基于双DSP的并联控制系统中串行通信的研究

SPI 部分发送和接受程序如下:

void spi_TxProcess()

{

while(SpiRegs.SPISTS.bit.BUFFULL_FLAG==1) {}

/*判断SPISTS.bit.BUFFULL_FLAG)是否为空*/

if(SpiRegs.SPISTS.bit.BUFFULL_FLAG==0)

{

SpiRegs.SPITXBUF=slave_value;

/*向SPITXBUF 写入数据以启动数据发送*/

}

}

interrupt void SPIRXINTA_ISR(void)

/*中断方式接受*/

{

TX_data2=SpiRegs.SPIRXBUF;

/*读取SpiRegs.SPIRXBUF 后自动清除中断标志位*/

return;

}

4 异步通信模块的设计

4.1 基于SCI 的硬件设计

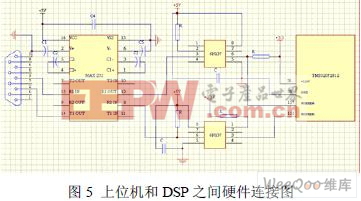

图 5 为上位机和DSP 的硬件连接图。RS-232C 标准采用负逻辑:逻辑“1”为-5V~-15V 之间的低电平,通常用-12V 表示;逻辑“0”为+5V~+15V 之间的高电平,通常用+12V 表示。 上述标准称为EIA 电平。

RS-232C 是用正负电压来表示逻辑状态,并且是负逻辑,而TTL 则以高低TTL 器件电平表示逻辑状态,且为正逻辑,两者的规定是不同的。为了能够将与EIA 器件连接,保证二者之间正常通信,必须在它们之间进行电平和逻辑关系的变换。本Maxim 公司生产的集 成芯片MAX232 来实现这一变换[4]。变化后的电平在经过6N137 转换为适合TMS320F2812 的电平在+3.3V 以内的信号。

4.2 SCI 通信的软件实现

通信前,发送端和接受端必须使用双方协商一致的通信协议,数据被拆分成为(bit)进行传送。传送的顺序一次为起始位、数据位、奇偶校验位、停止位。每秒钟传送的bit 数由波特率来决定。本文中的通信协议设定为:波特率38400bit/s,8 位数据位,无奇偶校验,1 位停止位,数据传输同时采用ASCⅡ码和二进制两种形式。

评论