一种高可靠性的计算机与FPGA串行通信的实现

MSComm是VB对使用串口通信的用户定制的控件,它提供了一系列标准通信属性和方法,简单编写相关程序便可实现串行端口的连接。主要用到的属性如表2所示。本文引用地址:https://www.eepw.com.cn/article/155412.htm

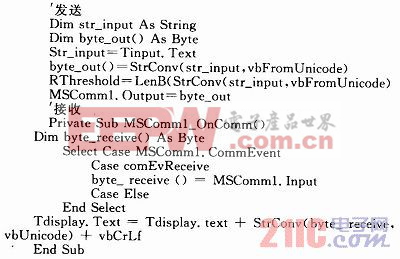

为验证FPGA与PC的通信,需要编写发送和接收程序,为简化程序,部分属性直接在注册表中设定。如InPutMode设定为1即二进制方式读取数据;由于程序接收部分使用OnComm事件,所以这里把SThreshold属性设定为1,而RThreshold属性设定为发送数据的字节数,即接收缓冲区接收到全部字节数后MSComm控件触发OnComm事件,执行相应的接收程序。InBufferSize和OutBufferSize均设置为1 024即1 KB缓冲空间。

如下是发送和接收子程序:

4 实验验证

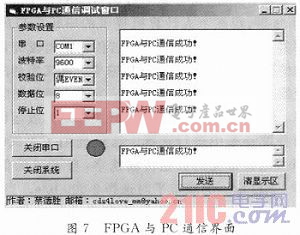

实验过程中串行数据的收、发等功能在Altera公司的CycloneⅡ系列EP2C5芯片下实现,在VB 6.0中编写相应的FPGA与PC通信的调试窗口,如图7所示为数据传输率9 600 b/s的实验结果。

打开应用程序,设置好通信端口、约定的通信速率、数据位等,在相应的输入框输入“FPGA与PC通信成功!”字符,点击5次发送,从显示区可以看到理想的结果,实验结果表明FPGA与PC通信可靠。

5 结语

本文实现了计算机与FPGA的串口通信,结合上位机的VB程序验证了通信的正确性。设计过程中FIFO部分运用了IP核使得程序更加简洁,且外加了一位拨码开关,实现了运行过程中两种波特率的灵活选择。实际运用中可以再相应地增加拨码开关实现多波特率多数据位等的互调,不必为了适应不同的通信标准而重新编写代码、重新配置。FPGA部分的程序在QuartusⅡ9.1环境下编辑、调试,综合结果显示共占用

FPGA的144个逻辑单元、81个专用逻辑寄存器、32位存储器和1个锁相环,相比百万门大规模FPGA占用资源很少,可以作为IP核灵活移植到其他工程中实现与PC的串行通信,为今后的设计开发提供参考。

评论