基于散列DMA的高速串口驱动设计

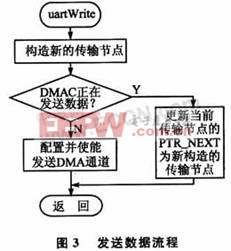

接收数据时,对方发过来的数据量一般是未知的。构造含有100个节点的循环链表结构,每个节点对应的传输块大小为接收FIFO Level。数据源地址为UART数据寄存器的地址,首节点的目的地址为接收数据内存区域的首地址,此后节点的目的地址每次向后偏移(FIFO Level×2)个字节,数据位宽为16(8个数据位,4个状态位,4个保留位)。当接收到的数据达到接收内存区域的80%(RECV_TH)时,需要通知数据发送方停止数据传输,在第80个节点处设置DMA中断,该节点为阈值节点。采用本文的设计方案接收1帧不超过RECV_TH大小的数据,最多产生一次RTI中断。当接收到的数据量少于FIFOLevel时不会触发DMA接收,在RTI中断中把UART接收FIFO中的数据复制到内存中的数据接收区,同时使DMA接收节点的目的地址向后偏移相应的长度并更新阈值节点的位置。接收数据流程如图4所示。如果采用DMA块传输方式,就必须额外使用一个环形数据缓冲区(Ring Buffer),每次接收到指定大小的数据块后产生DMA中断,在中断服务程序中将接收到的数据复制到环形数据缓冲区中。

3.3 驱动测试

本文的设计方案直接应用于工业级的HMI产品,必须经过严格的测试。利用3台西门子S7系列PLC和1台产品样机搭建令牌网,使用西门子MPI协议进行测试,并利用数据分析工具ProfiTrace监测通信过程。测试结果表明,2 400 bps~12 Mbps的各个波特率下都能进行稳定的数据通信。

结 语

本文详细介绍了DMA数据传输的特点和散列DMA的工作方式。在此基础上,提出了一套基于散列DMA的高速串口驱动设计方案,发送数据完全由DMAC完成,无需触发任何中断,接收1帧不超过接收区阈值的数据最多产生1次RTI中断。和现有的各种利用DMA块传输进行串口数据通信的方案相比,中断次数大幅减少,大大提高了数据传输的效率。在应用了本方案的人机界面产品上,实现了波特率高达12 Mbps的稳定数据传输。对于在其他平台上设计实现高速串口,本方案是一个很好的参考。

评论