数字电压表的VHDL设计与实现

介绍数字电压表的组成及工作原理,论述了基于VHDL语言和FPGA芯片的数字系统的设计思想和实现过程。

关键词:数字电压表;VHDL语言;FPGA

VHDL Realization of Digital Voltmeter

ZHAO Xiaobo, LIU Zhanwei, LI Sujuan

(Department of Computer, Shijiazhuang Railway Institute, Shijiazhuang050043, China)

Key words: digital voltmeter; VHDL; FPGA

在硬件电子电路设计领域中,电子设计自动化(EDA)工具已成为主要的设计手段,而VHDL语言则是EDA的关键技术之一,它采用自顶向下的设计方法,即从系统总体要求出发,自上至下地将设计任务分解为不同的功能模块,最后将各功能模块连接形成顶层模块,完成系统硬件的整体设计。本文用FPGA芯片和VHDL语言设计了一个数字电压表,举例说明了利用VHDL语言实现数字系统的过程。

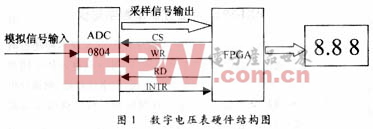

整个数字电压表的硬件结构如图1所示。

工作时,系统按一定的速率采集输入的模拟电压,经ADC0804转换为8位数字量,此8位数字量经FPGA处理得到模拟电压的数字码,再输入数码管获得被测电压的数字显示。

此电压表的测量范围:0~5V,三位数码管显示。

此电压表的测量范围:0~5V,三位数码管显示。

数字电压表的三大模块都是用VHDL语言编程实现的。

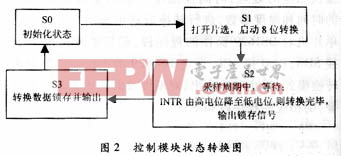

2.1控制模块

用状态机作法,产生ADC0804的片选信号、读/写控制信号,通过状态信号INTR判断转换是否结束;转换结束后将转换数据锁存并输出。其状态转换图如图2所示。

2.1控制模块

用状态机作法,产生ADC0804的片选信号、读/写控制信号,通过状态信号INTR判断转换是否结束;转换结束后将转换数据锁存并输出。其状态转换图如图2所示。

ADC0804是8位模数转换器,它的输出状态共有28=256种,如果输入信号Vin为0~5V电压范围,则每两个状态值为5/(256-1),约为0.0196V,故测量分辨率为0.02V。常用测量方法是:当读取到DB7~DB0转换值是XXH时,电压测量值为U≈XXH×0.02V;考虑到直接使用乘法计算对应的电压值将耗用大量的FPGA内部组件,本设计用查表命令来得到正确的电压值。

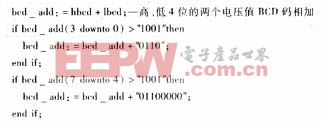

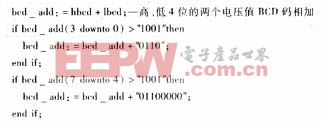

在读取到ADC0804的转换数据后,先用查表指令算出高、低4位的两个电压值,并分别用12位BCD码表示;接着设计12位的BCD码加法,如果每4位相加结果超过9需进行加6调整。这样得到模拟电压的BCD码。

本模块的功能仿真结果如图3所示;当转换数据为00010101,通过查表高4位0001是0.32V,而低4位0101是0.1V,最后的电压输出结果是0.32V+0.1V=0.42V,它的BCD码表示为000001000010,仿真结果正确。

2.3扫描、显示模块

如图4所示,CLK是扫描时钟,其频率为1kHz,由给定的40MHz时钟分频得到;DATAIN是数据处理模块输出的电压值的BCD码;SEL是数码管的片选信号;POINT是数码管小数点驱动;通过扫描分别输出3位电压值的BCD码DATAOUT,并通过DISP将BCD码译成相应的7段数码驱动值,送数码管显示。

在读取到ADC0804的转换数据后,先用查表指令算出高、低4位的两个电压值,并分别用12位BCD码表示;接着设计12位的BCD码加法,如果每4位相加结果超过9需进行加6调整。这样得到模拟电压的BCD码。

本模块的功能仿真结果如图3所示;当转换数据为00010101,通过查表高4位0001是0.32V,而低4位0101是0.1V,最后的电压输出结果是0.32V+0.1V=0.42V,它的BCD码表示为000001000010,仿真结果正确。

2.3扫描、显示模块

如图4所示,CLK是扫描时钟,其频率为1kHz,由给定的40MHz时钟分频得到;DATAIN是数据处理模块输出的电压值的BCD码;SEL是数码管的片选信号;POINT是数码管小数点驱动;通过扫描分别输出3位电压值的BCD码DATAOUT,并通过DISP将BCD码译成相应的7段数码驱动值,送数码管显示。

本文设计的VHDL语言程序已在MAXPLUSⅡ工具软件上进行了编译、仿真和调试,并通过编程器下载到了EP1K100QC208-3芯片。经过实验验证,本设计是正确的,其电压显示值误差没有超过量化台阶上限(0.02V)。本文给出的设计思想也适用于其他基于PLD芯片的系统设计。

评论