TURBO51嵌入式微处理器功能验证

TURBO51的FPGA 验证的前提是设计已经过了关键点的形式验证, 完成了块覆盖率为100% 的RTL仿真及代码检查且错误已收敛完毕, 故对FPGA验证的首要目的是通过运行和真实应用环境完全相同的完整目标应用系统验证两步的错误估计是否正确并配合其他SOC 模块作SOC 协同验证。因为对有的仿真做起来不方便的系统验证在FPGA 平台上很方便验证。在TURBO51的FPGA 验证中, 充分利用了FPGA 上的剩余资源, 用于实时定位与监测TURBO51的FPGA 实现版每个时钟的状态及其运行状态, 这其实已使原本认为FPGA 上难于定位错误的缺陷大为改观, 在真实环境下运行系统提供了非常接近RTL仿真的调试能力的观测窗口。这里依然首先选用了指令提交地址和指令取指地址,累加器, B 寄存器, 程序状态字PSW, 重定序缓冲状态, 例外处理标识, 写回总线,提交总线位为主要观察点, 显示每个时钟的状态, 将它们协同SOC 其它模块的输出, 示波器观测输出波形结果一起形成FPGA 验证结果。TURBO51在FPGA 验证时工作在60MH z, 除运行全部手工编写的用于模拟仿真的测试程序外, 还成功连续两百小时运行全部现有量产的基于RTOS商用系统及其极限条件, 没有发现严重错误。通过对寄存器值的实时监测发现十处以内的外设非致命错, 比如GPIO 与外设输入输出复用。

当然, 每改一次RTL或监视寄存器都需要重新进行FPGA 烧写文件的生成, TURBO51耗时近两小时, 故它仍然不可能取代仿真。完成FPGA 验证后做准备流片的工厂提供的工艺标准单元库综合及静态时序分析, 交出网表做后端布局布线, 完成后再用带门延时的后端门级网表进行门级仿真,最后编写样片基台测试程序。

6 验证结果分析

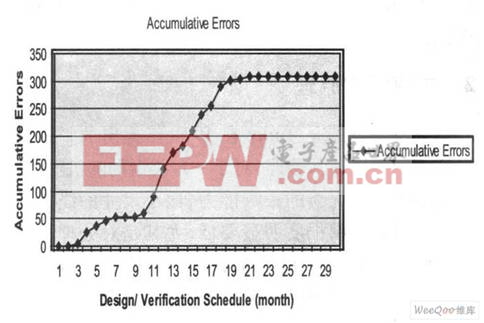

由于最初在制定实现的方法和制定验证计划时是同步进行的, 致使整个设计阶段的错误累积。在TURBO51的设计和验证中, 首先用形式验证将最高风险的存贮访问, 高速缓存, 分支预测, 动态执行, 例外处理中的最高风险组合进行完备证明,使错误得以排除。在此后的验证中, 凡经形式验证正确的部分再未出现过异常, 如图1所示。

图1 错误时间累计统计。

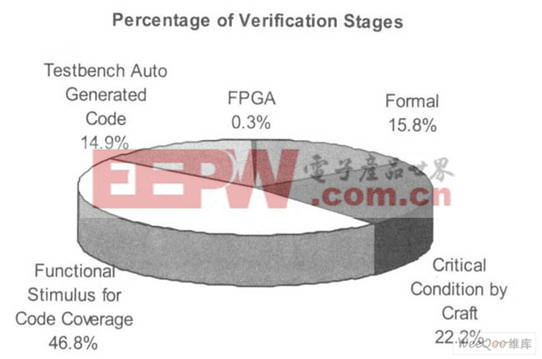

这样使得全部的高风险错误在RTL仿真的中期已经全部排除并且大多数都由手工编写的测试激励完成。由于8051指令集指令死角空间相对较小,手工编写可行。其中大部分RTL 仿真发现的错是IO设备错误与处理器指令执行部分无关。如图2所示, 错误99. 7% 百分比在FPGA 验证前已收敛,故可认定前面工作扎实有效。假如一个设计如果在FPGA 验证阶段错误还未能收敛完, 还能发现大量新增错误尤其是严重错误的话, 这说明仿真及行为模型描述与验证计划都存在严重问题,应退回去重走一遍, 否则流片风险较大。

图2 不同验证阶段发现的错误分布统计。

7 总结和未来工作

TURBO51嵌入式微处理器使用了上述多种验证方法使得越严重的错误得到了越早的收敛, 加上高的RTL代码覆盖率及长时间在FPGA 上成功运行了全部目标应用程序及所有仿真测试程序, 表明设计正确且兼容性完备, 使TURBO51嵌入式微处理器顺利采用富士通微电子(日本) 90nmCMOS 工艺一次流片成功。但另一方面, 可配置约束的自动随机指令序列已在更复杂的处理器验证中越来越广泛地采用, TURBO51的验证中在这一方面目前还处于初级阶段, 这将是以后的主要改进方向。

评论