基于CPLD的DSP与声卡的接口技术

从以上分析可以看出C2XX的DMA操作与PC机中的DMA操作的区别。在PC机中,CPU收到DMA请求信号后,迫使CPU在现行的总线周期结束后,使其地址、数据和部分控制引脚处于三态,从而让出总线的控制权,并给出一个DMA响应信号;在DMA操作完成后,DMA请求信号无效以后,CPU再恢复对系统总线的控制。而在C2XX中,DMA申请信号将引起C2XX中断,在中断程序中发出软件指令使C2XX各信号引脚处于三态,同时也给出了一个DMA响应信号;在DMA操作完成后,C2XX检测到DMA请求信号无效以后,虽然总线返回到正常状态,C2XX仍处在中断程序中。从以上分析可知,尽管中断需要保护断点和现场,使得C2XX的DMA的处理速度与PC机相比要低得多,但毕竟C2XX也实现了DMA操作,从而可借助DMA控制器8237实现对声卡的DMA操作访问[4]。

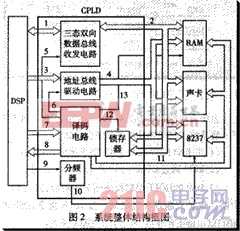

整个系统结构框图如图2所示。从图中可以看出,CPLD主要完成数据总线驱动、地址总线驱动、地址锁存器、译码和时钟分频等功能,其中译码电路是整个电路的核心。数据总线驱动电路和地址总线驱动将DSP的内部数据与地址总线与外围电路的数据和地址总线相互隔离;地址锁存器生成8237在DMA服务周期通过数据线DB0~D7输出的高8位地址A8~A15。时钟分频电路为外电路提供需要的各种频率的同步时钟。-译码电路为各单元电路以及外围电路提供读写信号、锁存信号、片选信号和使能信号。

图2中1为DSP内部系统总线,2为外部数据总线,3为DSP内部地址总线,4为外部地址总线,5为数据总线收发电路使能信号,6为地址总线驱动电路使能信号,7为DSP输出控制总线,8为CPLD译码后输人DSP的信号线,9为DSP同步外围电路的时钟,10为DMA输人时钟,11为RAM,8237和声卡的读写信号,12为锁存信号,13为RAM的片选信号。

3 EPM7128S内部译码电路的逻辑实现

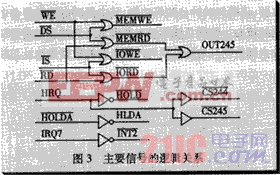

图3给出了EPM7128S内部译码电路主要的输入和输出信号以及它们的逻辑关系。其中DSP的地址选通信号和读写信号经译码分别得到IO读写信号和存储器读写信号;8237的DMA申请信号HRQ经反相后送到DSP的HOLD引脚以触发DSP中断,DSP在中断程序里发IDLE指令,HOLDA引脚变为低电子,响应DMA申请;同时数据总线和地址总线驱动电路的使能信号关闭,数据总线和地址总线为高阻态,从而8237可以接管总线,进行DMA操作。声卡的中断信号为高电子,须反相后再接DSP的中断引脚。

评论