基于DSP和CPLD的光纤陀螺信号采集系统设计

3 系统硬件结构

系统主要由DSP芯片TMS320F2812、双口RAMCY7C131,CPLD芯片EPM7128T1100、ADC芯片ADS8364以及传感器信号调理电路组成。

DSP主要负责与上位机通信,以及和CPLD共同控制AD实现对多路光纤陀螺数据的采集,这里选用TI公司生产的TMS320F2812。该芯片专门为控制系统应用而设计,它采用1.8 V的内核电压,具有3.3 V的外围接口电压,片内存储容量为18 KB SRAM,128 KB FLASH,最高主频150 MHz,片内集成有多种外设接口。

双口RAM主要输出数据采集指令并接收DSP传送的陀螺值。选用的双端口RAM型号为CY7C131,采用5 V供电,容量为1K×8 b,实际使用数据交换区为256×8 b。在256 B的存储空间内分为两个数据区,一个数据区(A)存放上位机下发的指令信息,另一个数据区(B)存放采集的陀螺数据信息。由于控制DSP与上位机对双口RAM的读写速度不同,为防止由于速度不匹配造成的读写冲突,在软件中相应的存储区设置读写标志位,通过此标志位来确定双端口RAM的读写状态。

在本系统中,CPLD是一个重要的组成部分,由CPLD组成的逻辑控制模块接收DSP传送过来的动作命令,控制AD某通道进行数据采集。这里选用Altera公司的EPM7128芯片。CPLD作为一个单独的控制执行结构,通过编写相应VHDL代码,即可生成相应的操作电路,实现对各种输入信号的锁存、判断和对控制信号的执行。

A/D转换芯片选用TI公司的高速、低功耗、六通道同步采样的16 b转换器ADS8364,可保证采样精度达到12位以上。芯片内部包含六个采样保持器,可保证六路信号同时采样;信号输入范围为0~5 V,最大转换速度250K,可以满足电位计、旋变信号采集速度和精度的要求。并且数字逻辑电平为3.3 V。考虑到数据采集处理系统的采样频率一般较高,如果用DSP直接控制ADS8364的访问,将占用DSP较多的资源,同时对DSP的实时性要求也较高。因此在本系统设计中,用CPLD实现ADS8364的接口控制电路。

陀螺模拟信号是-5~+5 V差分信号,通过信号调理,转化到0~5 V之间。当转速低的时候,因受系统影响信号上有毛刺,需要进行滤波,设计一个RC低通滤波电路去掉高频干扰即可。

4 系统软件流程

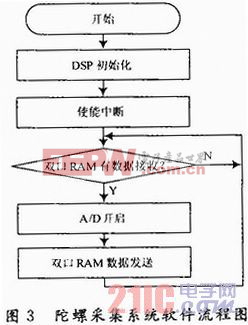

系统中DSP软件代码主要由两部分组成:与上位机通信和对陀螺信号的采集。软件开发在CCS3.1(Code Composer Studio)中进行。TMS 320F2812的主程序流程如图3所示。本文引用地址:https://www.eepw.com.cn/article/148954.htm

系统上电后,首先完成DSP中各个寄存器的初始化,包括配置RAM模块,设置定时器、中断等,然后系统进入循环等待状态。进入中断,首先对双口RAM进行查询,监测是否有采集指令下发,如果有,则启动A/D,然后把数据通过双口RAM传给上位机,否则返回循环等待状态。

评论