国产256核RISC-V处理器曝光,计划扩展到1600核!

随着每一代新一代芯片增加晶体管密度变得越来越困难,因此芯片制造商正在寻找其他方法来提高处理器的性能,其中包括架构创新、更大的芯片尺寸、多芯片设计,甚至晶圆级芯片,比如 Cerebras的WSE系列AI芯片。

近日,中国科学院计算技术研究所的科学家们也推出了一款先进基于RISC-V架构的 256 核多芯片,并计划将该设计扩展到 1,600 核,以创造整个晶圆大小的芯片,以作为一个计算设备。

据 The Next Platform报道,中国科学院计算技术研究所的科学家在《基础研究》杂志最近发表的一篇文章中介绍了一种先进的 256 核多芯片计算复合体,名为“浙江大芯片”。

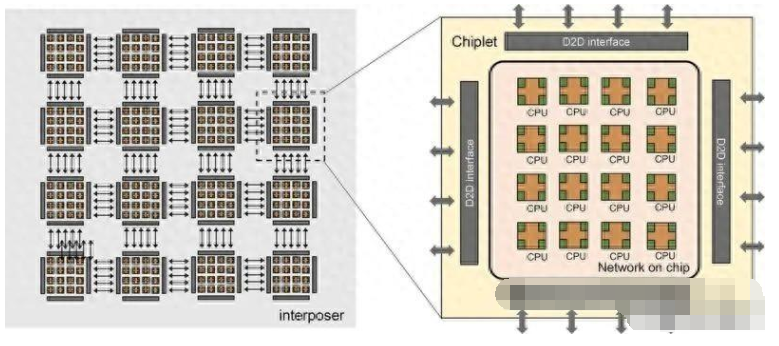

据介绍,该芯片设计由 16 个小芯片组成,每个小芯片包含 16 个 RISC-V 内核,并使用片上网络以传统的对称多处理器 (SMP) 方式相互连接,以便小芯片可以共享内存。每个小芯片都有多个芯片到芯片接口,可通过 2.5D 中介层连接到相邻的小芯片,研究人员表示,该设计可扩展到 100 个小芯片,或 1,600 个内核。

据报道,“浙江大芯片”基于Chiplet架构设计,采用 22 纳米级工艺技术制造,目前还不确定使用中介层互连并在 22 纳米生产节点上制造的 1,600 个核心组件会消耗多少功率。不过,由于延迟的减少,这将极大地优化其功耗和性能。

论文探讨了光刻和Chiplet技术的局限性,并讨论了这种新架构满足未来计算需求的潜力。研究人员指出,多芯片设计可用于构建百亿亿次超级计算机的处理器,AMD 和英特尔目前正在做这件事。

研究人员写道:“对于当前和未来的百亿亿次计算,我们预测分层chiplet架构将是一种强大而灵活的解决方案。” “分层chiplet架构被设计为具有多个内核和许多具有分层互连的小芯片。在chiplet内部,内核使用超低延迟互连进行通信,而小芯片之间则以受益于先进封装技术的低延迟互连,从而可以最大限度地减少这种高可扩展性系统中的小芯片延迟和NUMA效应”。

与此同时,研究人员建议对此类组件使用多级内存层次结构,这可能会给此类设备的编程带来困难。

“内存层次结构包含核心内存[缓存]、芯片内内存和芯片外内存,”描述中写道。“这三个级别的内存在内存带宽、延迟、功耗和成本方面有所不同。在分层chiplet架构的概述中,多个核心通过交叉交换机连接并共享缓存。这形成了pod结构,并且pod通过chiplet内网络互连,多个pod组成一个chiplet,chiplet通过chiplet间网络互连,然后连接到片外存储器,需要仔细设计才能充分利用这种层次结构合理利用内存带宽来平衡不同计算层次的工作量可以显着提高chiplet系统效率。正确设计通信网络资源可以保证chiplet协同执行共享内存任务。

大芯片设计还可以利用光电计算、近内存计算和 3D 堆栈内存等技术。然而,论文没有提供这些技术实施的具体细节,也没有解决它们在设计和构建此类复杂系统时可能带来的挑战。

编辑:芯智讯-浪客剑

*博客内容为网友个人发布,仅代表博主个人观点,如有侵权请联系工作人员删除。