1nm后的晶体管,imec将CFET纳入路线图

来源:半导体行业观察

但是对于4T cell设计和16nm 的金属间距,即使叉板变得太窄,也难以提供所需的性能。P. Schuddinck等人在2022年VLSI 论文中强调了这一挑战。这就是互补FET或CFET可以提供缓解的地方。因为在CFET架构中,n和pMOS 器件相互堆叠,从而进一步最大化有效沟道宽度。

Julien Ryckaert:“在CFET架构中,n型和pMOS 器件相互堆叠。堆叠从单元高度考虑中消除了np间距,允许进一步最大化有效沟道宽度,从而进一步最大化驱动电流。我们还可以使用由此产生的面积增益将轨道高度推至4T 及以下。”

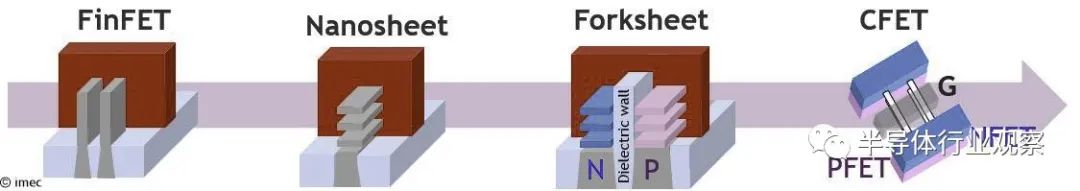

图1.从 FinFET 到 nanosheet 到 forksheet,最后到 CFET。

两种不同的实现方案:monolithic和 sequential

研究人员正在探索两种可能的集成方案,以实现具有挑战性的 nMOS-pMOS 垂直堆叠:单片(monolithic)与顺序(sequential)。

单片 CFET 流程从底部通道的外延生长开始,然后是中间牺牲层(sacrificial layer)的沉积,然后是顶部沟道的外延生长。Naoto Horiguchi表示:“虽然这似乎是构建 CFET 最直接的方法,但处理流程相当复杂。例如,堆叠方法产生了非常高的纵横比垂直结构,这为进一步图案化鳍、栅极、间隔物和源极/漏极触点带来了关键挑战。”

或者,可以使用由几个块组成的顺序制造流程来制造 CFET。

首先,底层设备被处理到contacts。接下来,使用晶圆对晶圆键合技术,通过晶圆转移在该层的顶部创建一个覆盖半导体层。然后,集成顶层器件,连接顶栅和底栅。Julien Ryckaert说:“从集成的角度来看,这个流程比单片流程更简单,因为底层和顶层设备都可以以传统的‘二维’方式单独处理。此外,它还提供了为 n 型和 p 型器件集成不同沟道材料的独特可能性。”

PPAC 基准测试:(优化的)顺序 CFET 是单片 CFET 的有效替代方案

在P. Schuddinck 等人在 2022 年发表的 VLSI 论文中,作者提出了 4T 标准单元设计中单片 CFET 与顺序 CFET 的 PPAC 评估 。

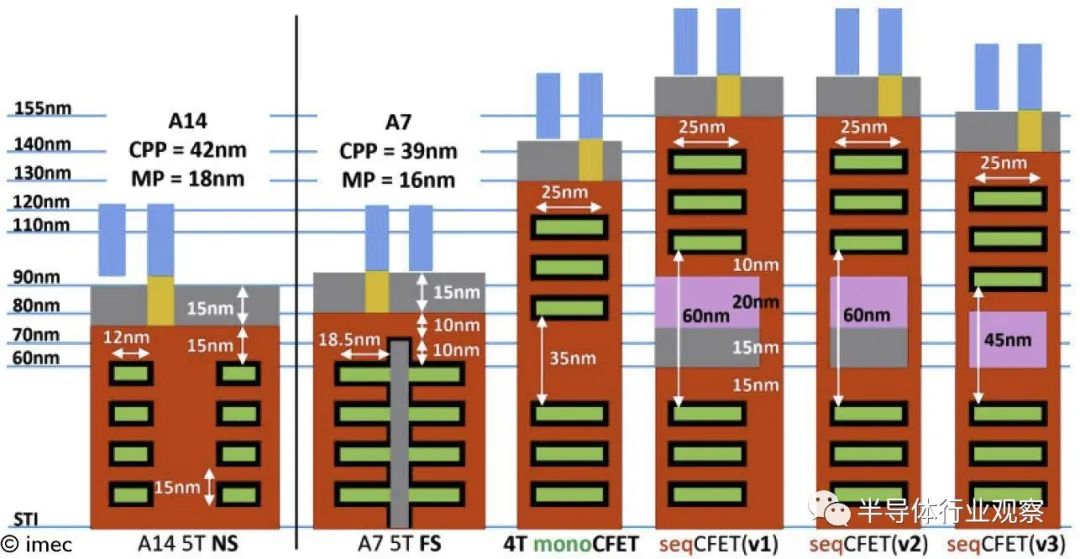

Julien Ryckaert说:“从这个基准来看,使用单片工艺流程制造的 CFET 消耗更少的面积,并且优于其有效电容增加的连续对应物。然而,我们表明,通过应用三个优化,我们可以将顺序 CFET 的轨迹与单片 CFET 的轨迹相提并论:(1)自对准栅极合并(图中的(v2)),(2)省略栅极cap (v3) 和 (3) 使用混合定向技术,称为 HOT。”

图2.nansoheet (NS)、forksheet (FS) 和 CFET(单片和顺序)的栅极横截面。基本顺序 CFET (=v1) 比单片设计更宽、更高。通过优化流程(包括自对准栅极合并 (v2) 和无栅极帽 (v3)),顺序 CFET 在面积消耗方面接近单片 CFET(也在 VLSI 2022 上介绍)。

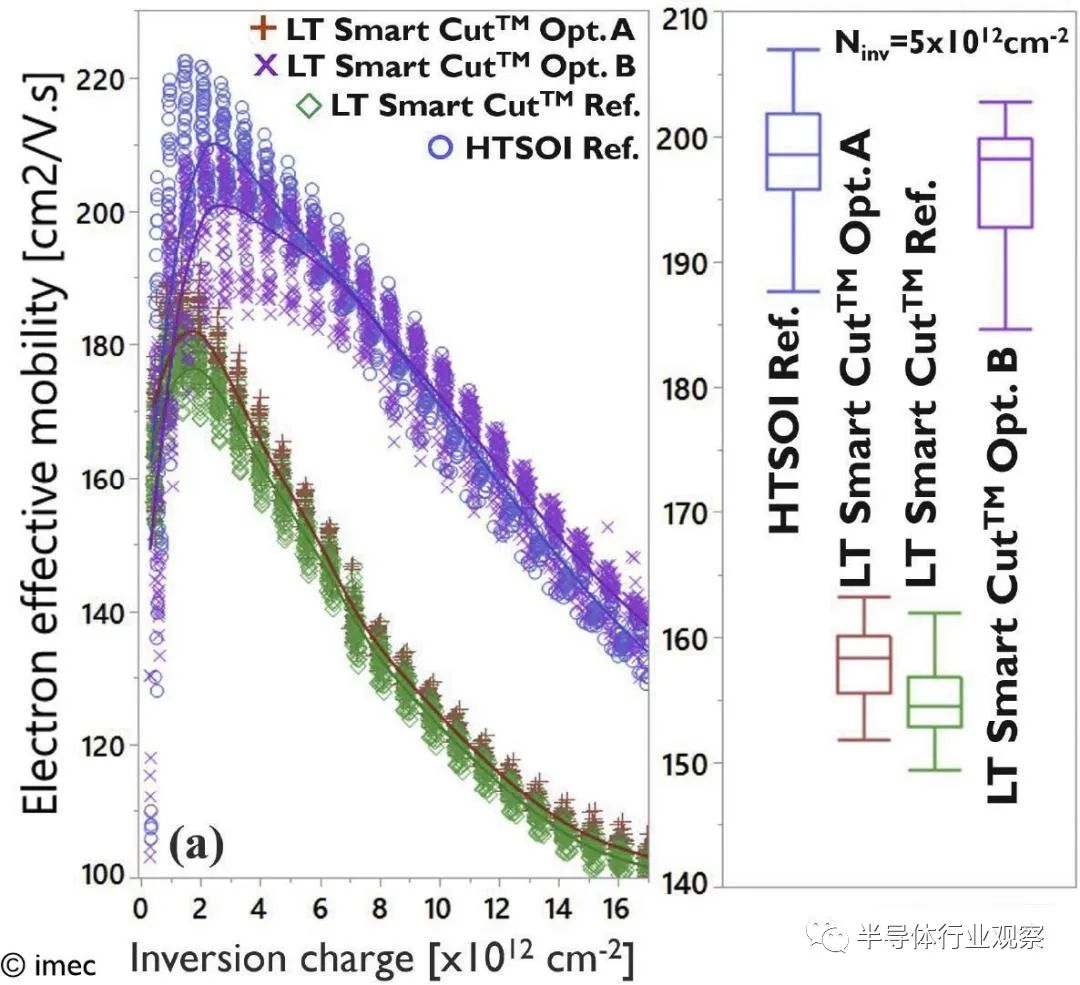

HOT 允许独立优化顶部和底部器件的晶体取向和应变工程,而不会增加工艺流程成本。例如,在 n-on-p 配置中,可以在顶部使用具有 <100> 取向的硅片,从而为顶部 nMOS 器件提供最高的电子迁移率。而对于底部,pMOS 空穴迁移率受益于 <110> 硅片取向。Julien Ryckaert:“尽管单片 CFET 仍然是首选,但顺序工艺流程的独特之处在于它可以利用晶圆方向的这种差异。

通过这些优化,我们的基准测试表明,对于未来 4T 轨道设计,顺序 CFET 流程可以成为更复杂的单片 CFET 的有效替代方案。”

逐步改进模块和集成步骤

近年来,imec 报告了在改进单片和顺序 CFET 的模块和集成步骤方面取得的进展。

例如,在 VLSI 2020 上,imec 率先展示了通过优化关键模块步骤实现的单片集成 CFET 架构 。

对于顺序 CFET,也报告了逐步改进。尽管底层和顶层器件可以以传统的“二维”方式分开处理,但晶圆转移带来了特定的挑战。例如,它对层转移和顶层设备处理都具有热预算限制(大约 500°C 或以下),以避免对底层设备产生任何负面影响。这是顶层器件的栅极堆叠可靠性的一个问题,它通常需要 900°C 量级的热步骤。

早些时候,imec 展示了保持良好栅极堆叠可靠性的新方法,其中包括对 pMOS 顶部器件进行低温氢等离子体处理。

优化的低温 Smart Cut TM层转移工艺——顺序 CFET 的关键构建模块

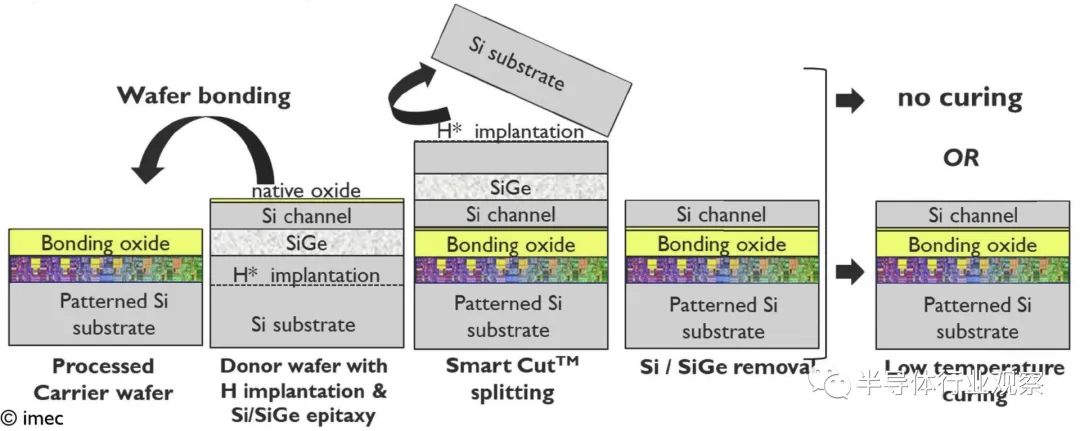

在 A. Vandooren 等人在 2022 年发表的 VLSI 论文中,imec 评估了三种不同的层转移过程 。在本文中,作者研究了各种工艺选项对顶部(完全耗尽的绝缘体上硅 (FD-SOI))和底部(体 FinFET)器件的器件性能的影响。

Naoto Horiguchi说:“从成本的角度来看,特别有前途的是 SOITEC 的低温 Smart Cut TM流程,它使用工程化的体施主晶圆来实现低温下的薄层分裂。这种方法的美妙之处在于它允许重复使用供体晶圆,使其成为一种具有成本效益的解决方案。其他两种方法都依赖于通过研磨和硅回蚀去除衬底,这不允许重新使用供体晶圆。”

图3.SOITEC 低温 Smart Cut TM层转移流程的描述,无固化或低温固化(也在 2022 VLSI 上展示)。

通过进一步优化,在使用低温 Smart Cut 进行概念验证层转移后处理的顶级器件显示可以从降低的电气性能中恢复。Naoto Horiguchi表示:“由于未经优化的低温固化,这些设备的电子迁移率较低。Soitec 进一步开发了其解决方案,表明我们可以通过优化低温固化步骤来恢复迁移率损失,从而提高 Si 通道的晶体质量。鉴于这种方法的成本效益,我们认为具有新开发工艺条件的 Smart Cut TM是在顺序 CFET 工艺流程中执行层转移的有效选择。

它提供了一个通用流程,支持 CFET 之外的 3D 顺序堆叠应用,例如 memory-on-logic 或 logic-on-logic 的 3D 顺序集成。”

图 4 - 低温 Smart Cut TM层转移方法的电子有效场迁移率与反转电荷,比较优化和参考(概念验证)工艺条件。该图显示了 Opt 改进的移动性。B(紫色),表示额外的低温固化步骤(也在 VLSI 2022 上介绍)。

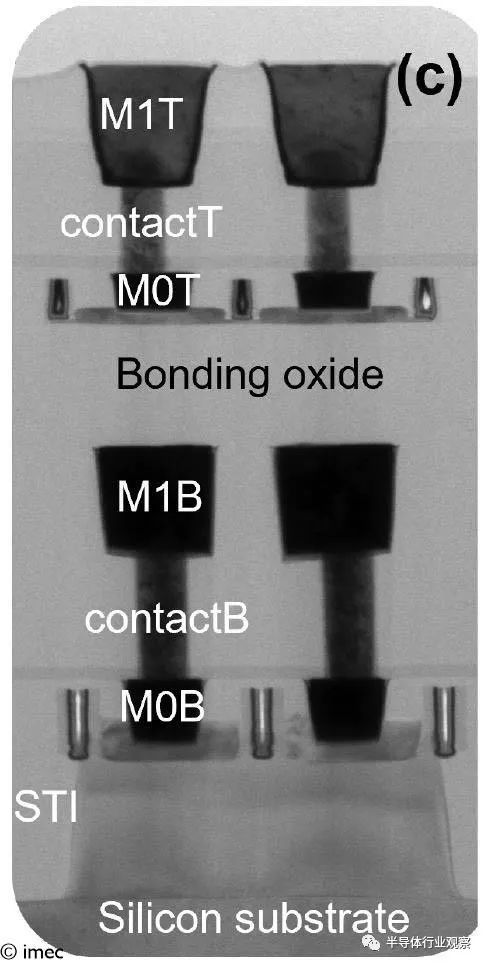

通过这些测试设备,作者还展示了顶部和底部设备之间良好的电气互连性,并通过功能逆变器链进行了验证。此外,如上所述,通过集成氢等离子体处理步骤,可以保持顶层 pMOS 器件的栅极堆叠可靠性。

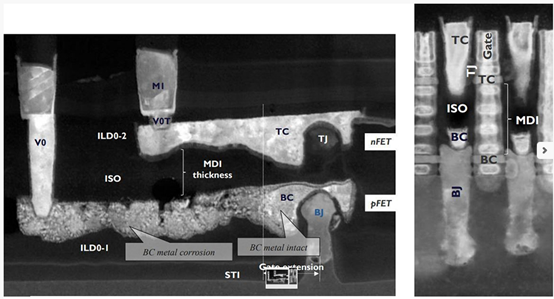

图5.3D 顺序堆叠器件的 TEM 横截面(也在 VLSI 2022 上展示)。

“我想强调的是,这种架构还不是真正的 CFET 实现,”Naoto Horiguchi 补充道。“例如,在设想的顺序 CFET 架构中,底部器件的金属互连层 (M1B) 不存在。A. Vandooren 的 VLSI 论文中展示了我们的测试工具,用于演示改进的层转移作为顺序 CFET 和其他 3D 顺序堆叠实现的关键模块。

未来,IMEC 表示,将继续努力优化集成步骤,最终将展示真正的顺序 CFET 实施。

*博客内容为网友个人发布,仅代表博主个人观点,如有侵权请联系工作人员删除。