针对Cortex―M3核的微控制器LM3S9B96,提出了一种基于μDMA的高速网络驱动程序的设计方案。在简要介绍LM3S9B96的以太网控制器、网络驱动程序的作用后,对该网络驱动程序设计的各个部分进行了详细描述,包括网络驱动初始化程序、数据包发送程序、数据包接收程序和中断处理程序等。

关键字:

μDMA 网络驱动程序 FIFO LM3S9B96

摘要分布式基站系统中,RRU 通常会通过光纤拉远实现与 BBU 的远程互联。由于光纤自身的特性,传输过程中必然会引入抖动和漂移;尤其是漂移,因其低频特性,并且难于滤除,在SERDES 的 FIFO 深度不够的情况下有可能会造

关键字:

SERDES FIFO 光纤 方案

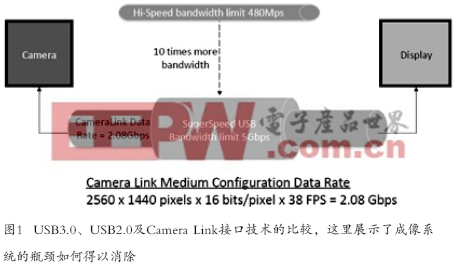

摘要 针对USB2.0在高速数据采集系统中带宽局限问题,设计了一款基于USB3.0总线的高速数据采集接口系统。通过对USB3.0的接口硬件系统、设备固件以及SLAVE FIFO与FPGA接口读写操作的设计,并经过实验测试,USB3.0硬

关键字:

FPGA USB3.0固件 SLAVE FIFO 数据通信

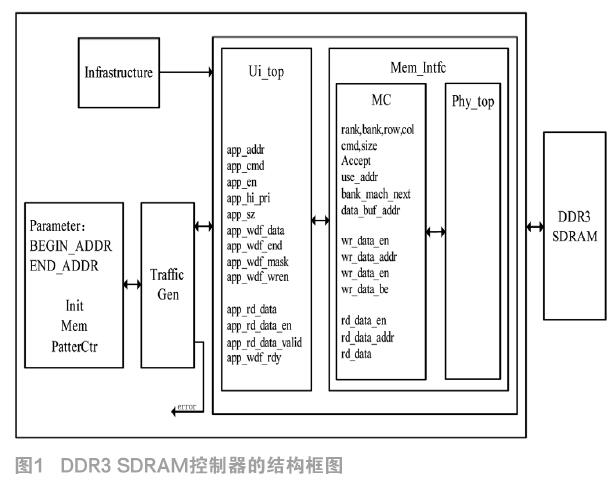

为了使DDR3 SDRAM更方便、多样地用于工程开发中,本文对XILINX公司DDR3 SDRAM提供的MIG核进行了分析研究,并在此基础上实现了大容量数据缓冲区的逻辑设计。通过对系统中各模块的作用及相互间关系的研究,发现该控制器256位接口对工程开发十分不便,通过创建FIFO控制系统和读写接口FIFO的方式,将接口转换为64位。该方案对控制核重新构建并上板测试,均符合高速数据传输缓存的要求,使DDR3成为一个大容量且可控的高速FIFO。

关键字:

MIG核 FIFO DDR3 SDRAM 201608

1 AD9225的结构

AD9225是ADI公司生产的单片、单电源供电、12位精度、25Msps高速模数转换器,片内集成高性能的采样保持放大器和参考电压源。AD9225采用带有误差校正逻辑的四级差分流水结构,以保证在25Msps采样率下获得精确的12位数据。除了最后一级,每一级都有一个低分辨率的闪速A/D与一个残差放大器(MDAC)相连。此放大器用来放大重建DAC的输出和下一级闪速A/D的输入差,每一级的最后一位作为冗余位,以校验数字误差,其结构如图1所示。

图

关键字:

ADC FIFO

高清图像质量已经快速成为现代家庭中多媒体产品的标准配置。在该领域之外的许多应用中,更高的分辨率、更好的对比度、更大的色深和更快的帧率也都越来越受欢迎,这些应用包括安保、医疗成像和工厂生产线检测系统等等。当然,尽管增强型成像技术在不久的将来更加流行似乎是板上钉钉的事情,但这将取决于支持更高数据传输能力的先进半导体技术的发展。本文将以实例阐述半导体技术所取得的进展。

虽然USB连接标准开始并没有引起太多关注,但从上世纪90年代中期第一次脱颖而出已经改变了很多,它现在已经远远不只是为低数据速率的鼠标和

关键字:

USB FIFO 缓冲器 FPGA 显示器

1 提高抽象层次

Vivado HLS能提高系统设计的抽象层次,为设计人员带来切实的帮助。Vivado HLS通过下面两种方法提高抽象层次:

● 使用C/C++作为编程语言,充分利用该语言中提供的高级结构;

● 提供更多数据原语,便于设计人员使用基础硬件构建块(位向量、队列等)。

与使用RTL相比,这两大特性有助于设计人员使用Vivado HLS更轻松地解决常见的协议系统设计难题。最终简化系统汇编,简化FIFO和存储器访问,实现控制流程的抽象。HLS的另一大优势是便于架构研究和

关键字:

Vivado FIFO 存储器 RAM C/C++

接上篇

4 设置简单系统

协议处理一般情况下属于状态事务。必须先顺序读取在多个时钟周期内进入总线的数据包字,然后根据数据包的某些字段决定进一步操作。通常应对这种处理的方法是使用状态机,对数据包进行迭代运算,完成必要的处理。例3是一种简单的状态机,用于根据上一级的输入丢弃或转发数据包。该函数接收三个参数:一个是通过“inData”流接收到的输入分组数据;一个是通过“validBuffer”流显示数据包是否有效的1位旗标;第三个是称为&ldquo

关键字:

Vivado FIFO 存储器 RAM C/C++

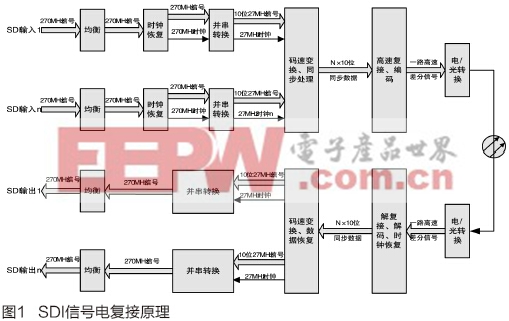

摘要:针对目前市场上越来越多针对SDI信号的应用需求,提出了多路SDI电信号单波长光纤传输的实现方案,就方案中出现的由于FIFO“写满”或“读空”引起的SDI信号传输误码,提出了一种基于FPGA内部PLL的可控时钟,利用该时钟作为FIFO的读时钟,实现SDI信号无损传输。

引言

串行数字接口(Serial Digital Interface,简写为SDI)是针对演播室环境提出的用单根电缆来传输数字视音频信号的方式。在SMTPE-259M标准中

关键字:

SDI FPGA 光纤 FIFO PLL 数据还原 201503

记得在上几篇博客中,有几名网友提出要加进去错误分析这一部分,那我们就从今天这篇文章开始加进去我在消化这段代码的过程中遇到的迷惑,与大家分享。

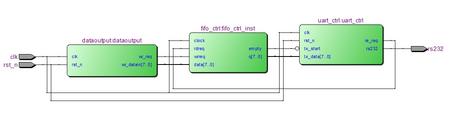

今天要写的是一段基于FIFO的串口发送机设计,之前也写过串口发送的电路,这次写的与上次的有几分类似。这段代码也是我看过别人写过的之后,消化一下再根据自己的理解写出来的,下面是我写这段代码的全部流程和思路,希望对刚开始接触的朋友来说有一点点的帮助,也希望有经验的朋友给予宝贵的建议。

首先来解释一下FIFO的含义,FIFO就是First Input Fi

关键字:

FPGA FIFO

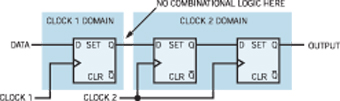

只有最初级的逻辑电路才使用单一的时钟。大多数与数据传输相关的应用都有与生俱来的挑战,即跨越多个时钟域的数据移动,例如磁盘控制器、CDROM/DVD 控制器、调制解调器、网卡以及网络处理器等。当信号从一个时钟域传送到另一个时钟域时,出现在新时钟域的信号是异步信号。

在现代 IC、ASIC 以及 FPGA 设计中,许多软件程序可以帮助工程师建立几百万门的电路,但这些程序都无法解决信号同步问题。设计者需要了解可靠的设计技巧,以减少电路在跨时钟域通信时的故障风险。

基础

从事多时钟设计的第一

关键字:

FPGA 异步信号 FIFO

引 言

RFID 技术是从 20 世纪 80 年代走向成熟的一项自动识别技术,近年来发展十分迅速。 目前,在全世界,基于 RFID 技术的电子标签,使用已经 非常广泛了,这主要取决于它的特性,RFID 标签可以使用在几乎所有的物理对象上。RFID 技术在 工业自动化,物体跟踪,交通运输控制管理,防伪校园卡,电子钱包,行李标签,收费系统,医用装 置,电子物品的监控和军事用途等方面已经得到了广泛的应用。例如第二代居民身份证,使用基于 ISO/IEC4443-B 标准的 13.56 MHz 电子标签,

关键字:

Microblaze RFID阅读器 FPGA FIFO

现代数字系统中,异步FIFO是一种被广泛应用于跨时钟域进行数据传输的有效方式。异步FIFO主要应用于两种不同时钟域的数据传输,这意味着数据的写入在一个时钟域,而数据的读出却在另一个时钟域,两个时钟完全异步[1]。现代通信系统中,特别是在移动通信系统中,人们对于节能型的产品提出了更高的要求。随着技术的发展,FPGA的技术、性能、稳定性等指标已经得到很大提高,同时FPGA厂商为不同的应用开发提供了各种IP核,大大减少了产品的开发周期,在各大FPGA厂商中,Xilinx的IP核应用比较广泛。但其IP核却没有

关键字:

FIFO FPGA

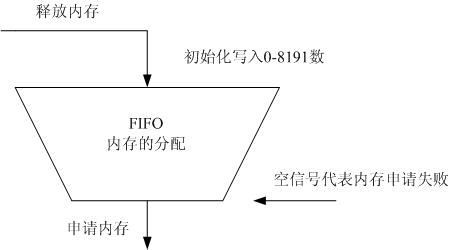

FIFO在FPGA设计中除了上篇所介绍的功能之外, 还有以下作为以下功能使用:

(1) 内存申请

在软件设计中,使用malloc()和free()等函数可以用于内存的申请和释放。特别是在有操作系统的环境下,可以保证系统的内存空间被动态的分配和使用,非常的方便。如果在FPGA内部实现此动态的内存分配和申请,相对来说较为复杂,例如某些需要外部数据存储且需动态改变的应用需求下,需要对FPGA外部DDR(或SRAM等)的存储空间,进行动态的分配和释放。通过使用FIFO作为内存分配器,虽然比不上软件

关键字:

FPGA FIFO SRAM

FIFO是FPGA内部一种常用的资源,可以通过FPGA厂家的的IP生成工具生成相应的FIFO。FIFO可分为同步FIFO和异步FIFO,其区别主要是,读写的时钟是否为同一时钟,如使用一个时钟则为同步FIFO,读写时钟分开则为异步FIFO。一般来说,较大的FIFO可以选择使用内部BLOCK RAM资源,而小的FIFO可以使用寄存器资源例化使用。

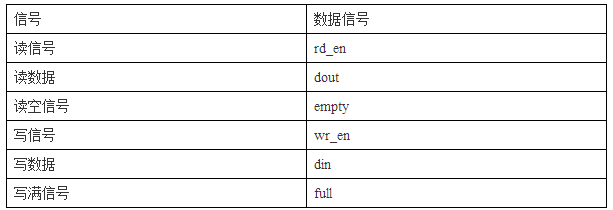

一般来说,FIFO的主要信号包括:

实际使用中,可编程满的信号(XILINX 的FIFO)较为常用,ALTERA的FIFO中,可以通过写深度(即写入

关键字:

FPGA FIFO RAM

fifo介绍

采用FIFO方式时,信息被以所收到的次序进行传输。

表示信息存储的一种数据结构,含义是先进入的对象先取出。队列(Queue )就是基于这种性质实现的。

FIFO( First In First Out)简单说就是指先进先出。由于微电子技术的飞速发展,新一代FIFO芯片容量越来越大,体积越来越小,价格越来越便宜。作为一种新型大规模集成电路,FIFO芯片以其灵活、方便、高效的特性,逐渐在高速数据采 [

查看详细 ]

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473