跨越鸿沟:同步世界中的异步信号

只有最初级的逻辑电路才使用单一的时钟。大多数与数据传输相关的应用都有与生俱来的挑战,即跨越多个时钟域的数据移动,例如磁盘控制器、CDROM/DVD 控制器、调制解调器、网卡以及网络处理器等。当信号从一个时钟域传送到另一个时钟域时,出现在新时钟域的信号是异步信号。

本文引用地址:http://www.eepw.com.cn/article/268638.htm在现代 IC、ASIC 以及 FPGA 设计中,许多软件程序可以帮助工程师建立几百万门的电路,但这些程序都无法解决信号同步问题。设计者需要了解可靠的设计技巧,以减少电路在跨时钟域通信时的故障风险。

基础

从事多时钟设计的第一步是要理解信号稳定性问题。当一个信号跨越某个时钟域时,对新时钟域的电路来说它就是一个异步信号。接收该信号的电路需要对其进行同步。同步可以防止第一级存储单元(触发器)的亚稳态在新的时钟域里传播蔓延。

亚稳态是指触发器无法在某个规定时间段内达到一个可确认的状态。当一个触发器进入亚稳态时,既无法预测该单元的输出电平,也无法预测何时输出才能稳定在某个正确的电平上。在这个稳定期间,触发器输出一些中间级电平,或者可能处于振荡状态,并且这种无用的输出电平可以沿信号通道上的各个触发器级联式传播下去。

对任何一种触发器,在时钟触发沿前后的一个小时间窗口内,输入信号必须稳定。这一时间窗口是多种因素的函数,包括触发器设计、实现技术、运行环境以及无缓冲输出上的负载等。输入信号陡峭的边沿可以将此窗口减至最小。随着时钟频率的升高,会出现更多有问题的时间窗口,而随着数据频率的提升,这种窗口的命中概率则会增加。

FPGA 制造商和 IC 晶片厂用“MTBF”来标识合格的触发器,并且确定它们的特性。“MTBF”(平均无故障时间)用统计方法描述了一个触发器的亚稳态特性,即确定某个触发器出现故障的概率。在计算 MTBF 时,制造商部分基于输入信号改变导致触发器不稳定期间的时间窗口长度。另外,MTBF 的计算还使用了输入信号的频率以及驱动触发器的时钟频率。

在一个 ASIC 或 FPGA 库中,每种触发器都有时序要求,以帮助你确定容易出问题的窗口。“建立时间”(Setup time)是指在时钟沿到来之前,触发器输入信号必须保持稳定的时间。“保持时间”(Hold time)则是指在时钟沿之后,信号必须保持稳定的时间。这些指标通常比较保守,以应对电源电压、工作温度、信号质量以及制造工艺等各种可能的差异。如果一个设计满足了这些时序要求,则触发器出现错误的可能性可以忽略不计。

现代 IC 与 FPGA 设计中使用的综合工具可以保证设计能满足每个数字电路触发器对建立与保持时间的要求。然而,异步信号却给软件提出了难题。对新的时钟域来说,从其它时钟域传来的信号是异步的。大多数综合工具在判定异步信号是否满足触发器时序要求时遇到了麻烦。因为它们不能确定触发器处于非稳态的时间,所以它们也就不能确定从一个触发器通过组合逻辑到达下一个触发器的总延迟时间。所以,最好的办法是使用一些电路来减轻异步信号的影响。

信号同步

信号同步的目的是防止新时钟域中第一级触发器的亚稳态信号对下级逻辑造成影响。简单的同步器由两个触发器串联而成,中间没有其它组合电路。这种设计可以保证后面的触发器获得前一个触发器输出时,前一个触发器已退出了亚稳态,并且输出已稳定。设计中要注意将两个触发器放得尽可能近,以确保两者间有最小的时滞(clock skew)。

IC 制造厂提供同步单元,帮助完成信号同步工作。这些单元通常包括一个有非常高增益的触发器,它比普通触发器耗电更高,也比较大。这种触发器降低了对输入信号建立-保持时间的要求,并且当输入信号导致亚稳态时,它可以防止出现振荡。另一种同步器单元包括两个触发器,省去了将两个单独触发器靠近放置的工作,也防止设计人员误在两个触发器间加入任何其它的组合逻辑。

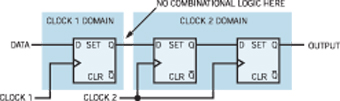

为了使同步工作能正常进行,从某个时钟域传来的信号应先通过原时钟域上的一个触发器,然后不经过两个时钟域间的任何组合逻辑,直接进入同步器的第一个触发器中(图 1)。这一要求非常重要,因为同步器的第一级触发器对组合逻辑所产生的毛刺非常敏感。如果一个足够长的信号毛刺正好满足建立-保持时间的要求,则同步器的第一级触发器会将其放行,给新时钟域的后续逻辑送出一个虚假的信号。

图1,在一个全同步器电路中,从某个时钟域传来的信号应先通过原时钟域上的一个触发器,然后不经过原触发器和同步器的第一个触发器两个时钟域间的任何组合逻辑,直接进入同步器的第一个触发器中。

一个经同步后的信号在两个时钟沿以后就成为新时钟域中的有效信号。信号的延迟是新时钟域中的一到两个时钟周期。一种粗略的估算方法是同步器电路在新时钟域中造成两个时钟周期的延迟,设计者需要考虑同步延迟将对跨时钟域的信号时序造成的影响。

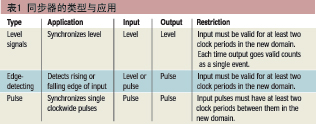

同步器有许多种设计方法,因为一种同步器不能满足所有应用的

需求。同步器的类型基本上有三种:电平、边沿检测和脉冲(表 1)。虽然还存在着其它类型的同步器,但这三种类型的同步器可以解决设计者遇到的多数应用问题。在电平同步器中,跨时钟域的信号在新时钟域中要保持高电平或低电平两个时钟周期以上。这种电路的要求是,在再次成为有效信号前,信号需要先变成无效状态。每一次信号有效时,接收逻辑都会把它看作一个单个事件,而不管信号的有效状态保持了多久。这种电路是所有同步器电路的核心。

表 1

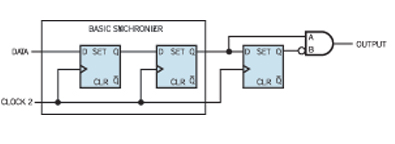

边沿检测同步器在电平同步器的输出端增加了一个触发器(图 2)。新增触发器的输出经反相后和电平同步器的输出进行与操作。这一电路会检测同步器输入的上升沿,产生一个与时钟周期等宽、高电平有效的脉冲。如果将与门的两个输入端交换使用,就可以构成一个检测输入信号下降沿的同步器。将与门改为与非门可以构建一个产生低电平有效脉冲的电路。

图2,边沿检测同步器在电平同步器的输出端增加了一个触发器。

当一个脉冲进入更快的时钟域中时,边沿检测同步器可以工作得很好。这一电路会产生一个脉冲,用来指示输入信号上升或下降沿。这种同步器有一个限制,即输入脉冲的宽度必须大于同步时钟周期与第一个同步触发器所需保

持时间之和。最保险的脉冲宽度是同步器时钟周期的两倍。如果输入是一个单时钟宽度脉冲进入一个较慢的时钟域,则这种同步器没有作用,在这种情况下,就要采用脉冲同步器。

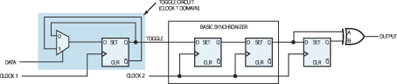

脉冲同步器的输入信号是一个单时钟宽度脉冲,它触发原时钟域中的一个翻转电路(图 3)。每当翻转电路接收到一个脉冲时,它就会在高、低电平间进行转换,然后通过电平同步器到达异或门的一个输入端,而另一个信号经一个时钟周期的延迟进入异或门的另一端,翻转电路每转换一次状态,这个同步器的输出端就产生一个单时钟宽度的脉冲。

图3,脉冲同步器的输入信号是一个单时钟宽度脉冲,它触发原时钟域中的一个翻转电路

脉冲同步器的基本功能是从某个时钟域取出一个单时钟宽度脉冲,然后在新的时钟域中建立另一个单时钟宽度的脉冲。脉冲同步器也有一个限制,即输入脉冲之间的最小间隔必须等于两个同步器时钟周期。如果输入脉冲相互过近,则新时钟域中的输出脉冲也紧密相邻,结果是输出脉冲宽度比一个时钟周期宽。当输入脉冲时钟周期大于两个同步器时钟周期时,这个问题更加严重。这种情况下,如果输入脉冲相邻太近,则同步器就不能检测到每个脉冲。

模拟信号相关文章:什么是模拟信号

电路相关文章:电路分析基础

脉冲点火器相关文章:脉冲点火器原理

评论