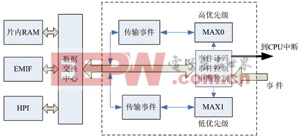

基于 DSP-dMAX 的嵌入式 FIFO 数据传输系统设计,本文介绍了基于C6727B的dMAX的基本结构以及基于dMAX的嵌入式FIFO软硬件设计,设置通用GPIO引脚作为中断,为了加快FIFO的传输速率,使用突发读写方式进行数据传输。嵌入式FIFO的实现,使得DSP和外部设备的通信更加方便和快捷,而且不需要CPU的参与,减轻了CPU的负担,CPU可以专注于复杂的算法处理。

关键字:

传输系统 设计 数据 FIFO DSP-dMAX 嵌入式 基于

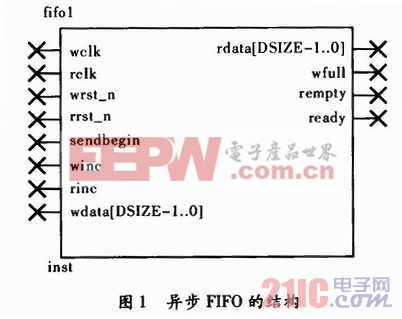

摘要 利用异步FIFO实现FPGA与DSP进行数据通信的方案。FPGA在写时钟的控制下将数据写入FIFO,再与DSP进行握手后,DSP通过EMIFA接口将数据读入。文中给出了异步FIFO的实现代码和FPGA与DSP的硬件连接电路。经验证,利用

关键字:

通信 运用 DSP FPGA FIFO 异步

摘要:以Altera公司的FPGA芯片EP2C20Q208C8为例,详细介绍了在QuartusII 7.2的环境下,用SOPC Builder构建Nios软核时,自定义FIFO接口元件的方法。通过将采集到的电压信号,在数码管上显示的实验,实现FIFO寄存器与

关键字:

SOPC FIFO 自定义 外设

声发射技术是光纤传感技术和声发射技术相结合的产物,是目前声发射技术的发展趋势。它将高灵敏度声发射传感器安装于受力构件表面以形成一定数目的传感器阵列,实时接收和采集来自于材料缺陷的声发射信号,进而通

关键字:

数据传输 存储 信号 发射 fifo 存储器 基于

1 FIFO概述

关键字:

V3680 FIFO 3680 72V

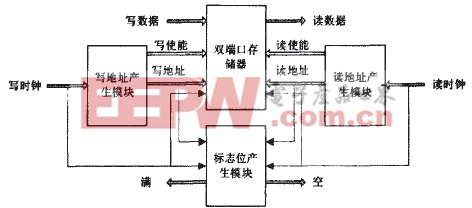

FIFO芯片IDT72V3680的功能特点及应用,1 FIFO概述 FIFO芯片是一种具有存储功能的高速逻辑芯片,可在高速数字系统中用作数据缓存。FIFO通常利用双口RAM和读写地址产生模块来实现其功能。FIFO的接口信号包括异步写时钟(wr-clk)和读时钟(rd-clk)、与

关键字:

特点 应用 功能 IDT72V3680 芯片 FIFO

在高频超声波数据采集系统中,很多高速A/D转换器往往不能直接与处理器相连接,这时就需要使用FIFO在处理器...

关键字:

FIFO 超声测厚 ARM

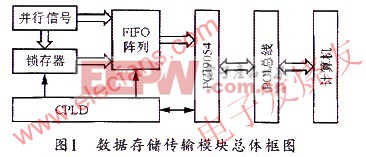

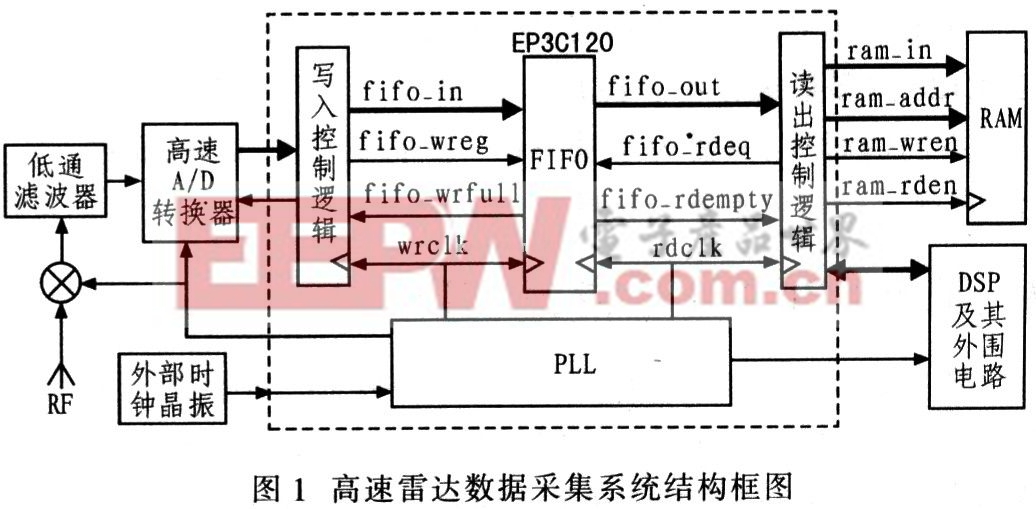

FPGA设计的高速FIFO电路技术,本文主要介绍高速FIFO电路在数据采集系统中的应用,相关电路主要有高速A/D转换器、FPGA、SDRAM存储器等。图1为本方案的结构框图。在大容量高速采集系统项目的开发过程中,FPGA作为可编程逻辑器件,设计灵活、可操作性

关键字:

电路 技术 FIFO 高速 设计 FPGA

在基于ARM的超声波测厚系统中,ARM处理器的数据接收能力往往与A/D芯片的工作速率不匹配,为避免有效数据丢失,提高系统工作效率,用FIFO作为高速A/D与ARM处理器之间的中转接口会得到很好的效果。这里以FIFO存储器CY7C4261作为中转器件实现了A/D芯片AD9283与ARM处理器S3C2410的接口设计,并叙述了数据从A/D芯片到ARM的整个数据采集过程。该接口电路用FIFO实现了超声测厚系统中A/D与ARM之间的无缝连接,提高了系统测厚精度。它的电路简单,调试方便,具有较高的应用价值。 关键字:

FIFO ARM 系统 接口设计

给出异步FIFO电路在高速数据采集系统中的应用,由FPGA生成独立时钟域的FIFO缓存器,采用FIFO的可编程设置参数启动数据传输,根据读写时钟频率异同的传输要求和FIFO的特性,采用一套控制电路,解决了可变速率数据缓存和固定时钟传输的问题。

关键字:

FIFO FPGA 时钟 201004

高速异步FIFO的设计与实现,引言 现代集成电路芯片中,随着设计规模的不断扩大.一个系统中往往含有数个时钟。多时钟带来的一个问题就是,如何设计异步时钟之间的接口电路。异步FIFO(First In First Out)是解决这个问题的一种简便、快捷的解

关键字:

实现 设计 FIFO 异步 高速

异步FIFO和PLL在高速雷达数据采集系统中的应用,将异步FIFO和锁相环应用到高速雷达数据采集系统中用来缓存A/D转换的高速采样数据,解决嵌入式实时数据采集系统中,高速采集数据量大,而处理器处理速度有限的矛盾,提高系统的可靠性。根据FPGA内部资源的特点,将FIFO和锁相环设计在一块芯片上。因为未使用外挂FIFO和PLL器件,使得板卡设计结构简单,并减少硬件板卡的干扰。由于锁相环的使用,使得整个采集系统时钟管理方便。异步FIFO构成的高速缓存具有一定通用性,方便系统进行升级维护。

关键字:

数据采集 系统 应用 雷达 高速 FIFO PLL 异步

fifo介绍

采用FIFO方式时,信息被以所收到的次序进行传输。

表示信息存储的一种数据结构,含义是先进入的对象先取出。队列(Queue )就是基于这种性质实现的。

FIFO( First In First Out)简单说就是指先进先出。由于微电子技术的飞速发展,新一代FIFO芯片容量越来越大,体积越来越小,价格越来越便宜。作为一种新型大规模集成电路,FIFO芯片以其灵活、方便、高效的特性,逐渐在高速数据采 [

查看详细 ]

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473