- 工业物联网(IIoT)互连性解决方案提供商RTI公司近日宣布,聘任新一代微创心脏泵开发商Puzzle Medical Devices公司首席执行官Stuart Kozlick为RTI咨询委员会的最新成员,为RTI公司医疗行业市场运营提供咨询顾问。Stuart Kozlick将以其丰富的行业专业经验,帮助RTI公司捕捉战略发展机遇,扩大在IIoT行业的影响力。作为一名经验丰富的高管,Stuart Kozlick在医疗设备开发、创新和研究方面拥有超过17年的经验,能够非常好地胜任其在RTI公司咨询委员会的职务

- 关键字:

IIoT DDS

- 频率合成技术起源于二十世纪30年代,当时所采用的频率合成方法是直接频率合成。它是利用混频、倍频、分频的方法由参考源频率经过加、减、乘、除

- 关键字:

DDS 杂散分析 方法

- 摘要 光伏汇流箱是光伏发电的重要组成部分,主要用于太阳能光伏组件与直流控制柜间的连接。文中设计的光伏汇流箱主电路以单片机STC12C5A60S2为控制核心,由电流检测电路、温度检测电路、通信电路和电源电路等组成,主

- 关键字:

DDS AD9852 传感器 电源

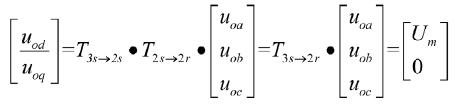

- 系统采用三相半桥拓扑,以STM32F407ZET6单片机为主从控制器,主控制器在dq坐标下进行控制实现三相稳压输出,从控制器采用主从均流控制实现两台三相逆变器的电流分配,采用三相同步锁相环(SRP-PLL)。逆变器单独工作时,输出交流母线电压为24.01 V,频率为49.99 Hz,总谐波畸变率为1.63%,系统整体效率为92.33%,负载调整率为0.12%。逆变器并联工作时,系统实现了两台逆变器输出功率比可调,输出线电流折算值误差最大值为0.06 A,并联工作负载调整率为0.21%。此外,系统具有友好的

- 关键字:

三相逆变器 主从均流 SPF-PLL 201809

- PLL(Phase Locked Loop): 为锁相回路或锁相环,用来统一整合时脉讯号,使内存能正确的存取资料。PLL用于振荡器中的反馈技术。锁相环通常由鉴相器(PD)、

- 关键字:

PLL 振荡器 DCDC

- 功率分析仪在测试时出现的数据跳动、效率异常等现象,很多时候与信号的频率是否准确测量有着很大的关系,本文就对频率测量的重要性进行分析,希望能帮助大家进行更准确的测量。 首先我们来看看为什么频率的测量对其他参数会造成如此大的影响。 同步源的选择 用过功率分析仪的工程师一定会记得,在对仪器进行设置的时候,一个叫“同步源”的设置选项,该选项包括了各个测试通道的电压和电流,工程师可以自主来进行选择。该选项的选择对直流信号测试影响不大,但对交流信号的测试会有很大的影响。原因是因为如果交流信号测量数据的间隔如

- 关键字:

PLL 频率

- 1 频综布局 单频综布局。通常采取如图形状进行布局:左臂支为参考频率源及锁相环控制电路,右臂支为压控制振荡器(VCO)输出隔离放大电路。中部环状为锁相环(PLL) 乒乓切换式频综布局,又叫音叉式布局:音叉的两臂为对称两个 PLL 频综,臂交汇点为开关切换装置。公共臂为切换后输出放大两路。 多通道收发接收机或者发射机本振电平分配电路布局:对称树状布局。 2 混频器(MIXER)电路布局 混频电路又称上下变频电路,是发射机和超外差式接收机的重要组成部分,是一种典型的频谱搬移电路。对于接收机来讲,

- 关键字:

射频,PLL

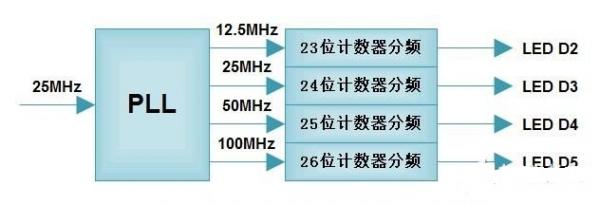

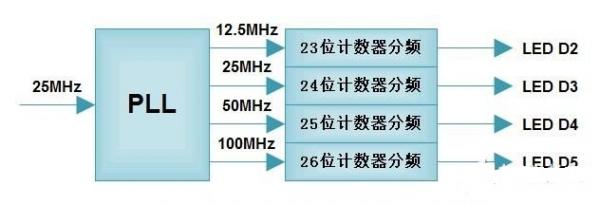

- 如图8.17所示,本实例将用到FPGA内部的PLL资源,输入FPGA引脚上的25MHz时钟,配置PLL使其输出4路分别为12.5MHz、25MHz、50MHz和100MHz的时钟信号,这4路时钟信号又分别驱动4个不同位宽的计数器不停的计数工作,这些计数器的最高位最终输出用于控制4个不同的LED亮灭。由于这4个时钟频率都有一定的倍数关系,所以我们也很容易通过调整合理的计数器位宽,达到4个LED闪烁一致的控制。

cy4.v模块代码解析 先来看cy4.v模块的

- 关键字:

FPGA PLL

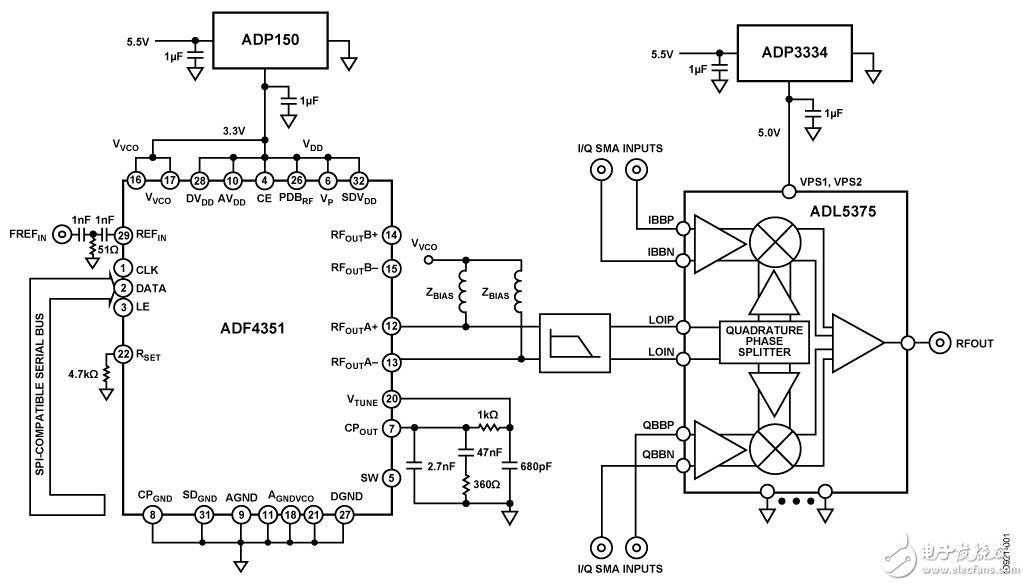

- 宽带低误差矢量幅度(EVM)直接变频发射机原理图-本电路为宽带直接变频发射机模拟部分的完整实现方案(模拟基带输入、RF输出)。通过使用锁相环(PLL)和宽带集成电压控制振荡器(VCO),本电路支持500 MHz至4.4 GHz范围内的RF频率。对来自PLL本振(LO)进行谐波滤波,确保提供出色的正交精度、边带抑制和低EVM。

- 关键字:

VCO PLL ADI 变频发射机

- 利用可编程振荡器增强FPGA应用-可编程时钟振荡器用作FPGA系统的时序参考,可提供一系列优势。其中首要优势是为了实现时钟树优化而进行高分辨率频率选择时所带来的设计灵活性,另一个巨大优势是具有可以减少电磁干扰(EMI)的扩频调制功能。

- 关键字:

DLL PLL FPGA

- 基于单片机与FPGA的直接频率数字合成器的设计方案-本文提出了一种基于单片机的直接频率数字合成器的设计方案。方案采用单片机控制FPGA产生DDS信号输出频率范围为20Hz~20KHz,幅度为0.3V~5V,两路正交信号能够实现0o~359o的相位差,并通过MAX+plusII软件进行仿真验证。仿真结果表明,本方案可达到预定要求,具有较强的实用性。

- 关键字:

频率合成器 DDS

- PLL和DLL:都是锁相环,区别在哪里?-一般在altera公司的产品上出现PLL的多,而xilinux公司的产品则更多的是DLL,开始本人也以为是两个公司的不同说法而已,后来在论坛上见到有人在问两者的不同,细看下,原来真是两个不一样的家伙。

- 关键字:

锁相环 DLL PLL

- PLL锁相环的特性、应用与其基本工作过程-PLL(Phase Locked Loop),也称为锁相环路(PLL)或锁相环,它能使受控振荡器的频率和相位均与输入参考信号保持同步,称为相位锁定,简称锁相。

- 关键字:

pll 锁相环

- PLL锁相环的基本结构及工作原理-PLL(Phase Locked Loop): 为锁相回路或锁相环,用来统一整合时脉讯号,使高频器件正常工作,如内存的存取资料等。PLL用于振荡器中的反馈技术。 许多电子设备要正常工作,通常需要外部的输入信号与内部的振荡信号同步。

- 关键字:

pll 锁相环

- 制作一个基于STC15W4K48S4设计手机控制AD9850信号发生器的设计方案-任何发射机或接收机都需要一个源。这个源可以是RC振荡器、LC振荡器、晶体振荡器、锁相环频率合成器或DDS直接数字频率合成器。而DDS直接数字频率合成器是近10几年的新兴方案。纵观各种DDS芯片,数美国ADI公司的AD9850性价比最高。市面上满天飞的一款DDS信号发生器就是采用此款芯片。出于成本和占有量的考虑,决定率先开发配套此款DDS信号发生器的控制板。本控制板硬件使用最新版STC的51系列单片机STC15W4K48S4。

- 关键字:

dds ad9850 振荡器

dds-pll介绍

您好,目前还没有人创建词条dds-pll!

欢迎您创建该词条,阐述对dds-pll的理解,并与今后在此搜索dds-pll的朋友们分享。

创建词条

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473