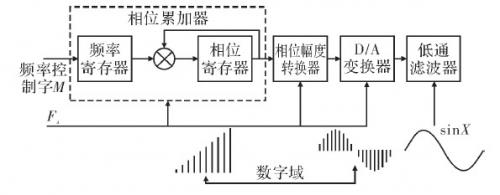

介绍了直接数字频率合成(DDS)的结构和原理,并将DDS技术应用于短波射频通信频率源中。实现了一种基于单片机+DDS可编程低噪声频率源,输出信号范围46.5~75 MHz.实验结果表明,该频率源具有频率分辨率高、相位噪声低等优点,满足短波射频通信系统对频率源的设计要求。

频率源是现代短波射频通信系统的核心,对整个系统的正常运行起着决定性的作用。作为射频电路与系统的核心设备,频率源的好坏关系着整个系统的稳定性。现在的频率合成技术正朝着杂散和相位噪声更低的方向发展,同时还要求有更宽的频带和更高的频率

关键字:

DDS 射频

摘要:

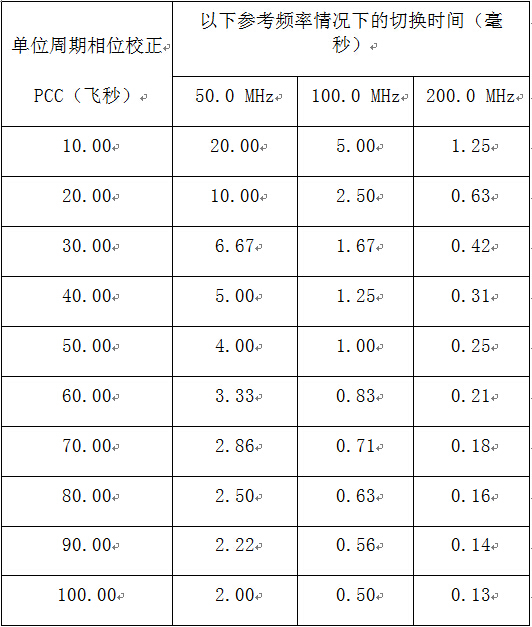

检测到时钟丢失时平滑切换到冗余时钟源有助于避免系统运行中断。

正文:

当今许多数据通信、网络和计算机系统都需要实现时钟冗余。组件或板级故障甚至简单的定期系统维护等引起的任何中断都不应造成系统运行中断。因此,为整个电路工作提供时序的系统时钟必须避免因任何异常情况而中断。带冗余的理想时钟发生器也必须能在检测到时钟错误或丢失的情况下从母时钟源平滑切换到子时钟源或晶振。

以下给出几类常用的冗余时钟方案,其中包括:

动态时钟切换:根据这种方案,系统在检测到母时钟源丢失或错误

关键字:

VCO PLL

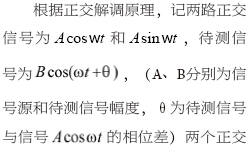

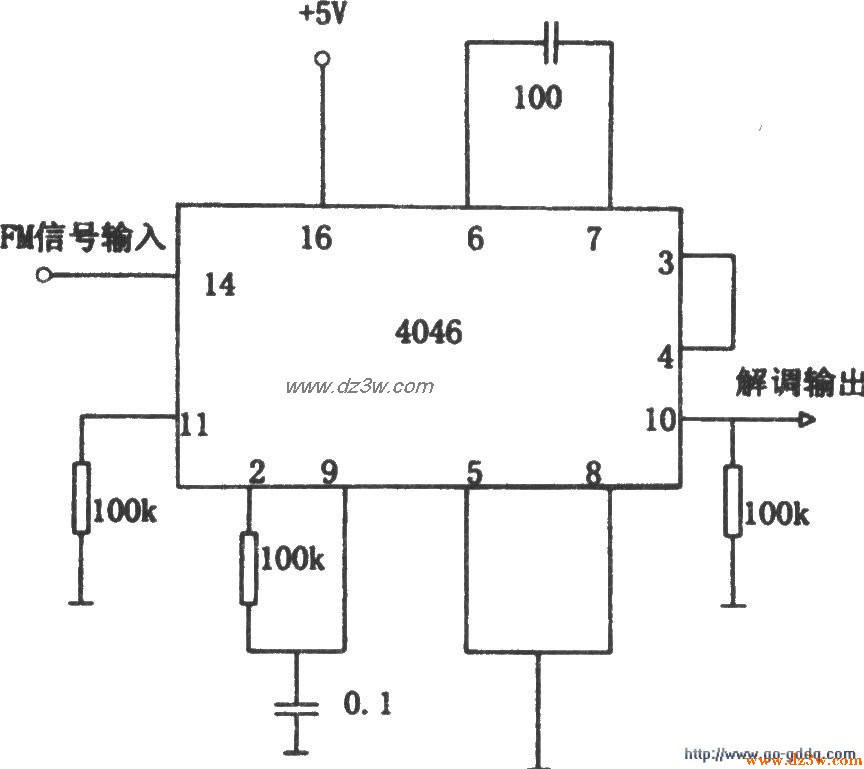

摘要:基于零中频正交解调原理的频率特性测试仪,用于检测被测网络的幅频特性和相频特性。系统采用集成数字直接频率合成器AD9854产生双路恒幅正交余弦信号,作为扫频信号源,以FPGA为控制核心和运算平台,结合滤波器、放大器、混频器及ADC电路,实现对双端口网络在1-40MHz频率范围内频率特性的点频和扫频测量,并在LCD屏上实时显示相频特性曲线和幅频特性曲线。

引言

AD9854数字合成器是高度集成的器件,它采用先进的DDS技术,片内整合了两路高速、高性能正交D/A转换器,在高稳定度时钟的驱动

关键字:

AD9854 FPGA 滤波器 DDS ADC 201504

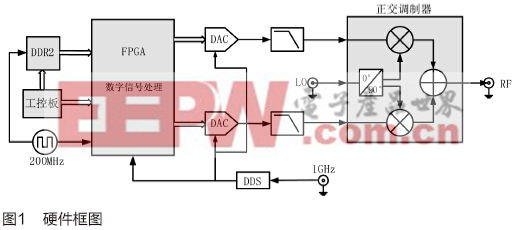

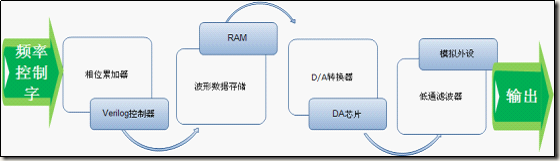

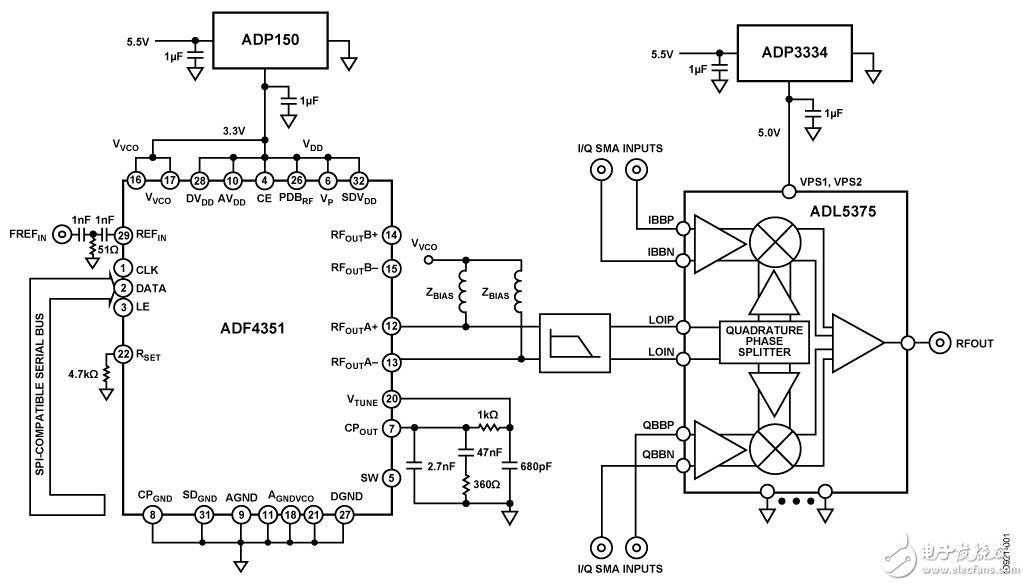

摘要:随着通信行业以及数字技术的不断发展,市场上经常需要多模通信信号或多制式数字调制信号发生器,本文介绍了采用软件无线电思想,基于“DDR2+FPGA+DAC+DDS+宽带调制器”的硬件结构的信号发生装置,实现了TD-SCDMA、WCDMA、TD-LTE、FDD-LTE等多模信号以及BPSK、QPSK、OQPSK、DQPSK、8PSK、16QAM、32QAM、64QAM、2FSK、4FSK、GMSK等数字调制信号的发生,能很好满足现代信号模拟的实际需求。

1 引言

关键字:

多模 调制信号 FPGA DDS FIR滤波器 201504

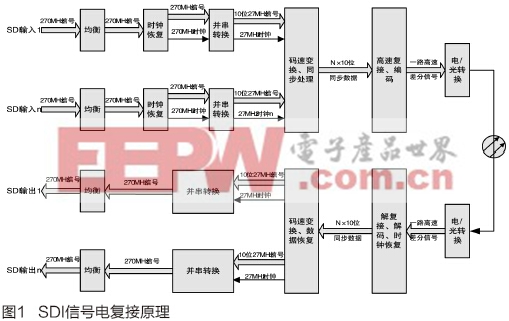

摘要:针对目前市场上越来越多针对SDI信号的应用需求,提出了多路SDI电信号单波长光纤传输的实现方案,就方案中出现的由于FIFO“写满”或“读空”引起的SDI信号传输误码,提出了一种基于FPGA内部PLL的可控时钟,利用该时钟作为FIFO的读时钟,实现SDI信号无损传输。

引言

串行数字接口(Serial Digital Interface,简写为SDI)是针对演播室环境提出的用单根电缆来传输数字视音频信号的方式。在SMTPE-259M标准中

关键字:

SDI FPGA 光纤 FIFO PLL 数据还原 201503

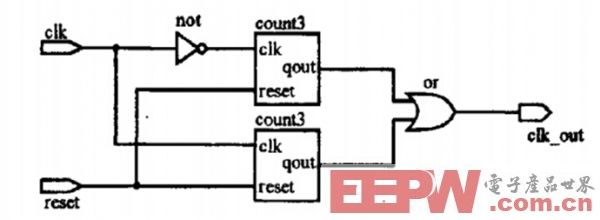

一、为啥要说任意分频

也许FPGA中的第一个实验应该是分频实验,而不是流水灯,或者LCD1602的"Hello World"显示,因为分频的思想在FPGA中极为重要。当初安排流水灯,只是为了能让大家看到效果,来激发您的兴趣(MCU的学习也是如此)。

在大部分的教科书中,都会提到如何分频,包括奇数分频,偶数分频,小数分频等。有些教科书中也会讲到任意分频(半分频,任意分数分频)原理,用的是相位与的电路,并不能办到50%的占空比,也不是很灵活。

但没有一本教科书会讲到精

关键字:

FPGA DDS

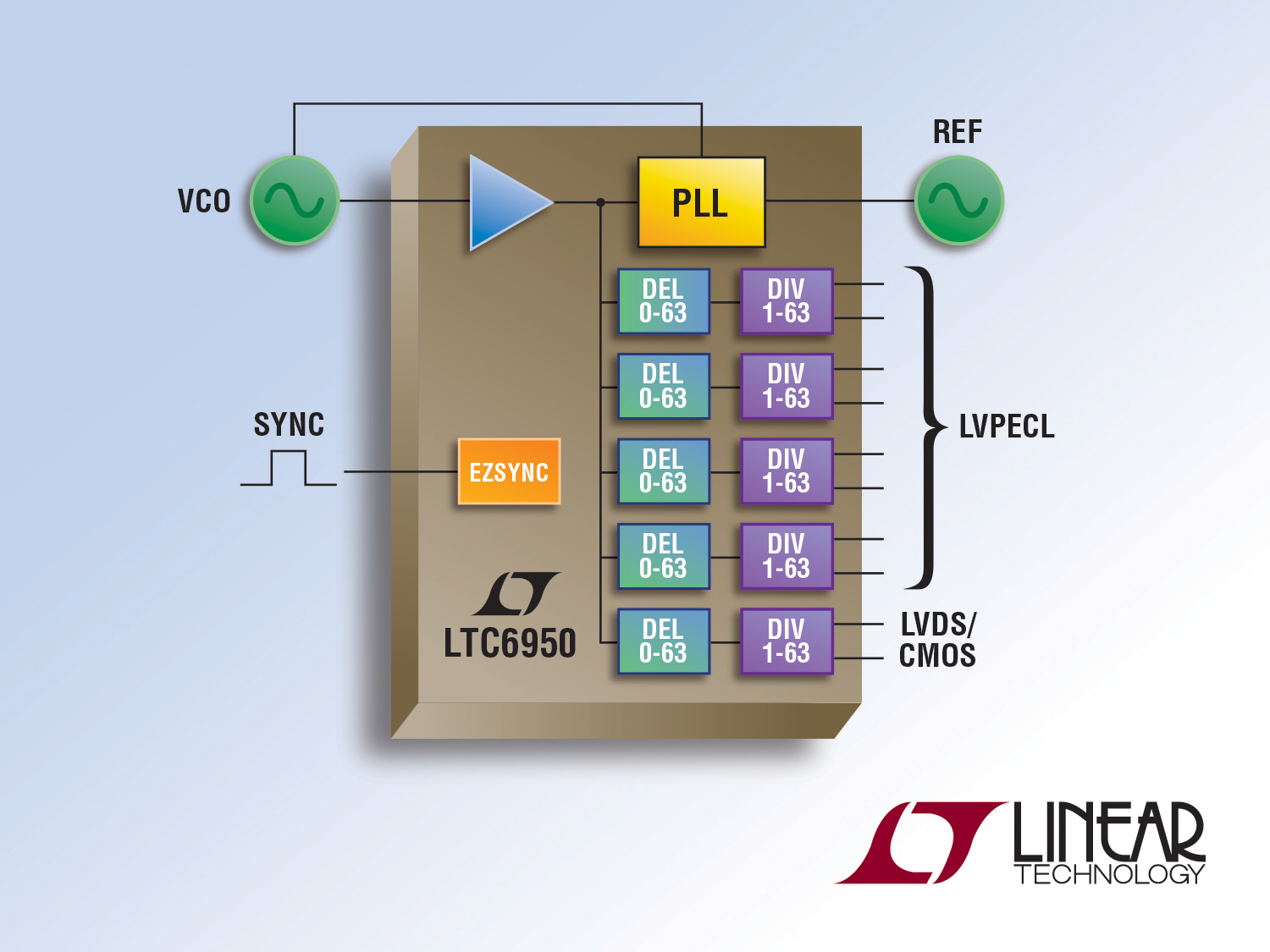

凌力尔特公司 (Linear Technology Corporation) 推出低相位噪声整数 N 合成器内核 LTC6950,该产品具超低抖动时钟分配输出电路。LTC6950 非常适用于产生和分配具高信噪比 (SNR) 时钟数据转换器必不可少的低抖动信号。当数字化或合成高模拟频率时,保持数据转换器时钟低抖动是实现出色 SNR 水平的基础。例如,新式电子系统需要用 ADC 直接数字化 RF 和高 IF 信号。凭借 18fsRMS 抖动 (在 12kHz 至 20MHz 带宽上),LTC6950 保证

关键字:

凌力尔特 PLL LTC6950

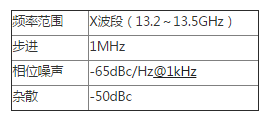

根据IEEE 521-2002标准,X波段是指频率在8-12 GHz的无线电波波段,在电磁波谱中属于微波。而在某些场合中,X波段的频率范围则为7-11.2 GHz。通俗而言,X波段中的X即英语中的“extended”,表示“扩展的”调幅广播。本文介绍基于X波段的天线、频率合成器、振荡器等的设计实现方案,供大家参考。

X波段频率合成器设计

本文提出LL频率合成方案是用于频率合成器设计的一种较好的方案,PLL频率合成器在相位噪声特性、杂波抑制及频

关键字:

天线 VCO PLL

1 引言

随着现代通信技术的不断发展,对频率源的要求越来越高。一方面,由于通信容量的迅速扩大,使得通信频谱不断向高端扩展;另一方面,由于频谱资源的相对匮乏,必须提高频谱利用率,进而对频率源的频谱纯度和频率稳定度都提出了更高的要求。

在无线通信领域中,为了提高频谱利用率,现代通信系统对频率合成器的精度、频率分辨率、转换时间和频谱纯度等指标提出了越来越高的要求。频率合成的方法主要有直接频率合成(DS)、间接频率合成(PLL)和直接数字频率合成(DDS)等方案。直接频率合成体积大、成本高, 有较

关键字:

X波段 PLL VCO

1 引言

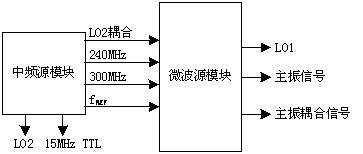

频率源是所有电子系统(雷达、通讯、测控、导航等)的基本信号来源,其主要包括固定频率源和合成频率源两类。其中合成频率源又称频率合成(综合)器,按其构成方式可分为直接式和间接式。采用锁相环(PLL)技术的间接频率合成器目前应用最为广泛。直接模拟频率合成器(DAS)采用倍频器、分频器、混频器及微波开关来实现频率合成,具有最优的近端相位噪声和高速捷变频特性,但结构复杂、成本昂贵的特点限制其只能应用于雷达等高端领域。直接数字合成器(DDS)目前也得到了广泛应用,但高性能DDS产品的输出频率还有待

关键字:

X波段 频率综合器 DDS

1 引言

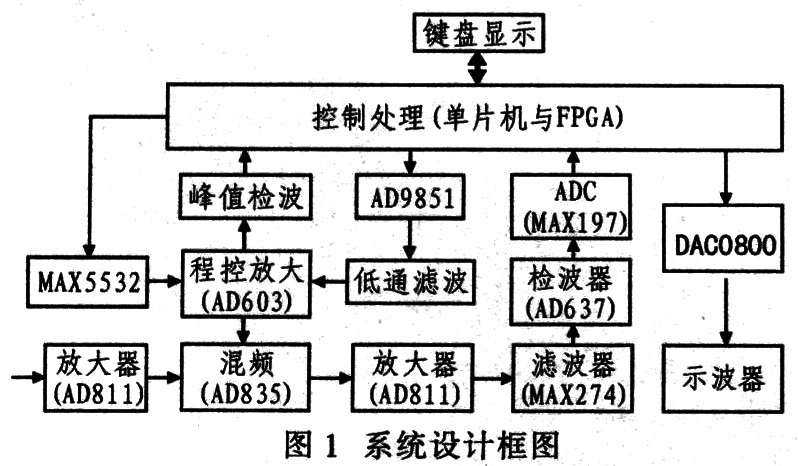

直接数字频率合成(DDS)是近几年一种新型的频率合成法,其具有频率切换速度快,频率分辨率高,以及便于集成等优点。在此,设计了基于DDS的频谱分析仪,该频谱分析仪依据外差原理,被测信号与本征频率混频,实现信号的频谱分析。

2 系统设计

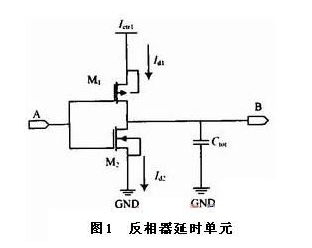

图1给出系统设计框图,主要由本机振荡电路、混频电路、放大检波电路、频谱输出显示电路等组成。通过单片机和现场可编程门阵列(FPGA)共同控制AD985l,以产生正弦扫频输出信号,然后经滤波、程控放大得到稳定输出,与经放大处理的被测信号混频,再经放

关键字:

DDS FPGA AD985l

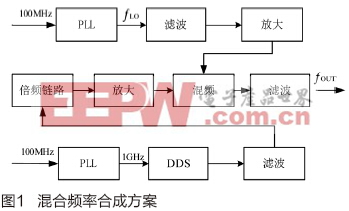

摘要:本文介绍了一种C波段宽带捷变频率综合器的设计方法,采用直接数字频率合成器(DDS)实现频率捷变,采用倍频链路扩展输出带宽,通过与锁相环(PLL)合成产生的本振信号混频将输出频率搬移到C波段。论述了DDS时钟电路、倍频链路以及混频部分的设计方法,并给出了达到的主要技术指标和测试结果。

引言

频率合成器是现代通讯系统必不可少的关键电路, 是电子系统的主要信号源,是决定电子系统性能的关键设备。随着系统对频率源的频率稳定度、频谱纯度、频率范围和输出频率个数的要求越来越高,高稳定、低相位噪声、

关键字:

变频率综合器 DDS PLL C波段 合成器 201410

1、前言

分频器是FPGA设计中使用频率非常高的基本单元之一。尽管目前在大部分设计中还广泛使用集成锁相环(如Altera的PLL,Xilinx的DLL)来进行时钟的分频、倍频以及相移设计,但是,对于时钟要求不太严格的设计,通过自主设计进行时钟分频的实现方法仍然非常流行。首先这种方法可以节省锁相环资源,再者这种方式只消耗不多的逻辑单元就可以达到对时钟的操作目的。

2、整数倍分频器的设计

2.1 偶数倍分频

偶数倍分频器的实现非常简单,只需要一个计数器进行计数就能实现。如需要N分频

关键字:

FPGA 分频器 PLL

电子产品世界,为电子工程师提供全面的电子产品信息和行业解决方案,是电子工程师的技术中心和交流中心,是电子产品的市场中心,EEPW 20年的品牌历史,是电子工程师的网络家园

关键字:

定时应用 PLL 振荡器 内部时钟 合成器IC技术

高性能模拟与混合信号IC领导厂商Silicon Labs(芯科实验室有限公司)今日宣布针对高速网络、通信和数据中心等当今互联网基础设施的根基,推出业界最高频率灵活性和领先抖动性能的时钟解决方案。Silicon Labs的新一代Si534x“片上时钟树“系列产品包括高性能时钟发生器和高集成度Multi-PLL抖动衰减器。这些单芯片、超低抖动时钟芯片整合了时钟合成与抖动衰减功能,设计旨在减少光传输网络、无线基础设施、宽带接入/汇聚、电信级以太网、测试和测量以及企业和数据中心设备(包

关键字:

Silicon Labs Multi-PLL 时钟

dds-pll介绍

您好,目前还没有人创建词条dds-pll!

欢迎您创建该词条,阐述对dds-pll的理解,并与今后在此搜索dds-pll的朋友们分享。

创建词条

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473