处理器设计的谬误—第三部分

这个系列的深度报道文章统计了失败的处理器种群。这些文章探索了造成每一种处理器种群死亡的主要设计错误。每一种主要的设计错误也以一或两个例子进行了阐述。前两部分讨论了支持特殊语言的高级计算机指令集架构的发展;允许简单机器仿效其长辈的中间ISA的使用等。除此之外,还有堆栈机、极端CISC和RISC处理器、VLIW机以及过度地迅速成长的流水线操作等,以及本文讨论的不平衡的处理器设计

本文引用地址:https://www.eepw.com.cn/article/90483.htm错误3:不平衡的处理器设计

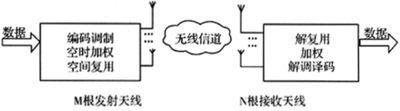

随着处理器社群成为富有魅力的宠儿,处理器流水线似乎受到了人们不成比例的关注。然而,处理器的性能更多地取决于其执行流水线。因为就任何工程学科来说,优良的处理器性能取决于平衡的设计。许多属性均对处理器(或系统)的整体性能有贡献,而这些因素当中的任何一个均能对运行实时应用程序的“完美”流水线的运行效率造成不良的影响,如果该流水线与其它的流水线处于不平衡状态的话。设计工程师必须采用一种经扩展的设计决策配置以及各种新技术来产生平衡、有成本经济性的系统。

过去十年中,在处理器设计上的进展包括两个方面:1.在电路设计上的进展,它造成时钟速率从1985~2005年期间每年以大约30%的速度提高;2.在架构上的改善—包括采用更宽的指令集、VLIW架构以及经深思熟虑的执行,这使得微处理器发出指令的速率远远快于主存储器带宽增长的速率或者主存储器存取延迟时间缩短的速率。因此,微处理器对大块或主存储器的存取暂时变得昂贵了,这种趋势迫使架构和系统级要做出的设计变更包括:

·对主存储器的更宽连接(更多的引脚);

·更大和更高效率的指令以及数据高速缓冲存储器;

·以存储器为中心的系统架构。

这些新方法当中的每一种均带来了各种好处并招致成本的提高。

在1997年有一篇文章把处理器的执行时间分为三个时间段,它帮助解释处理器的设计如何可能做到较佳的平衡。这三个时间段分别是:

·处理器时间:当处理器被完全使用或部分使用并且因缺乏指令级的并行处理能力而造成部分的停止运行时;

·延迟时间:在竞争之前损失的时间—存储器延迟时间更短(在存储器各个层级之间提高存储带宽无法缩短延迟时间);

·带宽时间:在存储器竞争之前的时间损失加上因存储器各层级之间的存储带宽不足而引起的时间损失;

许多“现代”处理器设计技术加剧了上述所有三个执行时间段所带来的问题。不确定的软件和硬件预取技术—通过确保当需要时数据才实际处于高速缓冲存储器之中—能够改善处理器的性能,但是,这些技术会增加对主存储器的流量,并且,当它们预取不需要的数据、预取在被使用之前就被逐出的数据、或者预取在可被使用之前就被逐出处理器高速缓冲存储器的其它数据(迫使该数据被重新抓取)时,会浪费带宽。多线程通过无论何时一个线程停止—因存储器存取延迟时间太长或I/O操作时间太长—均切换至一个准备就绪的线程而提高处理器的吞吐量,但是,频繁的线程切换会搞乱高速缓冲存储器以及TLB。因此,由多线程达到的好处可能因高速缓冲存储器效率的降低而部分或完全受到抵消。

失去平衡

盲目地追逐高时钟速率也驱使处理器的设计失去平衡。随着处理器变得越来越快,它们以更快的速率占用指令和操作码,这对主存储器延迟以及带宽的要求提出更大的压力。最近朝着同类、具有一致的高速缓冲存储器的多核处理器以及通用主存储器发展的趋势,也增加了主存储器的延迟以及带宽要求。试验显示,把压力放在处理器至主存储器接口上的积极进取的设计技术,可能导致处理器停止工作并在多达50%的时间里等待存储器。这样的系统显然是失去平衡的系统。

深亚微米以及纳米电路的影响也驱使传统的处理器设计失去平衡。互连延迟—以前不重要—现在在整个门延迟上占据主导地位,因为线延迟并不会随着特征尺寸的缩小而缩短,除非线的截面积的宽高比发生变化。正如在以前的部分所讨论的,Intel奔腾4微处理器—它达到了3.8GHz的商业时钟速率—的设计工程师被迫把该处理器的20级执行流水线投入于适应片上的线延迟。

因为深亚微米和纳米设计规则已经允许时钟速率上升,微处理器设计工程师已经采取进一步降低内核工作电压的措施以期限制功耗的增加。然而,这么做需要采用具有更低阀值电压的晶体管以适应更低的内核工作电压。依次下来,在90nm及以下工艺级别,当阀值电压被降低到一定水平时,因泄漏引起的处理器功耗大致会等于它的动态功耗。这样的处理器即使当什么也不做时也会消耗大量的功率。

对高速缓冲存储器的依赖

所有这些选择和结果就是在处理器的架构上迫使采取新的发展方向。首先,在这些新方向当中的一个方向就是需要采用更加高效率的高速缓存。在目前的高速缓存中保存的那部分数据当中,有0.05%~33%是活跃的(在被逐出之前将被再次刷新)。那意味着处理器高速缓冲存储器的大多数空间通常填满了不流动、无用的数据以及指令。经改善的高速缓冲存储器的管理逻辑能够把高速缓存与主存储器之间的流量减少为原来的1/2乃至1/100,因此,对硅片是一种明智的支出。提高高速缓存效率的一个途径就是以比高速缓存更精细的粒度来高速缓存各个对象,从而提高高速缓存标签的开销但降低对带宽的要求。

把处理器的主存储器集成在同一颗处理器芯片上,能够有效地把整个片上主存储器做在高速缓存之中,从而消除存储器的层次并充分减少存储器的开销。在这个方向上进一步推进设计,就产生了把微处理器嵌入至独立存储器阵列的、以存储器为中心的架构。这就是MPSOC(多处理器系统级芯片)的领域,它寻求把整个处理负荷分布在大量小的、廉价的、以低速率运行的处理器上。因此,MPSOC很可能成为未来高性能处理器的架构。(本文译自《微处理器报告》)

参考文献:

[1] BURGER D, GOODMAN J R, KAGI A. Limited Bandwidth to Affect Processor Design[J]. IEEE Micro, 1997(11-12), 55-62

[2] FLYNN M J, HUNG P, RUDD K W. Deep-Submicron Microprocessor Design Issues[J]. IEEE Micro, 1999(7-8), 2-13

[3] NURMI J. Processor Design: System-On-Chip Computing for ASICs and FPGAs[M[. [S.I.]. 2007

[4] FAGIN B, PATT Y, SIRNI V, etc. Compiling Prolog into Microcode: A Case Study Using the NCR/32-000. Proceedings of the 18th IEEE Microprogramming Workshop, 1985[C]

[5] Halfhill T. AMD K6 Takes On Intel P6[J/OL]. 1996(1). http://www.byte.com/art/9601/sec7/art1.htm/

评论