基于DDS的数字PLL

多年以来,作为业界主流产品的模拟PLL已被熟知,模拟PLL性能稳定,可为频率合成和抖动消除提供低成本的解决方案,工作频率高达8GHz及以上。然而新兴的基于直接数字频率合成(DDS)的数字PLL在某些应用中极具竞争力。

本文引用地址:https://www.eepw.com.cn/article/89479.htm数字PLL利用数字逻辑实现传统的PLL模块。虽然实现数字PLL的方法有很多,但本文只介绍基于DDS的数字PLL架构。

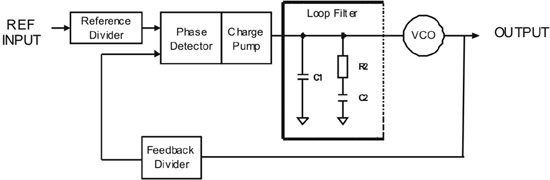

图1 典型的模拟PLL结构框图

图1所示的是典型的模拟PLL。输入信号首先进入参考分频器,参考分频器可降低输入鉴相器的信号频率。在PLL中,参考分频器的设置非常关键。如果设计人员必须使用大的分频比降低鉴相频率来生成期望的输出信号,那么环路带宽就会受到限制。下文将会对这一点进行详细说明。

在模拟PLL中,鉴相器产生上升或下降的电流脉冲,其持续时间与参考信号和反馈信号的相差成正比。而对于数字PLL,鉴相器的输出是与输入参考信号沿和反馈信号沿的时间差成正比的数字量。这些数字量被送入数字环路滤波器,完成滤波并对鉴相器的输出进行积分。环路滤波器的参数是数字型的,但可以较容易的改变,同时,与模拟PLL不同,其大小没有限制。另外,数字鉴相器不受热噪声、老化或漂移以及电荷泵失配或泄露的影响。而在模拟PLL中,当电荷泵中的晶体管没有完全关断或其它泄漏导致压控振荡器(VCO)中有不希望的电压变化时,都会发生电荷泵泄漏。另外,模拟PLL中电荷泵泄漏和驱动器上升/下降电流的失配会导致输出信号的频谱在鉴相器频率上出现杂散,而数字PLL由于没有电荷泵,因此避免了这种现象发生。

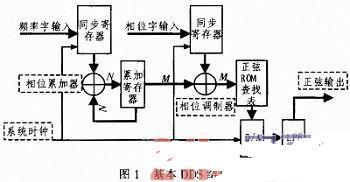

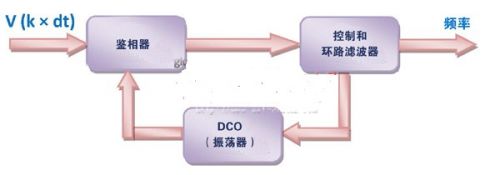

图2 基于DDS的数字PLL结构框图

在基于DDS的数字PLL中,直接数字频率合成(DDS)和数模转换器(DAC)代替了传统的压控振荡器(VCO)。DDS的输入是数字调谐字,用于设置输出信号的频率。这与VCO类似,VCO的模拟输入电压用于调节输出信号的频率。在1GHz频率下运行的DDS的调谐频率范围为DC~400MHz。如果利用奈奎斯特频率(DAC采样速率的一半)以上的DAC镜像作为信号,频率范围还可以进一步增大。DAC的输出被送到外部低通重构滤波器中,以滤除不需要的谐波,然后再反馈到内置反馈分频器中,这样就形成了闭合回路。

数字PLL中的重构滤波器是模拟PLL中没有的部分。低通滤波器滤除基频频率以上的频率信号。根据滤波需求以及输出频率与奈奎斯特频率的接近程度,通常会采用五阶或七阶低通滤波器。之后,正弦波被送入扇出缓冲器中,以产生方波时钟输出信号。为了滤除附加噪声或允许PLL工作于奈奎斯特频率以上,可使用带通滤波器代替低通滤波器。这时有可能在输出频率或低于输出频率的地方出现没有滤除的杂散,因此设计者必须谨慎做出频率规划,在不会出现问题的频率上运行DAC。

一旦理解了数字PLL中的各个组成模块,我们就能够开始认识到与这些数字单元相关的优势。首先,数字PLL非常适合频率转换应用。例如,将普通的19.44MHz的时钟频率转换为156.25MHz,需要对输入信号进行1944分频,使鉴相器在10kHz频率下工作。为了保持环路的稳定性, PLL环路带宽通常被限制在鉴相器频率的1/10左右,在本例中带宽为1kHz。小数N分频PLL有助于保持鉴相器的高工作频率,但会带来自身的一些问题。在模拟PLL中,低环路带宽需要大容量的元件,这不仅会占用电路板空间,而且当使用陶瓷电容时还会导致自谐振。由于相位修正的步长有限,数字PLL也可能产生参考杂散信号,但是,由于数字环路滤波器很容易实现非常小的环路带宽(< 1 Hz),因此这个杂散信号很容易被抑制。更重要的是,由于环路特性由数字系数来决定,因此数字PLL能够比模拟PLL更好地控制环路动态特性。这是相位调制系统的一个主要优点。

对任何PLL来说,PLL环路带宽内的参考噪声能通过,而带外的参考噪声会被衰减。基于DDS的双环路数字PLL架构的主要优点是输出相位噪声取决于DAC系统时钟,而不是模拟VCO。这允许设计人员选择能够满足其特定抖动需求的系统时钟源。在模拟PLL中,用其它VCO取代现有VCO需要匹配供电电压、增益、频率范围以及其它参数,这是很困难的,但并不是不可能的。在模拟PLL中,设计人员必须为了VCO相位噪声而对VCO调谐范围进行权衡,VCO噪声会随着VCO频率范围的增加而增加。而DDS数字PLL就没有这样的限制。通过提供一个干净的DAC系统时钟,设计人员可以获得等效的宽带低噪声VCO。设计人员可以选择低的PLL环路带宽以清除抖动。如何选择合适的DAC系统将在下文中介绍。

由于数字PLL中的鉴相器增益、环路带宽和相位裕度都是可编程的,因此用户可以在不同的条件下保持相同的环路传递函数。例如,为吉比特以太网产生125MHz的参考时钟,参考输入信号可能是8kHz的BITS时钟,也可能是19.44MHz的SONET/SDH参考时钟。在这两种情况下,数字PLL中为获得固定的环路带宽和相位裕度,可对环路滤波器进行优化。更重要的是,只需对寄存器进行编程就可以调整环路参数,而无需更换器件。

基于DDS的数字PLL的另一个重要优点就是可以使用高速DAC系统时钟来进行参考监控。此时钟可用来对参考输入信号进行过采样,允许对参考时钟的漂移或故障进行快速检测。一旦检测到故障,设备或者自动切换输入信号,或者转入保持模式。在数字逻辑中能够很容易地实现时钟无中断切换。当两个参考时钟都发生故障时,就会出现时钟保持,并且如果需要,数字PLL就会像一个DDS频率合成器一样连续输出相同频率的信号。在保持模式下,输出时钟的稳定性与系统时钟相同。如果要利用模拟PLL实现这一功能,那么则需要一个与参考输入信号频率成倍数的外部振荡器,或者需要VCO的控制电压在长时间内及一定温度下是稳定的亚微伏电平。前者也许可行,而后者一定无法实现。

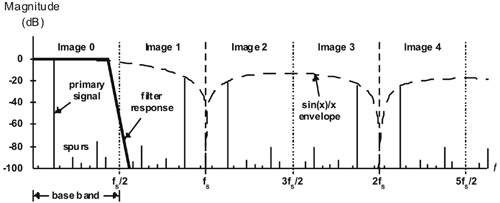

DAC杂散的存在是数字PLL的一个缺点。这里只对DAC杂散做简要的介绍。即使是理想的DAC,也会在整个频带内产生谐波和不希望的谱能量,这是由DAC的非线性特性造成的。DAC性能的衡量标准是在没有重构滤波器的情况下测得的无杂散动态范围(SFDR)。SFDR是从直流到DAC采样频率一半范围内最大杂散与载波功率值的比值。对于14bit DAC来说,宽带SFDR通常为-50dBc ~ -70dBc。在希望的输出频率处或输出频率之下出现高阶的DAC杂散是有可能的,这些杂散的幅值通常很低(<?70 dBc)。衰减DAC杂散的主要方法是使用重构滤波器,七阶的低通滤波器可以快速地削弱杂散信号。图3所示的是典型的DAC输出频谱和重构滤波器频率响应。设计人员应该谨慎地选择系统的时钟频率,使低阶的杂散信号不会与希望的输出频率太接近,从而有效地滤除杂散。

图3 DAC的频谱与重构滤波器响应的关系

使用数字PLL时,选择合适的DAC系统时钟是很重要的。在大多数应用中,高频振荡器可用于直接提供800MHz ~ 1000MHz的DAC系统时钟。但是,这些器件比较昂贵,很少会使用。而许多数字PLL具有模拟PLL时钟倍频器,其产生的相位噪声在许多应用中也是可以接受的。这样,设计人员可以使用通用的16MHz或25MHz晶体或频率范围在16MHz ~ 100MHz的晶体振荡器,通过片上PLL产生1GHz的系统时钟。在计算任何抖动时,都必须考虑片上PLL的噪声。

选择晶体振荡器时,设计人员应该考虑希望的输出相位噪声及稳定性的需求。例如,如果在保持模式下需求Stratum 2的时钟稳定度,那么,就应该为系统时钟使用Stratum 2兼容的振荡器。输出相位噪声不仅是振荡器相位噪声的函数,而且包括由系统时钟PLL(如果使用的话)提供的倍频量。采用80MHz的三阶泛音晶体振荡器驱动系统时钟PLL时得到的总相位噪声,会优于采用25MHz振荡器驱动时所得到的总相位噪声。

为了克服任何一种PLL设计的限制,可以使用数字PLL结合模拟PLL的解决方案。数字PLL能够处理时钟切换和频率比的问题,而模拟PLL则用来进一步衰减杂散,增大频率,并进行时钟分配。

那么模拟PLL和数字PLL哪个更好呢?当然,答案取决于具体的应用。在不需要保持、参考切换和环路配置的系统中,模拟PLL是更好的解决方案,且允许产生较高的输出频率。而在需要流畅切换、保持,及较好控制环路动态范围的冗余时钟应用中,数字PLL是更好的解决方案。它的灵活性和动态配置能力允许参考输入可以是不同频率,而且,基于DDS的数字PLL允许参考频率很低。

基于DDS的数字PLL能提供传统PLL不能实现的解决方案。通过应用数字逻辑实现PLL构建模块,性能与灵活性都得到提升,比模拟PLL更具吸引力。

低通滤波器相关文章:低通滤波器原理

分频器相关文章:分频器原理 鉴相器相关文章:鉴相器原理 数字滤波器相关文章:数字滤波器原理

评论