FPGA系统内部逻辑在线测试技术研究

1 引言

本文引用地址:https://www.eepw.com.cn/article/88005.htm随着FPGA向低成本、低功耗、高性能方向发展,其I/O引脚大多采用微间距TOFP或BGA封装工艺,因而使引出多种内部信号的I/O引脚以及FPGA的验证工作变得非常困难,同时FPGA的验证和调试耗时占总开发时间的50%以上。

在验证和调试系统时,传统上是把信号线引到I/O引脚,然后采用示波器、逻辑分析仪或总线分析仪进行测量和分析。由于这些设备相当昂贵,而且调试时又需要许多连线夹,因此一不小心就会烧坏器件或电路板。

伴随着EDA 工具的快速发展,Altera公司在QuartusⅡ软件中开发出一种嵌入式调试工具SignalTapⅡ,它是基于逻辑分析核的嵌入式逻辑分析仪,不仅具备普通逻辑分析仪的触发、数据采集和存储功能,还可访问FPGA器件内部的所有信号和节点,除Altera公司开发的这种嵌入式逻辑分析仪外,其他主流FPGA公司,如 Xilinx、Lattice、Actel等也有相似技术,其中最具代表性的是Xilinx公司的ChipScope Pro工具,它是专为Xilinx FPGA系统内的凋试而设计的。Chip-Scope Pro核心集成在FPGA中,支持所有XiLinx FPGA系列,并通过标准的JTAG端口提供实时的调试和验证能力。

2 SignalTap II原理

SignalTap II嵌入逻辑分析仪是专门用于Quartus II设计软件中的第二代系统级调试工具。对于嵌人式逻辑分析仪内核(知识产权IP核)插入FPGA的设计,同时提供触发功能和存储功能。在FPGA运行过程中,满足触发条件时SignalTaPⅡ将启动采样并储存数据,采样数据不断刷新片内存储器内容。SignalTapⅡ通过下载线ByteBlasterⅡ,将捕获到的信号数据从器件的RAM资源载至QuartusⅡ开发环境,以实时显示波形。这样就能使开发者在整个设计过程中,以系统级的速度来观察硬件和软件的交互作用。

目前,SignalTapⅡ逻辑分析仪可以支持的器件系列有:Cyclone、CycloneⅡ、Cyclone Ⅲ、APEXTⅡ、APEX 20KE、APEX20KC、APEX20K、Excalibur、Mercury、Stratix GX、Stratix、StratixⅡ、Stratix Ⅲ等。

3 SignalTapⅡ使用方法

使用SignalTapⅡ的一般程序是:设计人员在完成设计并编译工程后,建立SignalTap Ⅱ(.stp)文件,并加入工程、配置STP文件、编译并下载没计到FPGA、在Quartus Ⅱ软件中显示被测信号的仿真波形。

设置SignalTapⅡ文件的基本流程如下:

(1)设置采样时钟。决定了显示信号波形的分辨率,根据Altera公司的建议最好使用全局时钟,而非门控时钟,否则会使采样时钟处于不能准确反映设计数据的状态。

(2)配置采样深度,确定RAM的大小。用户可指定要观测数据的采样点数,即数据存储深度。

(3)设置buffer acquisition mode。包括循环采样存储和连续采样存储两种模式。图1给出STP参数配置过程。

(4)触发级别。SignalTapⅡ是支持多触发级的触发方式,最多可支持10级触发。在多级触发中,SignalTapⅡ首先对第一级触发模式进行触发;当第一级触发表达式满足条件,测试结果为TRUE时,SignalTapⅡ对第二级触发表达式进行测试;依次类推,直到所有触发级均完成测试,并且最后一级触发条件为TRUE时,SignalTapⅡ开始捕捉信号状态。

(5)触发条件。可以设定复杂的触发条件用以捕获相应的数据,以协助调试设计。当满足触发条件时,在SignalTapⅡ时钟的上升沿采样被测信号。

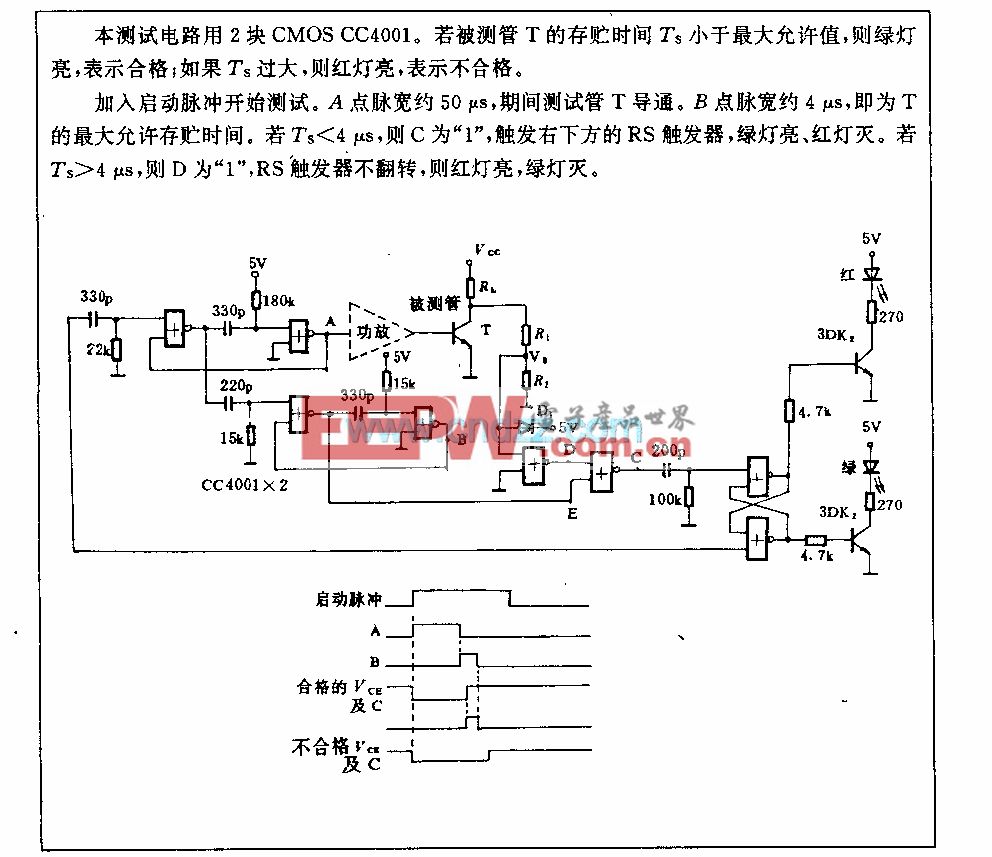

(6)设置被测信号。在SignalTapⅡ逻辑分析仪窗口,双击鼠标左键,弹出的Node Finder对话框,在filter中选择要加人STP文件的节点或总线。图2所示给出了待测信号及触发设置。

完成STP设置后,加载SAM对象文件(.sof),在Device列表中选择目标器件,点击Program Device图标进行器件编程,点击Run Analysis进行采集、分析数据,如图3所示。

4 实例分析

现以FT245BM型USB与EP2C8 0208C8N型FPGA间的简单通信为实例,具体说明如何采用SignalTapⅡ验证FPGA的设计。其顶层设计文件如图4所示。

FT245BM是FTDI(Future Technology Devices IntlLtd)公司的一种快速USB通信接口。它无需编写片内固件程序。FTDI公司提供D2XX官方驱动程序,使用D2XX驱动程序能获得更好的数据传输性能,且传输速率最大可达1 MB/s。

FT245BM的主要功能是在内部硬件逻辑的作用下实现USB串行数据格式与并行数据格式的双向转换。PC机通过USB接口与FT245BM进行数据交换,FT245BM通过并行方式与下位微控制器通信。利用单芯片实现USB与并行FIFO缓冲区的双向数据传输;通过简单的四线握手信号与FPGA等逻辑器件接口;FT245BM通过8位并行数据口D[0,7]和4位读写状态/控制口RXF#、TXE#、RD#、WR实现与EP2C8交换数据,而PC机与FT245BM间通过UISB总线传输数据。可选的外部EEPROM用于存储USB设备的特定信息,通过EECS、EESK、EEDATA来完成数据的写入和读出。

在调试中,按照上述SignalTapⅡ的使用步骤,在编译后的工程中添加STP文件,并对文件进行设置。首先设置采样时钟gclk,系统时钟采用32.768 MHz;然后添加采样深度的设置,设为2 K;最后在STP文件中将Buffer AcquisitionMode分别设为连续存储和循环采样存储两种模式进行验证。连续存储方式记录采样操作的连续过程,而在循环采样存储方式下SignalTapⅡ记录多次采样时刻数据。

当外部实验开发系统连接好后,进行编译下载。单击SignalTapⅡ面板上的Autorun Analysis按钮,启动SignalTapⅡ进行采样和分析,此时就能从SignalTaDⅡ数据窗通过JTAG口观察到来自实验板上FPGA内部的实时信号,该实例的输出信号如图5所示。

实际中将遇到许多竞争处理和不完善的地方,然而由于使用了SignalTapⅡ工具,所以能直观地看到内部的逻辑状况,这大大减少了开发周期,并能顺利地进行调试。

5 结语

Quartus中的SignalTapⅡ工具成功克服了传统逻辑分析仪的缺点,提供了一个测试器件的很好途径,还具有实时可视性,大大减少了调试、验证过程花费的时间,加快了设计周期。通过对CycloneⅡ系列EP2C8Q208C8进行实验,证实该测试手段大大提高了系统的调试能力,效果很好。但需注意的是,它是一块自主逻辑,需要占据FPGA资源。比如RAM,LE等,资源消耗量与需采集的数据量成正比。因此不能无限制地采集信号,一般采集信号的深度不大。再者,由于时钟的限制,无法看到有毛刺的现象,实际应用中也存在一定的限制。另外,SignalTapⅡ工作在JTAG方式,调试完成后,需将SignalTapⅡ移除设计,以免浪费资源。

评论