基于FPGA的高速PID控制器设计与仿真

在CNC(电脑数控)加工、激光切割、自动化磨辊弧焊系统、步进/伺服电机控制及其他由电机控制的机械组装定位运动控制系统中,PID控制器应用得非常广泛。其设计技术成熟,长期以来形成了典型的结构,参数整定方便,结构更改灵活,能满足一般控制的要求。

本文引用地址:https://www.eepw.com.cn/article/82229.htm此类运动控制系统的被控量常为速度、角度等模拟量,被控量与设定值之间的误差值经离散化处理后,可由数字PID控制器实现的控制算法加以运算,最后再转换为模拟量反馈给被控对象,这就是PID控制中常用的近似逼近原理。

采用这种结构设计的控制系统,其性能只能与原连续控制系统性能接近而不会超过,逼近的精度与被变换的连续数学模型大小及采样周期长短有关[1]。特别是在高速运动控制的情况下,采样周期的影响更大,采样周期相对较长时,逼近程度才较好,但是对PID控制算法的运算速度及回路的调节时间等也提出了更高的要求。

可编程逻辑器件FPGA的逻辑门数为5000~200万个,属于大规模甚至超大规模逻辑器件,其工作频率最高可达250MHz。因此,无论从编程规模还是工作速度上,完全可以用来实现高速PID控制器。本设计使用Altera公司的Cyclone系列FPGA器件EP1C3作为硬件开发平台,对运动控制中常用的增量式数字PID控制算法进行优化处理,提高了运算速度和回路的调节时间。

1 增量式数字PID控制算法的FPGA实现

经典PID控制方程为:

![]()

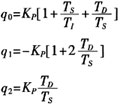

式中,KP为比例放大系数;K1为积分时间常数;KD为微分时间常数。数字PID控制算法的实现,必须用数值逼近的方法。当采样周期相当短时,用求和代替积分,用差商代替微商,使PID算法离散化,将描述连续一时间PID算法的微分方程离散化、差分、归并处理后可得:

![]()

从(2)式可以看出,增量式数字PID算法,只要储存最近的三个误差采样值e(k)、e(k-1)、e(k-2)就足够了。实现此增量式数字PID控制算法的结构图如图1所示。

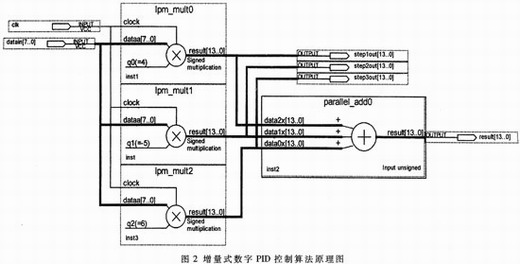

图1中虚线框以内的结构是三个具有移位功能的乘法器,可以使用Altera公司提供的经过严格测试和优化处理的宏功能模块LPM_MULT(M0~M2)实现。LPM_MULT是一个可定制位宽的加法/乘法器,在此,定制误差输入值e(k)的位宽为8bit,另一常量乘数q0、q1、q2为整定后的PID控制器的控制参数,位宽为6bit,乘法器输出结果位宽为14bit。QuartusII中的原理图如图2所示。

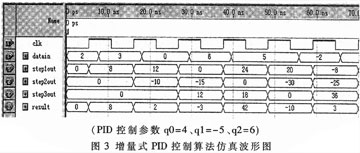

LPM_MULT宏功能模块还可以定制运算结果输出时等待同步脉冲(clock)的个数,这就是LPM_MULT的流水线输出功能。图2中指定lpm_mult0、lpm_multl、:lpm_mult2的等待时间依次为1、2、3个同步脉冲,这种设计自然地实现了移位相乘操作;同时利用乘法器的流水线功能,提高了乘法运算的速度。优化后的功能仿真波形如图3所示。

由图2、图3可见,在第K个流水线推进时钟信号clk的上跳沿,lpm_mult0输出当前时刻下的乘积运算结果steplout,lpm_multl输出K一1时刻下的乘积结果step2out,lpm_mult2输出K-2时刻下的乘积结果step3out,并行加法运算部件parallel_add的输出值为result=steplout+step2out+step3out。

2 通用模/数、数/模转换器的设计与仿真

为了不失系统的通用性和可扩展性,参照ADI公司8bit、半闪烁型A/D转换器AD7822的时序图,设计了通用A/D转换部件typical_ADC实现系统的模/数转换仿真功能。typical_adc部件是一个理想化的A/D转换芯片,主要由一个8位地址计数器和一个存放正弦数据的ROM构成,它模拟正弦信号的采样、量化过程,采样周期只与系统的工作时钟有关[2]。

相对于模/数转换而言,数/模转换的控制信号要少一些,时序要求更简单。参照TI公司14位D/A转换芯片DAC8806的功能表,设计了一个通用D/A转换部件typical_dac实现系统的数/模转换仿真功能。为了形式化地表示系统的D/A转换过程,typical_dac只是对PID算法的输出量△u(k)做了一个奇偶校验运算,VHDL语言描述如下:

ARCHITECTURE behav OF typical_dac IS

BEGIN-当转换控制信号wr为低电平时输出各位异或值,否则输出高阻态

uout<=(datain(0)XOR datain(1)XOR datain(2)XOR datain(3)XOR datain(4)XOR datain(5)XORdatain(6) XOR datain(7)X0R datain(8)XOR datain(9):XOR datain(10)XOR datain(11)XOR datain(12)XOR datain (13)XOR`1`)WHEN wr=`0`ELSE`z`;END behav;;

3 工作控制状态机的设计

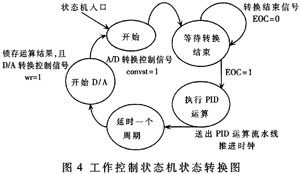

典型的数字PID控制系统由A/D转换、PID控制算法和D/A转换三个关键环节构成。为了协调三个环节之间的工作流程,系统工作控制部件必不可少。纯硬件数字系统的顺序控制有多种方案可选,如单片机辅助控制、嵌入式CPU软核控制、脉冲计数控制等等,但都难以兼顾系统的高速控制和灵活扩展。在高速运算和控制方面,有限状态机具有以上几种控制方式难以超越的优越性。

从状态机的信号输出方式上分,有Moore型和Mealy型两类状态机。从输出时序上看,前者属于同步输出状态机,而后者属于异步输出状态机。Mealy型状态机的输出是当前状态和所有输入信号的函数,它的输出是在输入变化后立即发生的,不依赖于时钟的同步[2]。

Moore型状态机的输出则仅为当前状态的函数,这类状态机在输入发生变化时还必须等待时钟的到来,时钟使状态发生变化时才导致输出的变化,所以比Mealy机要多等待一个时钟周期,但是能有效避免毛刺现象。本设计所用的状态机为单进程Moore型状态机。状态转换如图4所示。

4 系统实现与功能仿真

整个PID控制器的系统设计采用自顶向下的设计方法和模块化的设计思想,即先由PTD控制器的自然语言描述得到VHDL的系统行为描述,然后对系统分解为误差A/D变换部件、PID运算部件、控制增量D/A变换以及协调三者的控制状态机等四个主要模块。

Altera公司专用EDA软件QuartusII支持原理图与VHDL语言混合输入设计方式,除PID运算部件采用原理图输入设计方式以外,其余三个部件均采用VHDL输入设计方式。系统仿真时,如果将系统的最高工作速率设定为120MHz,则采样速率为24MHz。功能仿真波形图如图5所示。

通过对增量式数字PID控制算法的优化处理,显著提高了系统的工作速度。仿真结果表明,拥有较低转换速率的A/D变换技术成为提高系统运行速度的瓶颈。就本设计采用的闪烁型A/D器件而言,减少状态机等待A/D转换结束信号EOC(见图4)的时间,即提高A/D转换的速率是提高系统整体工作速率的关键。

本设计中所采用的增量式数字PID控制算法的设计思想可以应用到有限长单位脉冲响应(FIR)滤波器和无限长单位脉冲响应(ⅡR)滤波器的FPGA设计中,并且同样可以使用流水线优化技术以提高工作速度。同时,由于PLD设计和专用ASIC设计的通用性,在PLD设计平台上所完成的设计可以很自然地过渡到专用ASIC的设计工作中,进一步提高了系统的可靠性和集成度。

评论