应用处理器子系统使SoC设计更容易

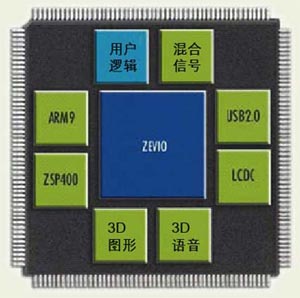

LSI LogIC公司开发的低功耗处理器架构子系统瞄准GPS导航系统、电子玩具、个人媒体播放器以及许多其它低功耗手持应用。Zevio架构提供了一套完整的支持功能和总线互连,设计人员能够很容易地开发SoC解决方案。这种SoC包括一个或多个CPU或DSP内核、视频支持、2D或3D图形、64通道 3D/2D音响引擎、USB端口和NAND闪存接口、 SDRAM,以及双数据速率(DDR)或DDR2 DRAM等IP预验证模块中的功能。IP预验证模块对于开发从ARM和ZSP DSP到视频编解码器、3D图形和2D/3D音响处理器的各种电子消费产品器件十分重要,Zevio架构使得产品从概念到原型只需要花6个月。CPU和 DSP内核可以选择ARM7、ARM9或ARM11,MIPS24K、5Kf和4Ke,以及LSI的ZSP200、400、500和600。

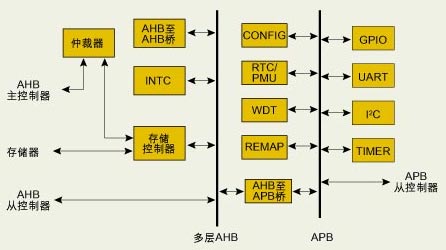

本文引用地址:https://www.eepw.com.cn/article/80117.htm基本资源包括存储控制器、总线仲裁器、中断控制器、实时时钟、定时器和看门狗定时器、I2C 接口、串行UART和一些通用I/O(GPIO)引脚,这些功能占用了多层ARM高性能总线(AHB)。CPU、DSP、A/V核心及相关片上存储器直接连接至多层AHB,总线将多层AHB桥接至另外的AHB主控器和ARM外围总线(APB),其它外围从设备可连接至APB。

3D图形引擎具备可与Sony PlayStation和PlayStation2相媲美的性能水平,它包括独立的几何引擎和光引擎,以及渲染引擎(rendering engine)。3D图形处理器包括的几何引擎和渲染引擎只需要30万门,在75MHz运行时,具有每秒1.5M多边形的峰值性能,采用0.13um工艺,功耗仅为0.25mW/MHz。

图1:Zevio应用处理器架构框图。

3D音响引擎也很节省功耗,在同样的时钟速率下功耗不超过5mW。它包括带MIDI和sound font支持的64语音合成引擎,以及16种3D语音配置。

2D/3D 音响处理器用于有效满足消费产品的音响合成需求。它支持达48路2D语音和16路3D语音,总共64路语音。音响处理器被设计成工作于24MHz,输出为 44.1kHz 16位PCM取样。该处理器仅8万门,采用0.13um工艺技术,功耗低至0.05mW/MHz。

Zevio 架构包括以下外设:4个16位定时器、1个32通道中断控制器、1个8通道DMA控制器、一个看门狗定时器和1个不需要独立电源的实时时钟。存储控制器以系统总线频率的两倍运行,支持低成本16位宽SDRAM接口。先进的电源管理单元(PMU)精确控制时钟,并将逻辑触发减到最少,以降低整个系统的平均功耗。PMU控制片上功率岛(power island),以减少功耗敏感应用的泄漏。

Zevio可编程参考板使系统设计人员可以在芯片开发中,在周期精确级环境评估SoC,以进行早期软件开发,这样软件就可马上用于SoC,大大缩短了产品面市的时间。

LSI Logic不但提供硅IP,还与三个战略伙伴合作:Koto Laboratory提供游戏专业技术,Access公司提供便携式浏览器技术和实时操作系统,而HI公司提供图形应用编程接口及支持。

图2:一个基于Zevio架构的电子玩具SoC。

评论