基于CD4060的硬件看门狗技术

引 言

多年来,围绕着单片机应用系统的抗干扰技术以及其受干扰后的自我恢复,在硬件和软件等方面积累了多种方法,这些方法相互结合,配合使用,有效地提高了系统的可靠性与抗干扰性。

看门狗(Watch Dog Timer,简称为WDT)技术就是最常见的抗干扰技术。看门狗WDT有硬件看门狗和软件看门狗之分,无论是硬件看门狗还是软件看门狗实际上都是一个可清零的定时计数器。如果该定时计数器用MCU芯片外部电路实现,则为硬件看门狗,如果该定时计数器用MCU芯片内部定时器/计数器实现,则称为软件看门狗。

本文介绍硬件看门狗技术,并给出了实用的基于CD4060的硬件看门狗电路。

1 硬件看门狗电路及其工作原理

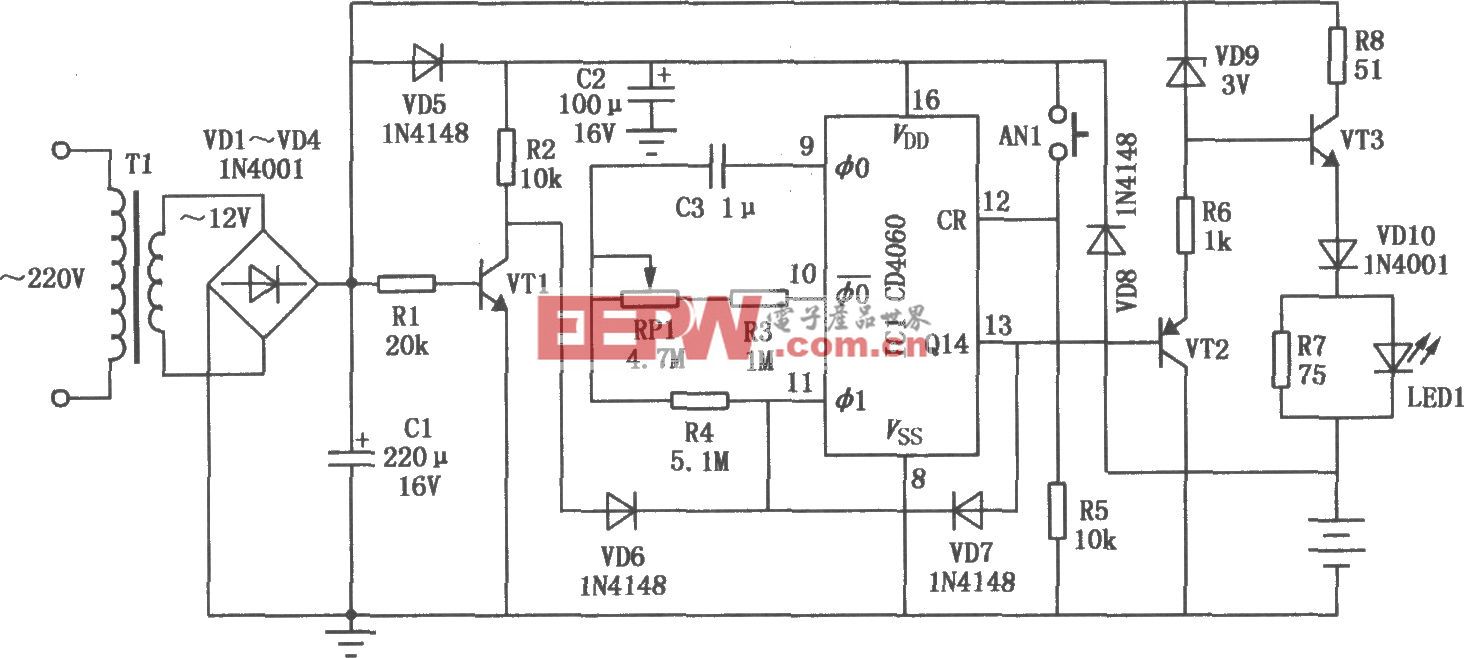

基于CD4060的硬件看门狗电路如图1所示,它是针对工程项目所设计的一个实用电路,并且该电路实际使用情况良好。下面介绍电路的组成及其工作原理。

看门狗电路由14位二进制计数器CD4060和三极管VT1、VT2等组成。

单片机AT89C51的P1.7口设计成输出口,由AT89C51的CPU向看门狗电路发送喂狗信号——正脉冲,在两个正脉冲间隔内,P1.7保持为低电平(此功能要结合软件才能实现,相应的软件设计在下面介绍)。我们知道,单片机AT89C51的I/O口带灌电流负载的能力比较大,每个引脚低电平时的吸入电流为20 mA,带拉电流负载的能力却很小,实测情况是,每个引脚高电平时的输出电流仅25μA,现在P1.7口被设计成带拉电流负载的方式,为了提高P1.7口带拉电流负载的能力,所以,电路中设置了上拉电阻R3。

14位二进制计数器CD4060的计数脉冲由其内部振荡器和外接阻容元件R1、R2、C1组成的电路产生,振荡周期为

T0SC=2.2

评论