基于ADF4106的锁相环频率器研究与设计

摘要:本文由锁相环频率合成器的基本工作原理入手,介绍基于锁相环芯片ADF4106的工作特性,并结合环路滤波器、压控振荡器和射频通路设计出一种输出频率为2GHz的频率合成器,并经过印制板加工及测试,验证实验结果满足设计指标。

本文引用地址:https://www.eepw.com.cn/article/279219.htm引言

频率合成器[1-2]的功能就是给收发机中的变频电路提供频率可编程的本地载波信号,是无线收发机的核心模块之一,其性能对通信系统的通信质量具有重大影响。目前频率合成器主要有直接模拟频率合成技术(DS)、锁相环频率合成技术(PLL)、直接数字频率合成技术(DDS)、混合频率合成技术四种实现方式,其中锁相环频率合成器是射频电路中最常使用的一种结构,相比于其他几种结构,PLL结构能够在有限的功耗限制下合成高性能的载波信号。本文基于锁相环芯片ADF4106设计了一种数字锁相环频率合成器,具有超宽的带宽、较好的噪声特性、快速锁定时间,以及功耗低和体积小等特点,从而被广泛应用于无线通信系统中。

1 锁相环频率合成器的基本工作原理

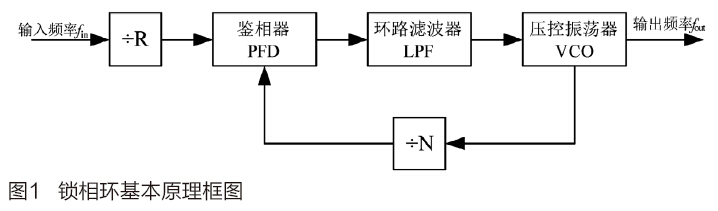

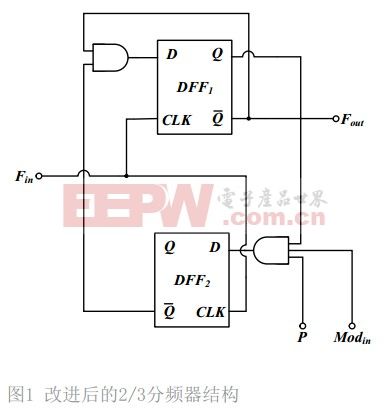

锁相环(PLL)是一个相位误差控制系统,通过将输入信号与压控振荡器(VCO)输出信号之间的相位进行比较,产生相位误差电压经处理后去调整压控振荡器的相位。当环路锁定时,输入信号与压控振荡器输出信号频差为零,相位差不再随时间变化,此时误差控制电压为一固定值,压控振荡器输出频率与输入信号频率相等,即fout=(N/R)*fin。锁相环基本原理框图如图1所示。

锁相环主要结构由VCO、鉴相器(PFD)、分频器和环路滤波器(LPF)组成。其中,PFD主要功能是进行相位比较的,它把VCO输出信号N分频后与输入频率R分频后进行比较,产生误差控制电压。LPF的作用是滤除误差电压中的高频成分和噪声,以保证环路所要求的性能,提高系统的稳定性。VCO受控制电压的控制,使其输出频率向参考信号的频率靠近,两者频率之差越来越小,直至消除频差而相位同步实现锁定。在实际设计中,可以通过程序改变分频比R、N,从而获得需要的稳定输出频率。

2 方案设计与实现

2.1 锁相环芯片ADF4106结构功能介绍

ADF4106是ADI公司生产的集成锁相环频率合成器芯片,利用该芯片可以实现无线收发机上变频和下变频部分的本地振荡。ADF4106由一个低噪声数字PFD、一个精确的电荷泵、一个可编程基准分频器R(14位)、可编程A(6位)、B(13位)计数器和一个双模前置分频器P/P+1组成。A、B计数器和双模前置分频器相连接实现一个分频器N,且N=PB+A。该芯片具有6GHz的频率带宽,2.7V~3.3V的供电电压,独立的电荷泵供电电压,可编程的双模前置分频器P/P+1,其值可取8/9、16/17、32/33和64/65,同时还具有三线串行接口、模拟数字锁定检测、硬件软件低功耗模式等特性。ADF4106同外部LPF和VCO可以组成一个完整的PLL电路。由于ADF4106的宽带特性消除了许多高频系统中倍频器的使用,从而简化了系统结构和降低了成本。

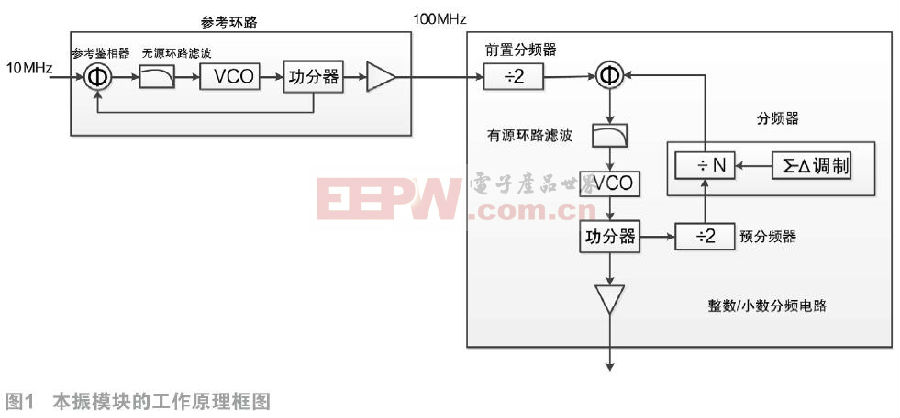

在本文设计中,设计实现2GHz的频率合成器,且要求2GHz频率信号分两路输出,并保证其中一路输出信号功率达到13dBm。该电路主要由ADF4106、LPF、VCO和射频信号输出部分组成。根据图1,选取输入信号频率fin=10MHz,该信号在进入ADF4106的Refin引脚前通过一个T型匹配网络来实现阻抗匹配。为了保证PFD输入信号频率为1MHz,需要通过编程设定基准分频器R的值为10,分频器N的值为2000。

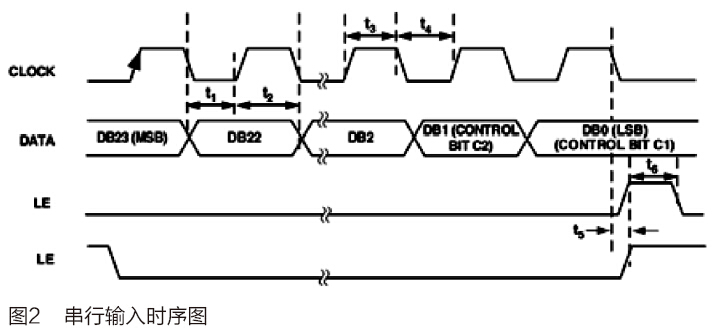

ADF4106具有一个简单的SPI兼容串行接口向器件引脚CLK、DATA、LE写数据,当LE为上升沿时,将CLK每个时钟上升沿存储到寄存器中的24位数据送入合适的锁存器中。串行输入时序图如图2所示。

adc相关文章:adc是什么

分频器相关文章:分频器原理 功分器相关文章:功分器原理 鉴相器相关文章:鉴相器原理 锁相环相关文章:锁相环原理

评论