LPCVD TEOS 厚度的机械应力对闪存循环性能的影响

摘要:本文研究了闪存循环(耐久性)与LPCVD(低压化学气相沉积)制程应变的相关性。所沉积的充当S/D植入物牺牲氧化层的12.5nm SCTEOS在后面的工序中会被去除。然而有趣的是,通过应力记忆技术(SMT),我们发现对通道产生的应力会影响闪存循环(耐久性)性能

【关键词:耐久性/循环、LPCVD TEOS、应力】

引言

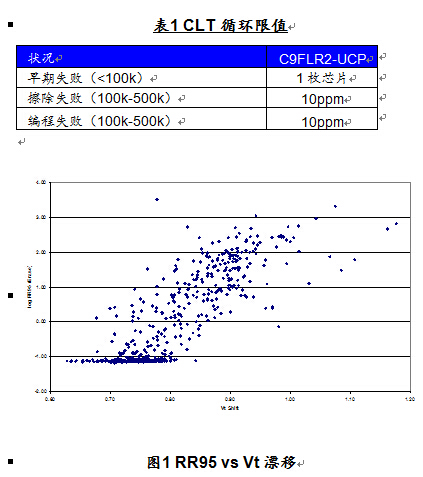

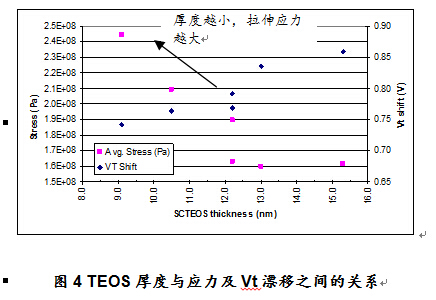

2008年2月,有报道称,嵌入式闪存UCP遇到擦除原始比特失败率(RR)高于CLT(置信度检测)S5循环中10ppm的限值(查阅表1获取CLT限值)问题。这会造成晶圆报废,也不利于平稳提升产量。为了探寻问题的根本原因、以及有助于获取更多裕度的最佳工艺条件,相关人员开展了许多研究和评估。循环原始比特失败率的另一种响应是Vt(阈值电压)漂移(Vt EOL - Vt BOL),我们发现RR(对数)和Vt之间存在密切的关系——如图1所示。

本文研究了LPCVD TEOS薄膜应力对闪存循环的影响,目的是以较少的Vt漂移获得更多循环制程裕度。SiN(HTN)薄膜引起的机械应力会影响闪存循环性能是众所周知的事实,这个现象已经得到了广泛的研究。但针对LPCVD TEOS薄膜应力的研究几乎没有。因此,本文将借助实验结果进一步探讨LPCVD薄膜的影响。

三个DOE批次的LPCVD TEOS薄膜厚度清楚地表明,循环Vt漂移与TEOS薄膜厚度之间有密切的联系。我们发现循环Vt漂移与LPCVD TEOS薄膜厚度之间的关系与薄膜的机械应力有关。这一点可以用制程应变也就是所谓的应力记忆技术(SMT)解释。退火时应力会从TEOS薄膜转移到通道上[1]。因为与基片表面平行的压缩应力,存储单元中的编程/擦除(P/E)循环会产生更多界面陷阱,从而导致Vt漂移增大。而将LPCVD TEOS薄膜厚度从12.5nm降至11.5nm,可以获得额外的约20mV Vt漂移的循环制程裕度。

实验方法

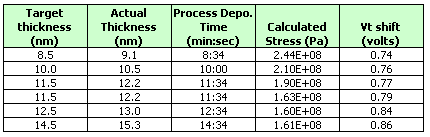

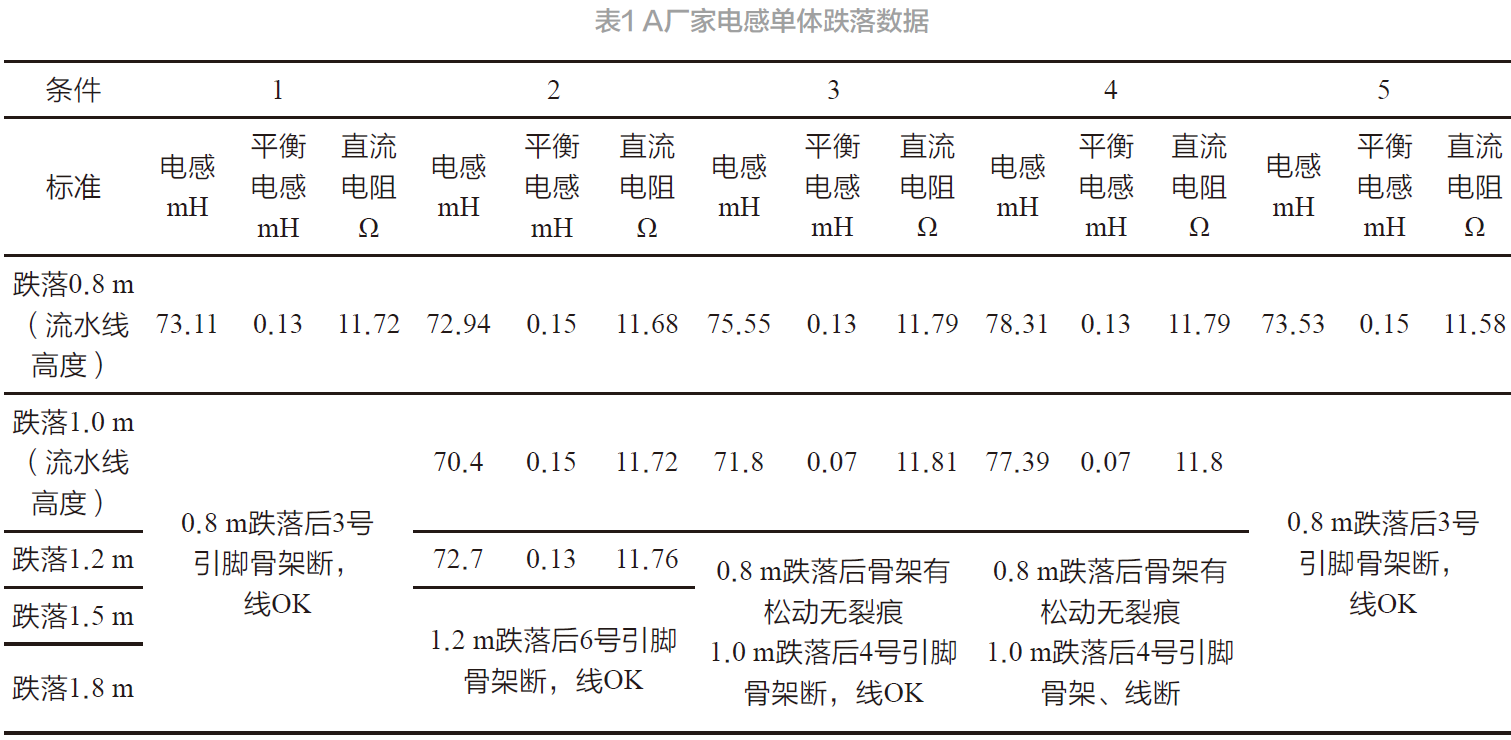

为了研究不同LPCVD TEOS薄膜厚度对Vt漂移性能的影响,我们根据表1中所示的目标厚度要求相应地调整工艺沉积时间,以在DOE晶圆上沉积不同厚度的TEOS薄膜。通过利用E+H MX204-8-37非接触式晶圆测量仪,获取DOE晶圆上晶圆基片厚度、TEOS制程之前的晶圆弯曲度(前弯曲度)、以及TEOS制程之后的晶圆弯曲度(后弯曲度)测量数据。然后利用该信息计算沉积不同厚度的TEOS薄膜层对DOE晶圆造成的应力。

结果和讨论

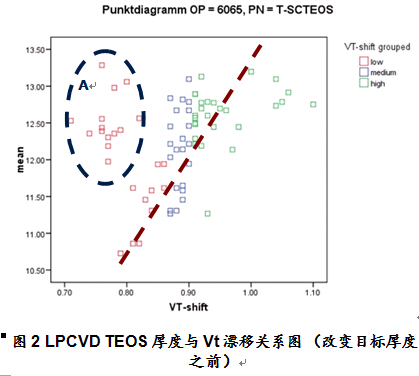

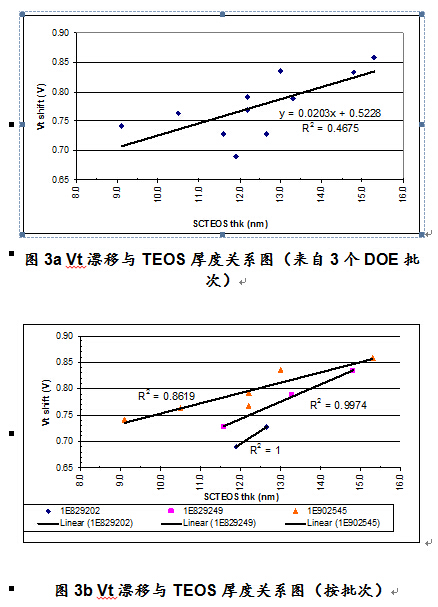

图2表明,LPCVD TEOS薄膜厚度与Vt漂移之间具有关联性——假设A区的数据点可能受到其他制程的影响。接下来,开展LPCVD TEOS薄膜厚度实验验证数据。来自3个DOE批次的实验结果表明,LPCVD TEOS薄膜厚度与Vt漂移之间存在关联:TEOS薄膜厚度越小,Vt漂移越小。对每个DOE批次展开进一步研究发现,如图3b所示, Vt漂移对薄膜厚度的敏感度因批次而异,它证实了之前作出的Vt漂移可能受到除LPCVD TEOS薄膜厚度之外的其他制程影响这一假设。然而,3个DOE批次的实验数据在LPCVD TEOS厚度对Vt漂移有影响这一点上是一致的。

发现LPCVD TEOS厚度与闪存循环之间的关联性是非常有益的,因为这个被沉积的只是充当S/D植入物牺牲氧化层的12.5nm TEOS薄膜将从存储单元上去除。因为SiN(HTN)薄膜应力对闪存循环(耐久性)的影响已非常明了,我们就对不同厚度的LPCVD薄膜应力展开评估以便加强了解。如图4所示,LPCVD TEOS薄膜厚度越小,拉伸应力越大,从而使得Vt漂移变小。Vt漂移与LPCVD TEOS薄膜厚度之间存在这种关系是因为,在LPCVD TEOS薄膜沉积时,它会引起制程应力,也就是所谓的应力记忆技术(SMT)——图5。拉伸应力越大,产生的界面陷阱越少,循环Vt漂移也越小。该论点得到参考文献[2]的进一步证实,它利用电荷泵(CP)法发现,因为与基片表面平行的压缩应力,存储单元中的编程/擦除(P/E)循环会产生更多界面陷阱(请参见图6)。而压缩薄膜上Tox/Si基片之间俘获的界面越多,Vt漂移就越大。

评论