ISE时序约束笔记2——Global Timing Constraints

问题思考

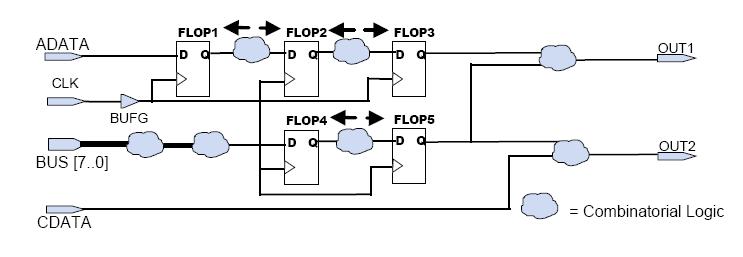

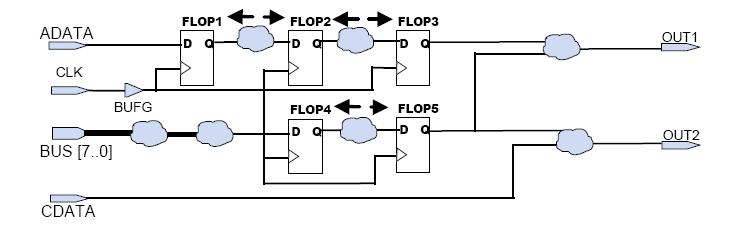

本文引用地址:https://www.eepw.com.cn/article/269396.htm单一的全局约束可以覆盖多延时路径

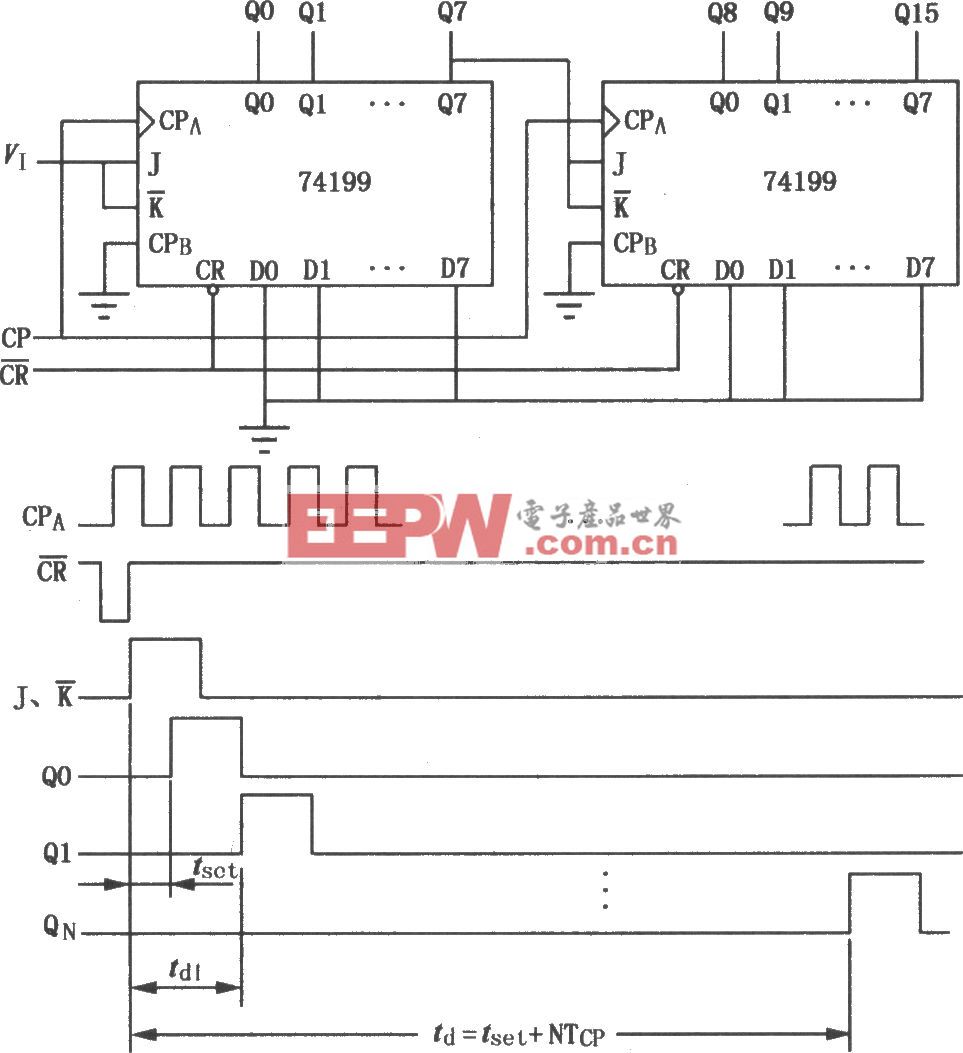

如果箭头是待约束路径,那么什么是路径终点呢?

所有的寄存器是否有一些共同点呢?

问题解答

什么是路径终点呢?

——FLOP1,FLOP2,FLOP3,FLOP4,FLOP5。

所有的寄存器是否有一些共同点呢?

——它们共享一个时钟信号,约束这个网络的时序可以同时覆盖约束这些相关寄存器间的延时路径。

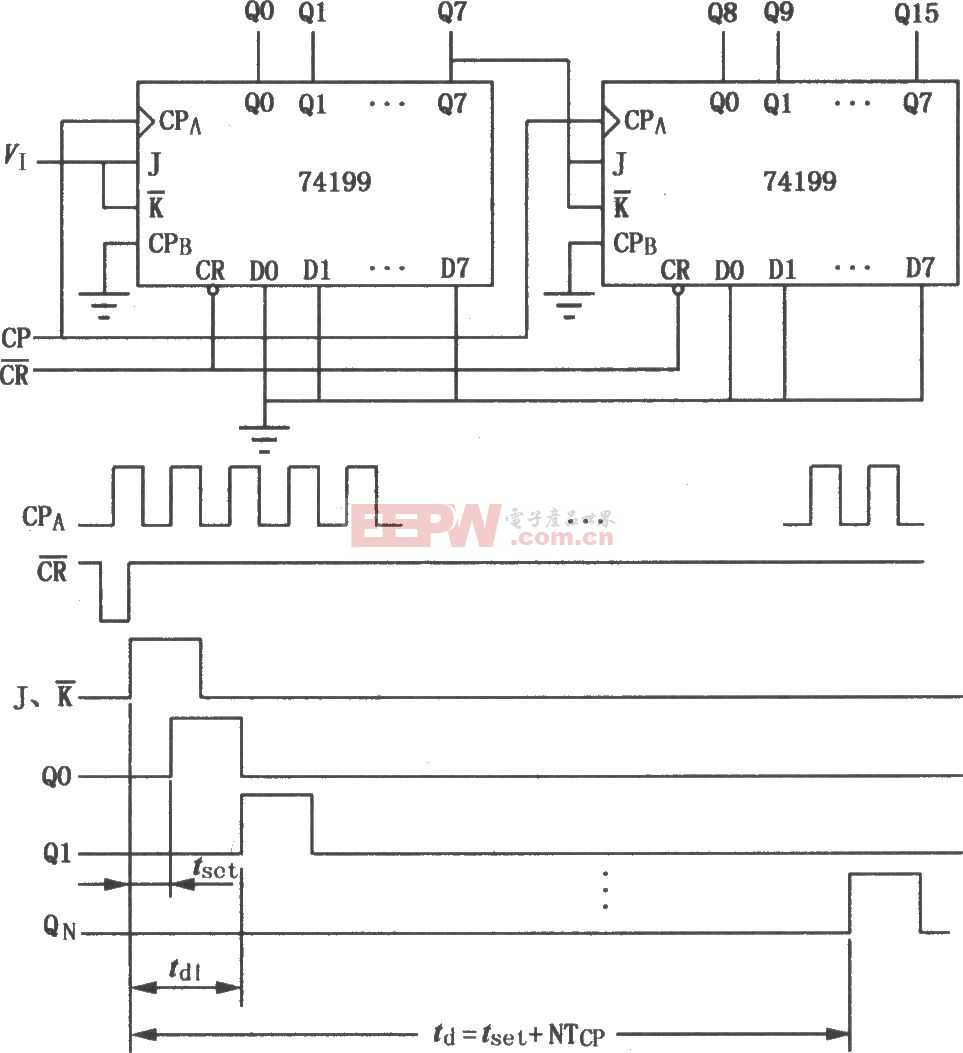

周期约束

周期约束覆盖由参考网络钟控的的同步单元之间的路径延时。

周期约束不覆盖的路径有:input pads到output pads之间的路径(纯组合逻辑路径),input pads到同步单元之间的路径,同步单元到output pads之间的路径。

周期约束特性

周期约束使用最准确的时序信息,使其能够自动的计算:

1. 源寄存器和目的寄存器之间的时钟偏斜(Clock Skew)

2. 负沿钟控的同步单元

3. 不等同占空比的时钟

4. 时钟的输入抖动(jitter)

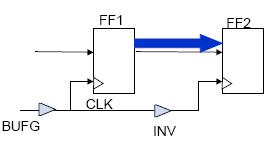

假设:

1. CLK信号占空比为50%

2. 周期约束为10ns

3. 由于FF2将在CLK的下降沿触发,两个触发器之间的路径实际上将被约束为10ns的50%即5ns

时钟输入抖动(Clock Input Jitter)

时钟输入抖动是源时钟的不确定性(clock uncertainty)之一

时钟的不确定时间必须从以下路径扣除:

——周期约束建立时间路径

——OFFSET IN约束的建立时间路径

时钟的不确定时间必须添加到以下路径中:

——周期约束保持时间路径

——OFFSET IN约束保持时间路径

——OFFSET OUT约束路径

Pad-to-Pad约束

——不包含任何同步单元的纯组合逻辑电路

——纯组合逻辑延时路径开始并结束于I/O pads,所以通常会被我们遗漏而未约束

评论