数字无线实时视频通信和拍摄系统设计

引 言

本文引用地址:https://www.eepw.com.cn/article/260801.htm本无线系统基于高速率射频芯片的视频通信系统,且具备即时拍摄功能;在视频(连续)模式下采用QQVGA的分辨率传输视频数据,为160×120(@13fps),基本上能达到实时视频的日的。在实际应用中,用户可以在接收端的LCD中观看(远处的)发送端附近的景物。当见到感兴趣的景物时,按下按钮稍等片刻,即可得到1.3M像素的图像,方便实用。为简化设计,该系统只用了8位色深和RGB的数据格式,且未采用CCD摄像芯片,也未使用FPGA芯片进行逻辑控制,节省了成本。

下面着重讲述以TMS320VC5402 DSP为控制核心的无线视频通信系统,详细描述DSP与摄像芯片以及DSP与射频芯片这两大部分的接口设计,分析设计中的要点,最后给出部分DSP汇编代码。

1 无线实时视频系统的组成与工作原理

1.1 OV9640摄像芯片简介

OV9640是美国OmniVision公司推出的高性能CM0S图像传感器芯片.支持130万像素的图像拍照和多种分辨率,包括l280×960、VGA、QQVGA、CIF、QCIF等及多种数据输出格式,如Raw RGB、YUV(4:2:2)、YcbCr(4:2:2)等;支持8位或16位数据输出;通过SC-CB接口对其编程,可实现图像处理的各种基本功能,譬如曝光控制、白平衡、色彩饱和、伽马控制等;芯片电压要求低,可应用于嵌入式移动设备。

1.2 nRF24L01射频芯片简介

nRF24L01是挪威Nordic公司的单片无线GFSK收发芯片,工作于2.4~2.5 GHz的ISM频段,无线传输率最大为2Mbps,与MCU采用SPI接口进行控制和数据传输。相比其上一代产品nRF2401,nRF24LOl的性能更为优越,功耗更低。它最多能支持6路数据通道,且每条通道均支持Enhanced ShockBurst(ESB)技术,具备自动应糟(AACK)和自动重发(ART)功能,减轻了MCU的负担,降低了无线数据的丢包率,提高了双向传输的效率。在开启ESB的情况下,nRF24L0l发送完数据包后将自动切换到接收模式以等待对方的应答.并会根据寄存器的设定来实施自动重发。

1.3 系统硬件电路

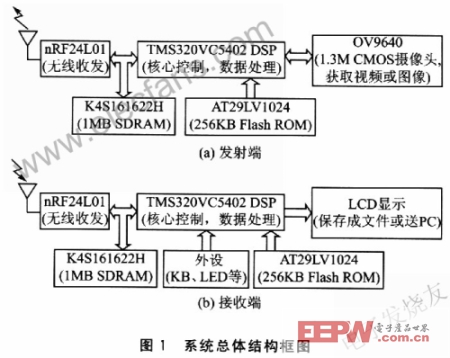

硬件电路由发送(获取)端和接收(存储显示)端两大部分组成,通过高速RF芯片实现在2.4 GHz频段的无线链接。发送端以TMS320VC5402 DSP作为控制核心,OV9610摄像头芯片作为视频(或图像)获取前端,AT29LV1024 Flash ROM作为DSP自举程序存储芯片,K4S161622H IMB容量的SDRAM作为程序运行空间以及视频数据缓冲,视频数据最终通过射频芯片nRF24LOl发射出去;接收端的硬件结构基本上与发送端一致,将前端的OV9640改换成后端的LCD显示即可。整个系统的总体结构框图如图1所示。

1.4 系统工作原理和流程

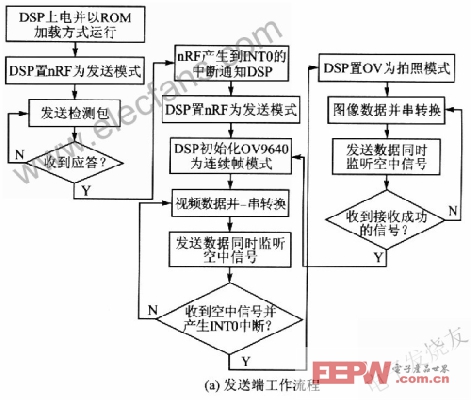

1.4.1 发送端工作于视频流模式

发送端由DSP作为核心控制芯片。DSP上电初始化,通过BootLoader把Flash ROM中的代码加载到SDRAM中,实现系统的高速运行以加快数据的处理速度,并将HPI接口设定为通用I/O。然后,通过McBSPO缓冲串口将 nRF24L0l设定为发送模式,把含有预定地址的数据包发送出占以检测接收端,nRF24L01会自动切换到等待应答信号的模式。若存在正确的接收端 (地址相符),则nRF24L01通过INTO中断通知DSP,使DSP重新将nRF24L01设定为发送模式,并立即对OV9640初始化,通过 McBSPl缓冲串口来实现SCCB总线,启动摄像头并设定为连续帧模式。此时的分辨率为标准QQVGA,即160×120(@8bit),最后,DSP 把从D[7:O]获得的8位并行数据转化为串行格式,通过SDRAM缓冲和McBSP0送给nRF24L01,将视频数据发射出去。若没有检测到正确的接收端(没有INTO中断发生),则DSP会一直等待INTO发生或直到用户关闭电源。

1.4.2 发送端工作于拍摄模式

在视频流传输过程中,nRF24LOl可以同时监听空中信号并自动应答。若收到来自接收端的拍照通知(按下按钮),则把OV9640设定为标准拍摄模式,分辨率为l280×960(@8bit)。然后,DSP将nRF24L01设定为发送模式,并将此时的帧数据发送出去。图像数据发送完成并等到接收确认信号后,系统将重新回到视频流模式。若接收不成功,则nRF24LOl的自动重发功能将确保数据传输的完整性。

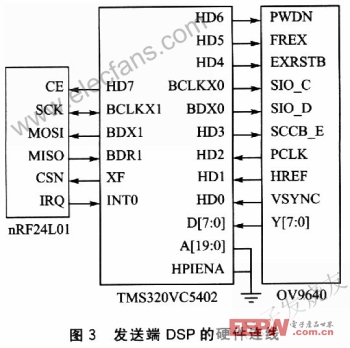

1.4.3 接收端的工作流程

接收端上电初始化的情况基本与发送端一致,但要将nRF2dL01(按预定地址)设定为接收模式以接收检测信号。检测到相符的地址后,nRF24L0l的自动应答功能会发送应答信号给发送端以确认收到信号,此时双方“握手”成功。接着,通过INTO中断通知DSP,使得DSP重新将 nRF24LOl设定为接收模式以接收来自发送端的连续视频流,并且打开LCD模块准备显示视频。最后DSP通过SDRAM缓冲视频流,送给LCD显示 (若LCD等其他后端模块为并行接口,则需要将数据转化成并行数据格式)。至此,系统已经能实现实时视频数据的无线传输,实时视频流的分辨率为 QQVGAl60×120(@13fps)。

在视频流的显示过程中,若用户按下拍照按钮,则产生INTl中断通知DSP,DSP会将nRF24LOl设定为发送模式并发送拍照通知信号。收到应答信号后,nRP24L0l返回接收模式准备接收图像数据,接收完成后会自动发送确认信号以表示图像数据接收成功。最后,DSP将图像数据交由后端模块处理。至此.系统实现了图像的无线拍摄功能,拍照效果为1280×960(@130万像素),基本上能满足拍照要求。

视频系统接收端和发送端的工作流程如图2所示。

2 DSP的接口设计

2.1 DSP与OV9640的接口设计

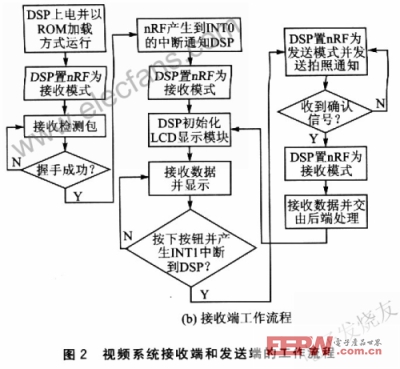

该芯片使用OmniVision公司自主开发的SCCB总线进行控制,使用三线连接。其中SCCB_E为串口允许/禁止信号线,SIO_C和 SIO_D分别为串口时钟线和数据线。系统中仅对OV9640进行控制而不需要获知其状态,采用DSP的McBSPO端口进行连接,其中HD3用于打开串口,BCLKX0和HDX0分别用于发送时钟信号和控制数据。具体的硬件连线如图3所示。

值得注意的是:

①使用DSP的HPI接口连接OV9640时,为了获得场频、行频和8位视频输出等信号,DSP的HPIENA引脚必须下拉,使得HD[7:0]能配置为通用I/o接口,才能实现对OV9640的启停或工作模式控制。

②通过修改OV9640的寄存器COMC,将输出大小设定为1280×960或者QQVGA。

③修改寄存器COMH,将输出格式设定为8位的RGB格式,并设定为Master方式。

④FREX为连续帧模式的允许/禁止信号,但默认为禁止。应配置DSP的HD4引脚,将其电平拉高,然后再用HD3将EXPSTB引脚置高以实现连续帧的数据输出;将FREX置低即可返回到(单帧)拍摄模式。

⑤计算数据传输率。该芯片输出并行8位图像信号以及场频、行频同步信号,视频中的l帧图像(160×120)的大小是:

160×120×8=153600位/帧

如果以nRF24L01最大的发送速度2Mbps计算,则每秒可发送

2000000/153600≈13帧

即本系统能以160×120(@13 fps)的速度传输视频信号。

⑥输出数据的并一串转换。

OV9640输出8位并行数据,而nRF24L01为串行接口,因而需要将并行数据串行化。8位并行数据格式为HREF、Bll、G2l、B22、 G12……,HREF、G21、R22、G23、R24……。通过编程约定发送端与接收端的时序,可将从HD[2:0]得到的PCLK、HREF和 VSYNC信号略去而无须计入无线传输之列。所以串行化时,将每次从D[7:O]读入的8位数据由高位到低位依次按顺序放进SDRAM缓冲中,再传给 nRF24LOl发送出去即可。

2.2 DSP与nRF24L01的接口设计

2.2.1 设计要点

DSP使用McBSPl与该芯片直接连接。其中CSN为SPI片选引脚,低电平有效,用DSP的XF引脚与CSN引脚连接;CE为收发模式选择引脚,用HD7进行高低电平控制。其他引脚的连线如图3所示。在编程时需要注意:

①每次通过SPI向nRF24L01发送指令前,必须使CSN得到一次由高到低的电平跳

变,即每次执行指令后,都要将CSN置高才能继续发送下一条指令。

②nRF24L01的SPI为下降沿锁存数据,故应将McBSPl配置成“有延时的下降沿”。

③IRQ引脚为低电平有效,每次产生到DSP的中断必须写“l”来清除。

④若发送端需要接收应答,则应当配置数据通道O来接收应答信号,且接收地址(RX_ADDR_PO)应当与发送地址(TX_ADDR)一致。

⑤芯片必须经过Standby模式才能进入TX或RX模式,故在TX和RX模式之间切换时应先将CE拉低以进入Standby模式。

⑥写寄存器的指令只能在Powerdown或Standby模式下执行,故在修改寄存器值前也应当将CE拉低。

⑦以下的2.2.2和2.2.3均未开启AACK和ART功能。因为系统在连续视频流方式运行时,只要求得到高数据传输率以满足实时性,而并不需要纠错重发。但在拍摄方式下,则应该打开这两项功能,以确保图像数据的完整性。

2.2.2 ESB发送数据

①将配置位PRIM_RX置低;

②保持CSN为低电平,送入接收端的地址(TX_ADDR)和数据(TX_PLD);

③将CE置高,开启数据发送;

④数据发送完毕,产生TX_DS中断;

⑤CE置低,可进入Standby模式。

2.2.3 ESB接收数据

①配置位PRIM_RX置高,CE置高,则130μs后,nRF24L01开始监听空中信号;

②收到合法的数据包后RX_DR产生中断;

③状态寄存器中的RX_P_NO记录所接收的数据通道;

④CE置低可进入Standby模式;

⑤MCU通过SPI得到数据。

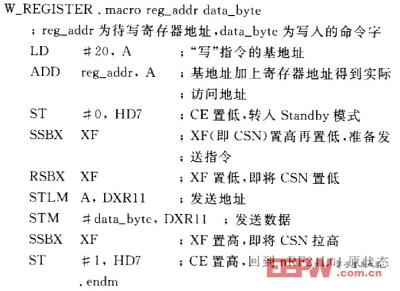

2.2.4 部分程序示例

(1)写nRF24L01寄存器

(2)读nRF24L01寄存器

(4)发送数据

假设在(3)中已经将数据宽度定为32字节,则W_TX_PAYLOAD.macro tx_start_byte

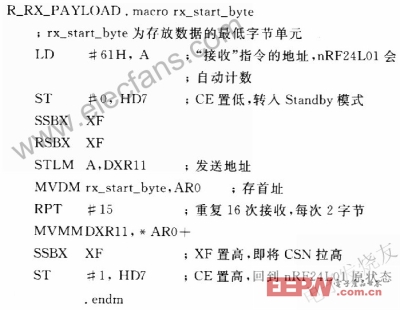

(5)接收数据

同样假设在(3)中已经将数据宽度定为32字节,则R_RX_PAYLOAD.macro rx_start_byte

结语

以DSP为核心的无线通信系统,在硬件上采用了高速低功耗的无线射频芯片nRF24L01、高性能的TMS320VC5402数字信号处理芯片以及多功能的摄像芯片OV9640,使其能够实现强大的视频通信功能,并且在软件层次上优化设计,以缩短等待延迟和降低功耗。本系统的扩展性很强,例如,加装语音编解码芯片即可实现无线音频和视频的同步传输;加装视频压缩芯片可以提高帧速率;同时使用两片(或两片以上)的无线收发芯片能实现全双工,更能提高空中数据传输率;改用高分辨率的摄像芯片即可获得更优质的视频和图像效果等,但也提高了硬件连线和软件设计的难度。

总之,无线视频和无线图像通信是未来无线领域的重点发展方向。本设计实现了在一定帧速率下的实时QQVGA视频传输,对今后同类系统的设汁有一定的参考价值。

评论