什么是PCI总线?其接口芯片的应用

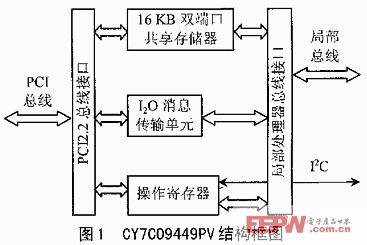

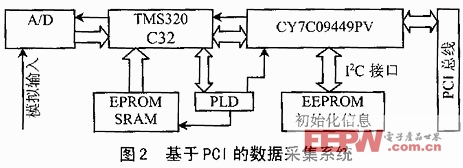

PCI (Peripheral Component Interconnect)总线是一种高性能局部总线,是为了满足外设间以及外设与主机间高速数据传输而提出来的。在数字图形、图像和语音处理,以及高速实时数据采集与处理等对数据传输率要求较高的应用中,采用PCI总线来进行数据传输,可以解决原有的标准总线数据传输率低带来的瓶颈问题。 1 PCI局部总线特点 * 传输率高:在33MHz的时钟频率下,对于32位的PCI总线,峰值数据传输可以达到132MB/s;64位的PCI总线可达264MB/s。对于64位的66MHz时钟的PCI总线,可以达到528MB/s,远远大于标准ISA的5MB/s和EISA的33MB/s传输率。 *线性突发传输:减少了地址操作,更有效地利用总线的带宽来传输数据,可以确保总线满载数据。 *采用独立于处理器的结构:图为PCI总线开发的设备是针对PCI的,不受处理器的限制,所以PCI设备的设计独立于处理器的升级。 *自动配置功能:每个PCI设备有256字节的配置寄存器,可以实现设备的即插即用。 *软件透明:在与PCI设备通信时,软件驱动程序使用相同的命令集和状态定义。 2 PCI接口的两种设计方法 PCI 接口的设计必须符合PCI总线规范定义的电气特性和时序要求。有两种PCI接口的实现方案:使用可编程逻辑器件(FPGA或CPLD)和专用PCI接口芯片。使用可编程逻辑器件,可以选择实现部分PCI规范的一个子集,这种方法比较灵活,但开发难度大,开发周期长。采用专用PCI接口芯片,可以缩短开发周期,降低开发难度。 3 CY7C90449PV介绍 CY7C09449PV 是Cypress公司推出的PCI主/从接口芯片,符合PCI2.2规范,可以直接与很多微处理器进行无缝连接。CY7C9449V提供16KB的双端口共享存储器(SRAM),用来在PCI总线和局部处理器间传输数据;I2O消息传输单元具有4个32位FIFO,用来实现消息队列和中断功能;局部总线时钟最大50MHz,单一3.3V电源供电;对3.3V和5V的PCI信号兼容,使用160引脚的TQFP封装。 3.1 CY7C09449PV结构 CY7C09449PV的结构如图1所示。 3.2 功能模块介绍 CY7C09449PV 提供64字节的PCI头标区配置寄存器空间。其中Vender ID、Device ID、Revision ID、;Header Type、Class Code用于设备的识别。命令寄存器(Command)包含设备控制位,包括允许存储器读写响应、I/O读写响应等。状态寄存器(Status)用于记录 PCI总线相关事件的状态信息。基址寄存器0(BAR0)提供设备在PCI存储空间起始地址,31~15可读写,通知系统BIOS此设备所要求的PCI存储空间为32KB,任何对31~15位与BAR0相符合的PCI存储空间访问的,CY7C09449PV都会影响并接受传输。基址寄存器1(BAR1)是 CY7C09449PV的I/O指针空间的地址。 CY7C09449PV 提供PCI总线接口、局部处理器总线接口和I2C串行EEPROM接口,以及内部16KB双端口SRAM、I2O消息传输单元和控制寄存器。数据的传输可以在PCI总线和局部处理器总线间进行。PCI总线和局部总线都能通过操作寄存器对I2C接口进行操作。 PCI 总线和局部处理器总线间可以通过共享的双端口存储器进行数据交换。由于共享存储器是“临界资源”,CY7C09449PV在仲裁寄存器(CRB_FLAGS)中,为PCI总线和局部处理器部各提供了4个仲裁档志位(L0,P0,L1,P1,L2,P2,P3,P3),来对共享存储器进行并发互斥访问。对了实现线性突发传输,提供了DMA控制寄存器,PCI总线和局部处理器总线都能通过DMA控制寄存器,来启动突发传输。为了保证对DMA 控制器的互斥访问,DMA控制寄存器也提供了仲裁标志位。CY7C09449PV为局部处理器提供了一个映射到整个PCI地址空间的8KB存储器窗口。通过这个窗口,局部处理器可以不经过共享存储器,直接对PCI地址空间进行访问,直接访问寄存器(DAHBASE)负责对这个窗口的操作。 CY7C09449PV的I2O消息传输单元具有符合智能I/O(Intelligent I/O)1.5规范的消息队列和断功能,由4个深度为32的32位FIFO(Inbound Free/Post,Outbound Free/Post)和共享存储器来实现。这4个FIFO也能用作通用FIFO。 PCI总线和局部处理器间的消息也能通过邮箱来传输。主机通过写Host to Local Data Mailbox(HLDATA)邮箱寄存器,向局部处理器传送消息数据,并产生中断标志位,等局部处理器读取消息数据后,中断标志位自动复位。局部处理器能通过写(Local To Host Data Maibox)邮箱寄存器,向主机发送消息数据,并产生中断标志位。主机读取消息数据后,标志位自动复位。 通过I2C接口连接EEPROM,可以保存CY7C09449PV的初始化数据。这些数据包括PCI总线和局部处理器总线的配置信息。在复位完成后, PY7C09449PV在响应PCI总线和局部总线交易以前自动下载这些数据,进行初始化操作。通过I2C控制寄存器组可以对I2C端口进行读写。I2C 控制寄存器组包括3个寄存器:I2C命令寄存器(NVCMD)、I2C读数据寄存器(NVREAD)、I2C状态寄存器(NVSTAT)。 CY7C09449PV 的中断控制器为PCI总线和局部处理器总线分别提供了独立的中断掩码和命令/状态寄存器:HINT(主机中断控制和状态寄存器)、LINT(局部处理中断控制和状态处理器)。中断源有:DMA完成、邮箱、FIFO非空、FIFO溢出等,以及1个外部中断引脚。内部资源如表1所列。 4 基于PCI与C32数据采集系统的设计方案 C32是一种32位的浮点DSP,具有较高的性价比,在实时数据采集与高速信号处理中得到了广泛的应用。使用CY7C09449PV作为接口芯片,可以实现PCI总线与基于C32的DSP系统的连接。 将CY7C09449PV 的RSTOUTD引脚与C32的复位信号相连,可以实现主机对C32进行复位。I2C接口引脚要接2.2KΩ到10kΩ的上位电阻。接口输入引脚在不用时,要上拉到高电平或接地。图2中的PLD实现C32对CY7C9449PV和A/D转换器的片选,以及C32的复位BOOT LOADER所需的信号逻辑。EPROM存储C32程序,SRAM存放数据和运行时的程序,EEPROM存入CY7C09449PV的初始化信息。 系统结构如图2所示。 采集到的数据有两种方案进行传输,使用FIFO或DMA。FIFO传输可以保证顺序的传输,但传输效率低,适用于速率要求较低的应用。使用DMA进行传输,能充分利用PCI总线PCI总线的突发传输能力,适用于对传输率要求较高的情况。共享存储器分为模块A和模块B。DSP先把采集到的数据写入模块A,等数据写满后,启动模块A的DMA传输;同时将接下来采集到的数据写入模块B,等模块B数据装满后,启动模块B的DMA传输,这样循环下云,可以使数据的采集和DMA传输并行进行。

表1 CY7C9449PV内部资源存储映射存储模块 偏移地址[14:0] 大小/KB I2O寄存器

操作寄存器

保留空间

PCI直接访问窗口

共享双端口存储器0x0000-0x03FF

0x4000-0x07FF

0x0800-0x1FFF

0x2000-0x3FFF

0x4000-0x7FFF1

1

6

8

16

评论