双核DSP片TMS320VC5421并行引导方案

1引言

本文引用地址:https://www.eepw.com.cn/article/257224.htm TMS320VC54211、2(以下简称VC5421)是TI公司推出的一款双核定点DSP芯片,它拥有两个DSP子系统,每个子系统都有一个DSP核,并且均有独立的数据和程序存储空间,可以进行两核之间的通信,并且两个子系统共享一套片外总线。

此外,每个子系统各自拥有2k 16bit字的片内ROM,并存储有Bootloader程序。当DSP芯片上电或复位时,两个DSP核可分别启动自身独立的Bootloader程序,以实现用户程序的上电自举。

双核DSP自启动和单核DSP自启动的实现方法有较大的差别,这一点在DSP系统设计中需要特别注意。本文对双核DSP芯片VC5421的引导模式进行了深入的分析和研究,给出了使用16位并行引导模式进行双核DSP引导的实现方案。

2 TMS320VC5421的Boot模式

其中16位并行引导模式是通过片外存储器接口(EMIF)以DMA方式将代码从16-bit字宽的片外数据存储器搬移到片内程序存储空间;

8位并行引导模式则是通过片外存储器接口(EMIF)以DMA方式将代码从8-bit字宽的片外数据存储器搬移到片内的程序存储空间;

而串行EEPROM引导模式主要是通过多通道缓冲串口2(McBSP 2)从主设备中搬移代码并实现上电自举。

和54系列中其它芯片不同的是,VC5421片内ROM中的Bootloader程序并不支持HPI、并行I/O和标准串口模式的自启动方式。在其所支持的三种boot模式中,16位并行引导模式是最常用的。本文对这种模式进行了深入分析,给出了使用该模式进行双核DSP程序引导的方案,并通过实验验证了该方案的正确性。

2.1 并行引导模式的选择

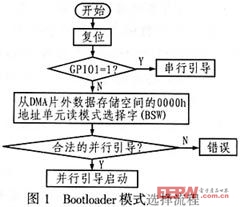

VC5421的两个DSP核在DSP芯片上电或复位时,到底以哪种模式实现上电自举,主要由两个核的公共引脚XIO和各自的GPIO0/ROMEN、GPIO1引脚决定。当XIO为0(低电平)时,将不从ROM引导,也就是说,将不使用VC5421片内ROM中的Bootloader程序实现上电引导,而是用HPI模式实现上电自举;当XIO为1(高电平),GPIO0/ROMEN为0时,将使用片外存储器中用户自己编写的Bootloader程序实现上电自举;当XIO为1 GPIO/ROMEN为1 GPIO1为0或1时,将分别使用并行或者串行引导模式实现上电自举。因此,在实施相应的上电自举前,必须将引脚状态设置正确,以保证Bootloader程序按预定的模式执行。Bootloader模式的选择流程见图1。

当Bootloader程序检测到并行引导模式时,程序将以DMA方式从片外数据存储区的0000h单元取出模式选择字(BSW)来进一步决定是8位还是16位的并行引导模式。10AAh意味着选择了16位并行引导模式,而如果选择8位并行引导模式,取出的两个字节将是08h和AAh。之后,程序将按照Boot表进行加载。图2是并行引导模式的选择流程。

2.2 16位并行引导模式的Boot表

Bootloader程序要搬移的代码必须组织成一定的格式,这就是Boot表。16位并行引导模式的Boot表如表1所列。

表1 16位并行导模式Boot表

此外,需要注意的是,由于在多数程序中都有跳转指令或循环指令,所以,Boot表中的程序入口地址必须和程序的cmd文件中分配的地址保持一致,也就是说,当在CCS中进行调试时,如果程序Load到5000h,Boot表中的程序入口地址就应该是5000h。

2.3 Boot表的生成

Boot表可由hex500格式转换工具生成,也可以自己编写一个文件格式转换程序来把.out文件转换成所需的文件格式。本设计通过编写一个C++程序来将.out文件转换成.hex文件,然后再在文件的开始处增加相应的标志位和寄存器设置字,从而形成完整的Boot表。

3 VC5421片外总线冲突的解决方案

由于VC5421是双核DSP,每个核有各自的存储空间和Bootloader程序,但两核共享一套片外总线和一个XIO引脚。这样,当两核的复位引脚A_RS和B_RS同时收到复位低电平信号时,将同时申请片外总线的控制权。这就造成了申请片外总线的冲突。而且Bootloader程序总是检查该核有没有片外总线的控制权,如果没有,将循环检查直到取得片外总线的控制权。为了避免这种情况的发生,应该以合理的顺序给两个核上电。

由于VC5421中A核带有用来控制时钟频率的锁相环电路,所以应该先对A核进行复位,再启动A核,然后利用A核的用户程序来控制B核的复位,以实现两个核的启动。

根据系统需要,本设计使用Altera公司的CPLD芯片来产生各种控制信号。其电路连接示意图如图3所示。A核的复位信号A_RS由CPLD芯片直接给出,并在系统上电或复位的同时对A核进行复位。而B核的复位信号B_RS则通过CPLD映射到DSP的I/O空间0000h地址单元的第6位:B核复位控制位(在系统复位后值为0)如图4所示。在A核启动后,通过用户程序写B_RS位可为B核提供复位信号。

4 VC5421的并行引导自启动操作

4.1 用户程序的搬移

两个DSP核要完成各自的功能,执行的用户程序是不尽相同的,而且A核的用户程序还要控制B核的复位,因此两个DSP核的Boot表内容是不同的。由DMA方式内部存储器图可知,程序空间的第0页和第1页属于A核,第2页和第3页属于B核。因此,需要注意的是,当Bootloader程序搬移用户程序时,A核的用户程序要被搬移到内部程序空间的第0页上,而B核的用户程序则要被搬移到第2页上。于是B核Boot表中的程序入口XPC和目的XPC应被设置成0002h。

4.2 Boot表的放置

本系统用4Mbit(256k×16)FLASH器件SST39VF400A作为片外数据存储器。页选信号由DSP通过CPLD给出,并且映射到DSP中I/O空间的0000h地址单元的低5位(系统复位后5位均为0,即第0页)。如图4所示。另外,此地址单元的第5位(CFG位)是控制FLASH映射的配置位。当CFG为0时,FLASH被映射到DMA片外数据空间的0000h,此时,Bootloader程序可以以DMA方式从FLASH中搬移数据并进行自启动;当CFG为1时,FLASH被映射到CPU片外数据空间的8000h,在这种情况下,可以通过程序向FLASH中烧写数据。因此,这一位在系统上电或复位后将被设置成0,以使A核能够顺利启动。

由于两个DSP核的Boot表内容不同,故应视Boot表的大小,将两个Boot表放到FLASH的不同页上,以便对两个核分别实行引导。本设计将A核的Boot表放到第0页,将B核的Boot表放到第1页。

4.3 外总线控制权的释放

如图5所示,在GPIO控制寄存器(地址3Ch)中,XIO_GRANT位为1代表相应的DSP核取得了片外总线的控制权;而在还没有取得控制权(XIO_GRANT位为0)但在申请片外总线的控制权时,相应的XIO_REQ位应置为1;CORE_SEL位用于表示程序在哪个核上运行,当在CPU A上运行时,读A核的GPIO控制寄存器的CORE_SEL位将返回到“0”,而当同一个程序在CPU B上运行时,读B核的GPIO控制寄存器的CORE_SEL位将返回到“1”。有关GPIO控制寄存器的其它相关位,设计时可查阅有关的参考文献1。

4.4 FLASH的烧写

笔者根据SST39VF400A的资料编写了一个DSP程序,该程序可同时将A核的Boot表烧写到FLASH的第0页,而将B核的Boot表烧写到第1页。

在系统上电或复位后,A核首先运行它的Boot-loader程序(此时FLASH的第0页映射到DMA片外数据空间的0000h地址单元),A核启动后执行用户程序。用户程序首先将页选设置成第1页,这样,FLASH的第一页将被映射到DMA片外数据空间的0000h;然后,A核释放片外总线控制权,并给B核发出复位信号,此时由于只有B核复位,且A核已释放片外总线的控制权,因此,B核将申请到片外总线控制权,同时执行Bootloader程序的启动以完成整个DSP引导。完整的启动过程流程图如图6所示,下面是A核的启动测试程序代码:

*mmregs

*titlc ″testLEDA″

*global begin

*text

.............

begin stm #0x000,0x0061 ;设置页选信号

portw ox0061,00h

call wait

andm #0xffcf,3ch ;释放片外总线

call wait ; 控制权

stm #0x00410x0061 ;给B核复位信号

portw 0x0061,00hcall wait

stm #0x0001,0x0061

portw 0x0061,00h

flash: rsbs 1,xf ;发光二极管亮

call wait

ssbx 1,xf ;发光二极管灭

call wait

b flash

;----Subroutine to wait for some time----

wait: stm #80,ar6

loop0: stm #30000,ar7-

loop1: nop

banz loop1,*ar7-

banz loop0,*ar6-

ret

5 实验验证

本设计中,在DSP的A_XF和B_XF脚上连接两个发光二极管,同时使被加载的用户程序通过循环来设置/清除这两个引脚以使两个发光二极管以不同的频率闪烁,以此来验证用户程序是否成功加载。系统上电后,两个发光二极管先后以不同的频率开始闪烁,说明DSP的A核、B核均成功地实现了上电自举。

c++相关文章:c++教程

评论