提高DFT设计测试覆盖率的有效方法

在DFT设计中,测试覆盖率及其测试效率是最重要的指标。一方面,理想的设计目标当然希望测试能够遍及整个芯片的逻辑,尽管理想值100%是不容易达到的;另一方面,测试效率亦非常重要,设计工程师总希望用最少的测试向量达到预期的测试覆盖率,来降低芯片的测试成本。

当然,DFT设计必须保证正常的逻辑功能为前提。不幸的是,功能设计总会忽略一些潜在的问题,导致最终的测试覆盖率往往不尽如人意。这种情况下,设计中有一些逻辑无论如何都不能被观测到或控制到,因此即使测试矢量的数量有很大的增幅,也不能使结果改善很多。

在实际的DFT设计中,存在对测试覆盖率有较大损害的两种情况:一种存在于数字逻辑-模拟逻辑(包括存储器)输入-输出处之阴影部分,另一种存在于特定的多芯片封装情况下未绑出的输入-输出焊垫处。二者的共同点在于:测试模式下部分逻辑的不可控或不可观测。

设计背景

本文探讨的设计目标是一个来自意法半导体的数字音频信号处理芯片,要求对数字功能逻辑进行扫描链测试,覆盖率达到98%以上。其功能逻辑中存在一些模拟模块,如锁相环、模数转换器和一些存储器单元等。更为重要的是,该芯片需要基于不同的应用系统需要,不但需要单独封装形式,也需要多芯片共享同一封装。这样,在某些多芯片封装中,就有部分焊垫未引出或接地。而测试的设计初衷是产生一组测试向量适用于所有封装形,就要求考虑最严格的封装下可用的管脚资源。

DFT设计有两个基本原则:可控制性和可观测性,即DFT设计要求所有输入逻辑是可控的和输出逻辑是可测的。显然,考虑到本设计中的模拟模块接口和封装形式的资源有限性,不可控逻辑和不可观测逻辑对不小于98%的目标测试覆盖率给出了很大的挑战。

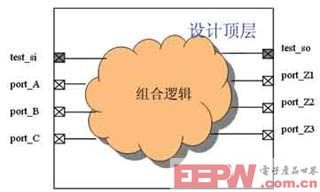

如图1所示,在某种芯片封装情况下,除信号test_si和test_so外,其余焊垫并未绑出(接地或悬空),从而造成信号port_A、port_B、port_C和port_D的不可控,以及信号port_Z1、port_Z2和port_Z3的不可观测(悬空)。导致很多相关逻辑不能正常参于DFT测试,测试覆盖率受到较大的损害。

图1 封装造成的测试逻辑不可控和不可测

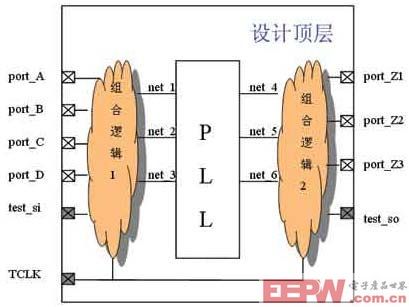

DFT设计的可控制性和可观测性是通过原始的管脚来实现的,事实上功能设计不可能专门为DFT保留足够多的管脚。如图2所示的数字-模拟接口,由于PLL模块的存在,显然信号net_1、net_2和net_3上得到的测试结果不可直接观测(不可测),组合逻辑1相应的测试覆盖率降低了;同时,由于PLL模块的存在,信号net_4、net_5和的net_6不能直接赋值(不可控),导致组合逻辑2的部分逻辑不能正常参于DFT测试,相应的测试覆盖率受到较大的损害。总的来说,芯片的测试覆盖率降低了。

图2 模拟模块造成的测试逻辑不可控和不可测

解决方案

针对设计中的上述情况,可以通过适当添加测试点的方式,使原来不可控和不可测的逻辑变化反映到扫描链上,使之变得间接可控和可测,以期提高整个芯片的测试覆盖率和测试效率。

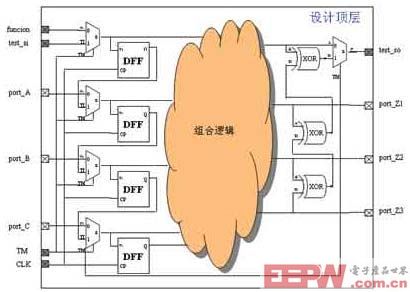

对于图1所示的某些封装中,不可控和不可测的未绑出(接地或悬空)管脚,图3给出了相应的定制的解决方案。

图3 添加控制点和观测点提高测试覆盖率(封装部分管脚未绑出情况)

对于输入管脚,添加一个带有选择端的寄存器。当控制选择信号为“0”时,电路处于正常工作状态,功能逻辑从输入端接收到正常的输入数值。当选择控制为“1”时,电路处于测试状态。在移位过程中,这些点由测试链预置相应的值;在捕获过程中,将之接地防止不定态在设计中的传播。

在输出管脚处,添加少量异或门和选择器件。当控制选择信号为“0”时,电路处于正常工作状态,输出管脚正常输出功能信号。当选择控制为“1”时,电路处于测试状态,用异或门将未能绑出的管脚的变化引出,相当于这些管脚也可以被观测了。

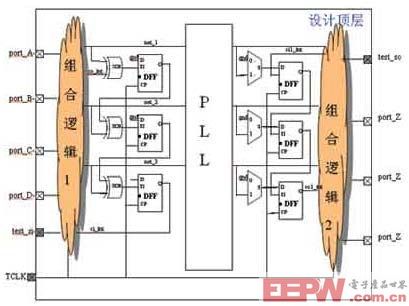

针对图2所示的数字-模拟接口,部分模拟模块输入信号通过组合逻辑给出,但在测试时并没有逻辑将这些“终点”的信号影响引出观察,因此这些点是不可观测的。这与DFT设计可观测要求(需管脚直接输出)不相符,可能造成测试覆盖率的损害。同时,部分模拟模块输出信号控制相应的组合逻辑,但在测试中,这些点是“浮空”(不可控制)的。这与DFT设计可控要求(需管脚直接输入)不相符,造成测试覆盖率的降低。图4给出了类似前者的定制解决方案,其实质也是把这些不可控和不可测点连到测试链上去,让这些逻辑间接可观测或可控制以改善测试结果。

图4添加控制点和观测点提高测试覆盖率(数字-模拟接口情况)

如图所示,在模拟模块输入信号处添加少量异或门和选择器件,并将它们连到扫描链上去。当控制选择信号为“0”时,电路处于正常工作状态,模拟模块的输入管脚正常接收功能信号。当选择控制为“1”时,电路处于测试状态,用异或门或者其他器件将未能观测管脚的变化引出,相当于这些管脚间接可以被观测了。

如图所示,在模拟模块输出信号处添加一个带有选择端的寄存器。当控制选择信号为“0”时,电路处于正常工作状态,模拟模块信号正常输出到后续的功能逻辑。当选择控制为“1”时,电路处于测试状态:在移位过程中,这些点由测试链预置相应的值;在捕获过程中,将之接地防止不定态在设计中的传播。

对于其他的模拟模块如ADC, 存储器等,采用类似的方法可改善整个芯片的测试覆盖率和测试效率,达到目标测试效果。

结语

在前面提及的实际项目DFT设计中,功能逻辑部分含有万余寄存器。为提高测试覆盖率,添加仅12个寄存器及很少部分组合逻辑作为测试点后,即可将测试覆盖率从原来的95%提高到98.3%。由此看来,这种方法是很有效率的。并且可根据项目实际需要,添加更多点以期达到更高覆盖率,理论上测试覆盖率可接近100%。

推荐RTL功能设计时就能考虑这种测试结构。这样做设计工程师之间能够了解彼此的设计需求,功能测试结构明晰,在DFT设计过程中省去很多麻烦。如果发现这类问题在RTL完成之后,一些DFT工具也提供用户自定义的测试点插入,但是要注意测试控制信号选取一定要与需要的测试模式匹配,否则无法完成相应的测试期望。这种方法的关键是了解在哪里加测试点更为有效。

评论