PCI-Express2.0协议层的数字验证及调试解决方案

L0s/L1级电源状态管理通过将链路置于电气空闲(E-IDLE)下来降低能耗,因此要求链路双方设备都能够实现L0s,快速的进入或退出电气空闲状态。L1相对于L0会进一步降低功耗。从PCIe1.0开始,L0s级电源管理就是调试测试的一个难题。链路宽度降低(Downconfigure)和提升(Upconfigure)是根据链路数据传输流量控制而定,只要满足系统的吞吐率,可以适当的关闭原本活动的链路,以达到减小能耗。同样,当系统吞吐率要求增大时,能够开启被关闭的链路。链路的传输速率也可以在2.5Gbps和5Gbps之间切换,以最小的系统能耗完成数据传输任务。

一.PCIe2.0技术简介

PCIe是串行的点对点的互连总线。最初PCIe是为取代AGP总线而设计,目前已经成为主流的I/O互连总线。PCIe提供了一个可升级的构架,传输带宽随着链路的宽度增加而增加。PCIe2.0较PCIe的主要变化是:速度增加,从2.5Gbps增加到5Gbps,并且速度可以协商;电气空闲(Electrical Idle)的进入和退出,减少能耗并简化了设计,增强系统可靠性;链路宽度降级,减少能耗。链路宽度提升,增加系统额外带宽。

PCIe2.0为系统带来优化的同时,也为设计和测试工程师带来了挑战。依据PCIe2.0的主要变化,要求测试设备有能力捕获链路上所有层面的协议。Tektronix TLA7000系列逻辑分析仪和TLA7S16 /TLA7S08模块是极好的针对PCIe2.0调试和验证的工具。

二.PCIe系统构架

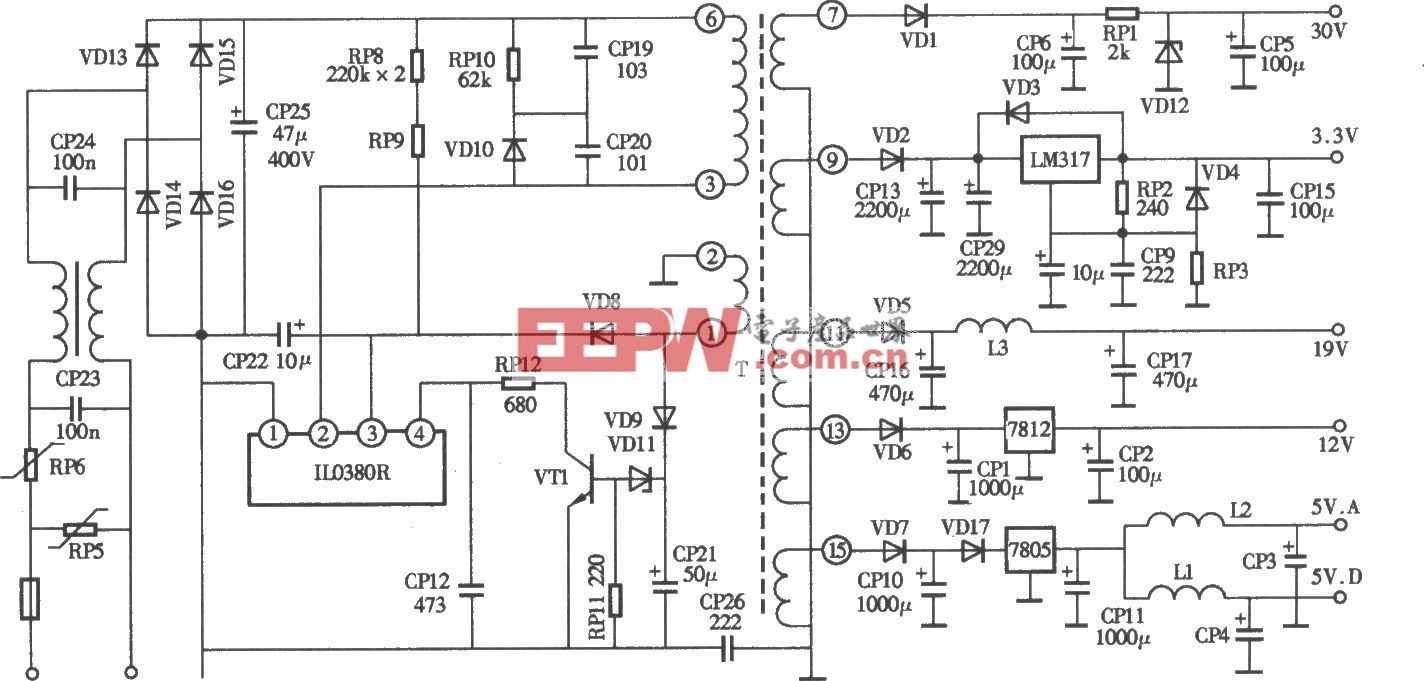

PCIe是一个三层结构的系统,包括物理层(逻辑子层和电气子层),数据链路层以及事务层。事务层主要负责事务的请求/完成、TLP流控制和消息通知。数据链路层主要负责确保数据在链路上正确、可靠的发送和接收。物理层分为两个部分:逻辑子层和电气子层。电气子层主要负责发送和接收信号;逻辑子层主要负责数据加扰/解扰、8b/10b编码、封包等。另外,链路的协商是在逻辑子层完成的。TLA7S16串行逻辑分析模块定位于捕获逻辑子层、数据链路层和事务层的数据进行协议分析,并且探测方式不会影响链路的信号完整性。

三.数据率训练(Training)过程的捕获与分析

所有的PCIe2.0链路在初始阶段必须工作在2.5bps速度下,这主要是考虑到向下兼容的能力。此外,当系统吞吐率要求不高的时候,也可以从5Gbps的速据降到2.5Gbps以减少能耗。因此,测试设备首先必须能够探测到速度的变化,然后通过捕获的数据分析速度切换是否按照规范要求进行。

能否在速度切换开始时触发并捕获数据是揭示链路上所发起序列的异常问题的关键所在。通常,当发起速度切换后,需要对第一个训练序列(TS)进行捕获。TLA7S16/08模块的序列触发功能可以对任意一条通道进行多达连续16个符号的触发设定。序列触发提供了对任意一个PCIe2.0的有序集中任意域的设定。

很多情况下,期望的触发条件由于链路中的协议出现了错误而无法被侦测到,这会减缓甚至被迫中断调试。在此期间,工程师往往不得不随机捕获数据,手动地去分析数据和协议的正确性。TLA7S16/08的序列触发可以帮助工程师通过触发链路中单独的通道去发现问题的根源。出现问题的通道暂时被忽略,协议的验证和分析将得以进行下去。

只要串行逻辑分析仪被触发,采集到的数据将会显示出完整的2.5Gbps到5Gbps速度切换的过程。工程师能非常直观地发现有问题的通道。另外,所有采集到的数据都会按照协议规范进行解码。

当系统完成2.5Gbps速度的训练后,链路会进入L0状态。在链路双方的训练中会通知支持的速度,如果双方都支持5Gbps,则链路会尝试着将速度切换到5Gbps。当链路处在L0状态时,会切换到Recovery状态,并且开始进行5Gbps速度切换的训练。当完成训练序列后,2.5Gbps的链路会进入电气空闲状态,接着链路会退出电气空闲,链路双方将运行在5Gbps的速度上,同时发起电气空闲退出有序集(EIEOS),紧接着通过其他的训练序列,速度切换将发生在Recovery.Speed状态中,最后链路返回到L0状态下。

请注意,串行逻辑分析仪会将每一条链路上发生的每一个符号和相应的解码信息一并显示。假如其中有一条通道发生误码的话,这些误码将会被显示在单独的通道上,用户能通过链路详细信息(Link Detail Column)中的内容快速地判断出在某一通道上是否存在问题。传统的协议分析仪仅能得到有错误帧的提示。

PCIe中的ASPM(Active State Power Management)是为了降低能耗而设计,然而PCIe系统出现的问题大部分是在电源管理期间。

当TLP Configuration Write命令发起,向寄存器写入了一个错误的数据,就会引起系统的异常。这种问题通常发生在ASPM使能期间,硬件和软件出现了配合问题。为了捕获这些异常事件,串行逻辑分析仪必须要捕获到链路在退出以及进入L0s状态过程中的TLP数据包。分析仪为了能够进行极限测试,在退出EIDLE状态过程中,必须尽可能多的捕获FTS包,即尽可能快地探测链路的变化,及早和被测系统实现同步和锁定。TLA7S16/08串行逻辑分析仪通常仅需要12个FTS包,就可以完成退出EIDLE后链路的锁定。及时、快速的链路数据锁定避免了在L0开始时有效TLP包的丢失。传统的协议分析仪可能需要上千个FTS包才能完成帧同步。图3说明了分析仪如何捕获到链路进入L0s的状态。

当链路退出EIDLE需要发送FTS包,发送FTS包的个数在链路训练的过程中已经确定了。如果分析仪在退出EIDLE过程中不能锁定数据,就无法采集到TLP Configuration Read包,更无法分析和验证包内携带的数据信息。

数据包级别的触发功能再配合实时的数据过滤功能,可以进一步缩小需要寻找的感兴趣的TLP和DLLP包的范围。

另一个可能发生的事件是当ASPM使能后,出现了TLP丢包的情况。在正常的运行环境中(非L0s状态),所有的TLP包能够被正确的捕获。在电源管理阶段,如果链路不能正常工作,很可能是TLP没有正确的发起。分析仪会捕获所有的TLP包,按照每一个TLP序列标识符进行排序,如果有TLP包丢失的情况,很容易被发现。

五.链路宽度协商过程分析

一些调试、验证的挑战是和链路动态切换有关的。PCIe规范允许链路双方提升或者降低链路的宽度。例如如果链路的一方在新的链路宽度训练中出错,链路将重新进入Recovery状态。TLA7S16/08串行逻辑分析仪能够验证链路宽度训练的整个过程。同样,当发起链路宽度训练序列后,链路会发起EIEOS,接着进入EIDLE状态。当链路退出EIDLE,分析仪会捕获完成链路宽度训练的数据包(图4)。

当链路退出EIDLE,同样需要额外的TS包使得链路恢复到正常的状态。串行逻辑分析仪同样能够捕获完整的过程。

六.多总线时间相关分析

随着电子系统变得越来越复杂,对系统并行总线和高速串行总线的整合设计变的非常的普遍。在许多应用中,不可能仅对PCIe总线单独进行分析,例如PCIe总线向控制器发起内存读数据请求,接着控制器向DDR内存进行读操作。如果DDR读数据使用了错误的地址,将会导致PCIe请求到错误的数据,并可能引起系统崩溃。逻辑分析仪是唯一能够对PCIe、控制器总线和DDR内存在单一仪器内进行分析的设备,所有的数据样点都是有时间相关的时间标记。

TLA7S16/08配合通用的逻辑分析仪模块(TLA7BBx)可以提供PCIe链路和其他并行总线时间相关的调试能力。TLA7BBx以最高50GS/s采样率对136路信号进行高精度的定时采集,还可以通过外时钟同步进行最高速度为1.4GHz的同步分析。逻辑分析仪能够获得这些并行信号,串行分析模块可以采集到PCIe链路的数据。这样的时间相关的信息能帮助我们解决很多调试、验证问题。

七.信号探测方式

对PCIe系统的探测必须遵循不能影响到链路正常特性的原则。在物理层面上,要求探测不能破坏原来链路的信号完整性;在数据层面上,要求不能改变原有系统的时序特性。Tektronix提供的P6701S/P6704S/P6708S/P6716S系列内插探头,提供对被测信号的高阻探测,与传统的协议分析仪先将信号缓存再输出的结构不同,而是直接将信号输入到采集系统中。此外,P6708/P6716探头还支持芯片级的PCIe信号探测。

总结

PCIE2.0的验证充满着各种挑战,对芯片和系统性能的验证;5Gbps的数据传输率;最小化系统开销以及高级电源管理(ASPM);复杂的协议和瞬变的故障都使得PCIE2.0的调试变得困难重重。Tektronix公司TLA7Sxx系列串行逻辑分析仪模块提供强大的硬件调试性能,配合TLA7000逻辑分析仪主机以及其他测试方案,最大程度满足被测系统的逻辑、协议测试。

评论