高密度封装技术推动测试技术发展

自从表面贴装技术(SMT)开始逐渐取代插孔式安装技术以来,线路板上安装的元件变得越来越小,而板上单位面积所包含的功能则越来越强大。

就无源表面贴装元件来说,十年前铺天盖地被大量使用的0805元件,今天的使用量只占同类元件总数的大约10%;而0603元件的用量也已在四年前就开始走下坡路,取而代之的是0402元件。目前,更加细小的0201元件则显得风头日盛。从0805转向0603大约经历了10年时间。无疑,我们正处在一个加速小型化的年代。

再来看看表面贴装的集成电路。从10年前占主导地位的四边扁平封装(QFP)到今天的倒装芯片(FC)技术,其间涌现出五花八门的封装形式,诸如薄型小引脚封装(TSOP)、球型阵列封装(BGA)、微小球型阵列封装(μBGA)、芯片尺寸封装(CSP)等。纵观芯片封装技术的演变,其主要特征是元件的表面积和高度显著减小,而元件的引脚密度则急骤增加。特别是BGA技术,已成为现代高密度IC封装技术的主流,如图1所示的NVIDIA公司的GeForce FX图形芯片(GPU)含有1152个焊脚,是同等尺寸大小QFP所容纳引脚数的3-4倍。但高I/O数也给传统电路接触测试(如ICT)带来挑战,同时BGA焊点隐藏在封装体下面,无法进行人工目检。。

表面贴装元件尺寸的不断缩小和随之而来的高密度电路安装,对测试带来了极大的挑战。传统的人工目检即使对于中等复杂程度的线路板(如300个元件、3500个节点的单面板)也显得无所适从。

曾经有人进行过这样的试验,让四位经验丰富的检验员对同一块板子的焊点质量分别作四次检验。

结果是,第一位检验员查出了其中44%的缺陷,第二位检验员和第一位的结果有28%的一致性,第三位检验员和前二位有12%的一致性,而第四位检验员和前三位只有6%的一致性。

这一试验暴露了人工目检的主观性,对于高度复杂的表面贴装电路板,人工目检既不可靠也不经济。而对采用微小球型阵列封装、芯片尺寸封装和倒装芯片的表面贴装线路板,人工目检实际上是不可能的。

不仅如此,由于表面贴装元件引脚间距的减小和引脚密度的增大,传统的电路接触式测试受到了极大限制。据北美电子制造规划组织预计,在2003年后利用在线测试对高密度封装的表面贴装线路板检测将无法达到满意的测试覆盖率。以1998年100%的测试覆盖率为基准,估计在2004年后这测试覆盖率将不足50%,而到2010年后,测试覆盖率将不足10%。另外在线测试技术还存在的背面电流驱动、测试夹具费用和可靠性等问题的困扰,种种迹象表明这一技术的发展已走到了尽头。

柳暗花明: 光学检测技术带来测试新体验

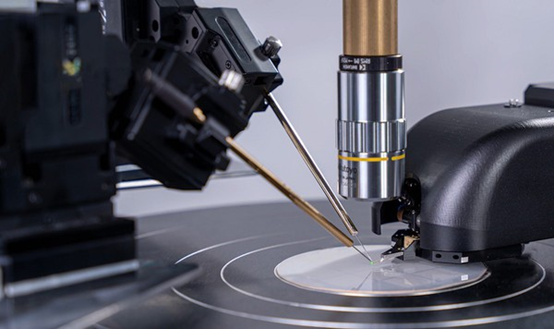

技术的发展绝不会因为上述困难就停滞不前,测试检验设备制造商推出了像自动光学检测(Automatic Optical Inspection,简称AOI)设备和自动X射线检测(Automatic X-ray Inspection,简称AXI)设备等这样的产品来应对挑战。事实上,这两种设备在被大量用于线路板制造工业以前,就已经在半导体芯片制造封装过程中得到了广泛的应用。不过,它们还需要进一步的创新才能真正应对由表面贴装元件小型化和高密度线路板带来的测试困难。

评论