图像传感与处理是否集成?

众所周知,手机的体积起来越小,价格也越来越低。当你针对消费者需求,要为手机增添更多功能时,如为静止图像和视频提供高分辨率的成像功能,你就会面临一个相当有意思的研究案例,也就是作为一种经典工程学科的折衷处理问题。

为了更好地进行选择,首先就要看一下可拍照机手机及其相关应用所需的基本功能,其中包括了图像质量、去马赛克(demosaicing)算法(把Bayer色彩滤光片的信号流转换为真实的图像)、噪声补偿、自动白平衡(auto white balance)、自动曝光、文件较小以及低功耗。

以集成追随超薄手机潮流

通过采用JPEG压缩,可以降低文件大小,并满足存储器要求。这种算法出现在某些图像传感器IC上,但更多的是通过被称为图像信号处理器(ISP)的辅助芯片(Companion Chip)来处理。而在CMOS图像传感器(CIS)面世之前,所有的图像处理都是在专用处理IC上完成的。

虽然JPEG压缩至今仍适用于电荷耦合器件(CCD)和CIS,但情况已开始发生变化。固态成像(solid-state imaging)技术已进入系统级芯片(SoC)和系统级封装(SiP)的争战中。不变的是以最少的条件创建质量较好的图像。

对于希望将数字处理整合到图像传感器上的开发人员而言,关注的核心问题是拍照模块的总体占位面积。在将数字处理集成在传感器裸片方面,安华高(Avago)是引领厂商之一。事实上,安华高是唯一一家在CIS器件集成片内JPEG编码和自动聚焦控制功能的供应商。自然而然地,该公司也提倡在拍照模块中使用单块系统级芯片(SoC)。安华高的行销经理Feisal Mosleh曾表示:“拍照模块在手机中的安装方式影响了手机厚度,而厚度目前是一项主要卖点。目前手机中还没有可供堆栈封装的厚度。”

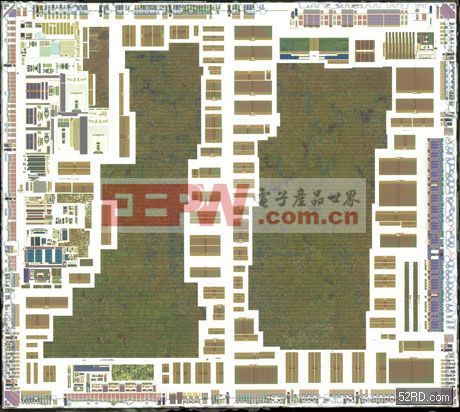

图1: 安华高的CMOS图像传感器集成了片内JPEG编码和自动聚焦控制功能

的确,超薄手机是一项重要营销亮点,而原始设备制造商(OEM)对封装、元件和模块的要求严格限制了供应商的物理设计。尽管现在有人认为元件厚度问题严重,且没有什么空间余留,但必须认识到,我们所讨论的厚度问题正是单裸片的真正优势所在,这一点十分重要。虽然存在关于裸片粘接、垫片(spacer)和线邦定等额外开销,图像信号处理器(ISP)的裸片厚度仍可以达0.2mm及以下。这是否占模块高度的很大比例,取决于各个模块供应商。对于标准移动成像架构(SMIA)标准来说,最大高度为7.6mm。某些已发布的超薄手机在消费领域中引入了模块高度限制特性,如三星的“信用卡手机”SGH-P300,厚度只有9mm。摩托罗拉的蛤壳式手机Razr V3i厚度为14mm,三星的t509和Xcute S50厚度分别为9.8mm和9mm。

拍照模块的成本考虑

手机的拍照模块售价一般在9美元左右。Semiconductor Insights公司关于诺基亚6111手机的拆卸和材料清单(BOM)分析报告估计,其中采用的意法半导体(ST)100万像素拍照模块VS6650的成本为7.75美元。有意思的是,这一应用产品使用的是单独的ISP IC——STV0976N手机图像处理器,并没有整合到拍照模块中。STV0976N实际上安装在手机主板的下侧,这样做可以使模块很薄,但占用了36mm2的额外面积。ISP的成本使得手机BOM增加了1.45美元。ST的ISP采用了大小为8.8mm2的图像处理硅芯片。

包括本文论及的片内(on-chip)集成与封装内(in-package)集成的对比在内,业界有关硅片处理成本问题的讨论屡见不鲜,但终将盖棺定论。要透彻了解这一关键参数,重要的是使用最好的分析工具。目前最好的IC成本模型工具是IC Knowledge公司的产品。它的2006 IC Knowledge模型建立了从头到尾的全面的制造流程,有助于进行精确的成本估算。

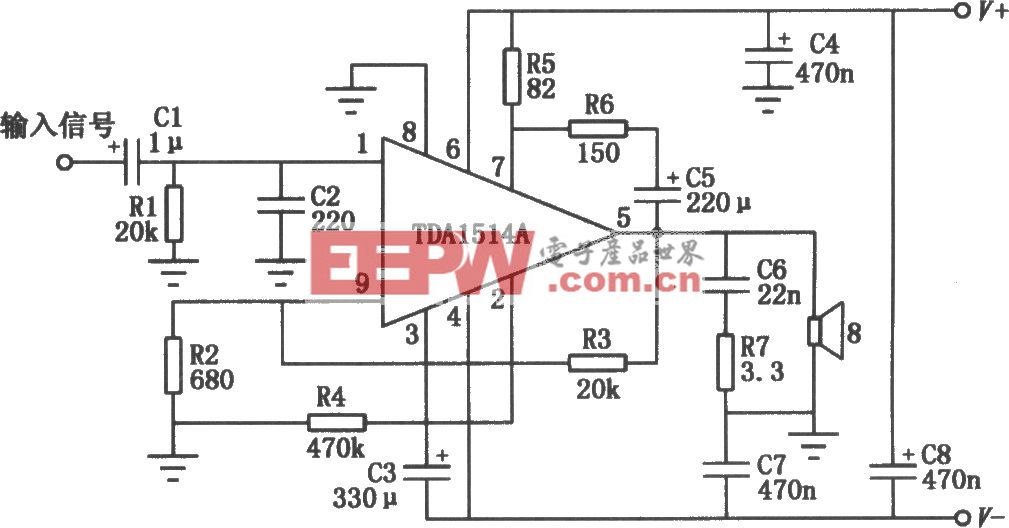

象Zoran Coach 8这种芯片,利用非常基础的大批量CMOS工艺流程,可使制造成本极低。假设委托一家台湾地区的晶圆厂采用180纳米、5层铝工艺制造,尺寸为5.9mm×5.2mm的每片IC的成本为84美分,相当于每平方毫米成本0.028美元。

图2: Zoran的数码相机图像信号处理器集成了抖动稳定和MPEG-4压缩等功能

此外,美光科技利用其CIS技术,充分发挥该公司的大批量DRAM制造工艺的优势,凭其图像处理技术在短期内已成为CMOS成像技术领域的主要玩家。美光拥有两个版本的28微米的像素生成技术。其中,MT9D011是带有原始Bayer输出的单纯传感器版本,而MT9D111则在其基础上增加了ISP功能。在采用美光的150纳米工艺制造时,数字处理部分使传感器IC的面积增加了24.6mm2。利用IC Knowledge模型分析可知,相应的额外成本为1.03美元,比Zoran ISP高出将近20美分。

对于图像传感器生产商而言,另一个有关大小的问题,是芯片能够支持的像素数量。首先,手机拍照模块的发展趋势是沿百万像素提升。但在尺寸和成本方面所受的限制,阻碍了裸片尺寸随像素数量的不断提高而增大,解决方案就只有减小像素。目前这一代图像传感器的像素尺寸可达2.2微米。而当像素缩小到2.2微米及更小时,越来越多的额外处理问题就会接踵而来。

由于像素尺寸是唯一的变量,像素越小,对低亮度条件越不敏感,干扰也就越大。结果造成即便是设计与制造俱佳的图像传感器,也会生成质量低劣的图像,除非图像处理能够补偿。现在不少手机都具有300万到500万像素的图像传感器,三星甚至已推出1,000万像素的可拍照手机。

传统的数码相机(DSC)设计也许可为手机市场提供一些借鉴。例如,Zoran最新的Coach 8 ISP是适用于DSC应用的最高端器件。Zoran的器件专门设计用于成本较低、占位面积有限的DSC。它们所具有的功能,比如MPEG-4压缩、用于输出到高清监视器的HDMI接口、LCD驱动器、32位MIPS CPU和数字视频图像稳定器等,都远远超越了当今的手机功能。DSC基本上只涉及到图像处理,故可以有把握地说,图像性能没有被损及。所以,DSC应用因采用单独的传感器和ISP而牺牲了性能这一说法值得怀疑。

CMOS以独到技术力拼CCD图像质量

CMOS图像传感器一直都与CCD图像传感器在分辨率与图像质量方面力拼。实际上,CMOS产品拥有一些明显优势。这种成像器(imager)可在现有CMOS生产线上以低成本进行快速生产,它们能集成大量的图像处理、压缩及其它逻辑电路,有助于设计尺寸更小的产品。

虽然早期的CMOS图像传感器非常便宜,但他们生成的图像却不能与CCD相提并论。不过,随着CMOS技术的进步,它开始在越来越多的应用中取代CCD。虽然这些技术进步并没有出现在很多种类的CMOS器件中。

当CMOS图像传感器刚开始挑战CCD时,像素尺寸一般都相当大。然而,技术永远是不断向前发展的,为了缩小尺寸,图像传感器处理技术面临的压力越来越大。

为了实现像素尺寸的不断缩小,目前的CMOS图像传感器处理技术正变得越来越有独到之处。其方法之一便是创建微透镜(Micro Lens),把更多的光聚焦在更小的光电二极管上。在前端制造工艺,供应商还可以创建更敏感的、固有噪声更低的光电二极管。

MOSFET的沟道表面干扰很大,把光转换为电荷的选择很少。因此,大多数现代图像传感器供应商都把掺杂剂注入到硅片表面上。这种“钉扎层(pinning layer)”把光吸收区域更深地推进到硅片内部,远离受干扰的表面。这种“钉扎光电二极管(pinned photodiode)”工作非常理想,但增加了额外的处理成本。

未来趋势将是背离集成?

回到生产工艺上,美光科技的2.8微米像素工艺的建模成本为0.042美元,而带有嵌入式闪存的类似逻辑工艺则可能只有0.023美元左右。成本的差异突显了这一事实,即随着CMOS成像工艺变得越来越专用化,它的成本也愈发高昂。在某些情况下,它的硅工艺成本可能是基本工艺的两倍。

问题在于,你为什么要为在昂贵工艺线上制造的额外功能买单呢?生产批量将决定成本,因此,你真的需要透镜、滤波器及其它成像器处理模块等所有这些额外的硅片吗?这么做的理由之一是可以把拍照模块的占位面积减至最小。不过,还有其它一些趋势需要考虑。

基带产品和应用处理器领域的大玩家都期待在它们的芯片上增加ISP功能。高通和TI都在创建复杂的手机SoC解决方案方面拥有丰富的经验。考虑把ISP增添到基带处理器上的这一概念的提出并没有很长时间。TI OMAP 3(430)集成了片上ISP,并为希望使用较简单便宜的拍照模块的手机设计人员提供了JPEG和其它选择。如果不计芯片面积的话,把ISP集成到这些复杂器件(采用10层金属、65纳米工艺制造)上而增加的成本几乎可以忽略不计。

为什么要集成呢?一个一直没有被考虑到的因素是功耗问题。完全集成传感器和ISP的方案肯定会降低功耗。不过,若拍照功能造成的功耗问题没有引起广泛注意的话,手机生产商可能有大量的余地去选择一个更廉价的解决方案。

预计未来的发展趋势是背离集成。随着传感器分辨率的提高,越来越多的传感器将只整合输出数字信号所必需的电路。制造商要么会将处理和压缩硬件放在ISP上,要么会在下一代应用处理器中使用内置式功能。

本文使用海纳锐利编辑并转载, 版权归原作者所有。

评论