一种以优盘为存储介质的MP3播放器设计

引言

随着mp3播放器作为消费类产品的普及,MP3的设计与生产也越来越多。在当前的MP3播放器中,一般有以下几种设计方案:

① MCU内置硬解码模块。典型的芯片有Atmel公司的AT89C51SNDI等芯片。

② 外置独立的MP3硬解码芯片。此种方案的好处是可以使用众多的MCU,可根据需要任意选择。硬解码芯片典型的有VS1011B、STA013等芯片。

③ 使用功能强大的MCU进行软解码,如使用DSP或是高性能的ARM。此种方案较为灵活,通过软件升级即可实现产品的升级。

MP3播放器的存储介质一般采用Flash存储芯片。随着USB技术和闪存技术的发展,优盘已经成为一种大众化的电子产品被广泛使用,但优盘一般只是作为PC的移动存储器。本文研究的一种方案是在上述MP3设计方案②的基础上,外扩优盘读写电路,使存储介质使用普通的优盘。这样可以解决普遍使用的优盘只能作为PC外设存储数据用的问题,使U盘的使用范围扩展到MP3上。更大的意义还在于,本文提出了一种在以嵌入式系统、MCU为核心的消费类电子产品或工业产品中,将优盘作为数

据存储器使用的设计方案,为在微计算机测控系统、仪器仪表、无纸化数据记录仪、数码相机等产品中添加优盘外设功能提供有益的参考。

1 硬件设计

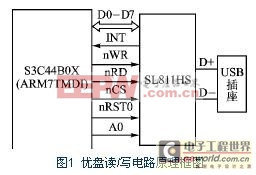

S3C44B0X是Samsung公司开发生产的为嵌入式设备提供的一个低成本、高性能的ARM7TMDI核处理器,其最高运行频率可达66 MHz。SL811HS是Cypress公司的一款遵从USB1.1协议的嵌入式Host/Slave USB芯片;可以支持低速和高速模式,能自动侦测低速模式1. 5 Mbps设备和高速模式12 Mbps全速设备。由于具有8位数据总线的支持,使该芯片可以较为简单地与微控制器相连,SL811HS芯片与S3C44B0X的接口较为简单。本系统中ARM读/写优盘原理框图如图1所示。

SL811HS的控制命令和数据均通过D0~D7传输,A0为数据或地址选择线。当A0置为低电平时,D0~D7上传输的是SL811HS片内寄存器的地址;反之当A0置为高电平时传输的则为数据。nWR、nRD、nCS、nRST0分别为写控制线、读控制线、片选线和复位线,S3C44B0X通过这几根控制线完成对SL811HS片内缓冲区的读写、片选和复位等操作。INT是SL811HS的中断请求信号线。当SL811HS检测到优盘插入、拔出时,通过将INT线拉高通知S3C44B0X。S3C44B0X可以通过查询SL811HS片内状态寄存器来得知是优盘插入或是拔出。对状态寄存器进行写操作可以清除中断,但需要注意的是ARM的结构特性。ARM内部通常是Little Endian方式存储和使用4字节对齐方式[1],并且当采用16位数据总线时,地址线ADDR0是无效的[2]。在本系统中,SL811HS芯片A0端是与ADDR1相连接的。

VS1011B是一款单芯片的MP3解码芯片,在国际MP3业余爱好者中影响较大,集成解码、A/D转换、音频放大等功能。VS1011B与S3C44B0X接口为SPI接口,其连接电路原理框图如图2所示。

VS1011B的控制与数据传输是通过SPI接口完成的,DREQ、xDCS、xCS、nRST1分别为数据请求端口、数字片选信号线、片选线、复位线。在VS1001B的新模式下,SDI(Serial Data InteRFace)数据和SCI(Serial Command Interface)数据传输可以共享ARM的一个SPI接口;而在兼容模式下,SDI数据传输要用DCLK、SDATA串行接口,SCI数据传输用SPI接口。为了简化电路,此处选用了新模式。

评论