一种基于DSP和MCU的双CPU数据处理系统设计

在嵌入式控制系统中经常需要对现场物理量进行数据采集与实时处理,且要求系统具有良好的人机交互功能,这时仅采用DSP处理器往往不能满足要求。本文选择以单片机为主处理单元(主要完成各种控制和接口功能)、DSP芯片为从处理单元(主要完成数据运算和处理)的系统结构方案,该系统可独立使用,也可与上位PC机进行通信。

1 数据处理系统硬件总体设计方案

该数据处理系统是为一种信号检测设备设计[1-2]的,能快速采集两路传感器的信号并进行实时处理。系统由MCU处理器、DSP处理器、8位高速A/D转换器以及FLASH存储器等部分组成,传感器的信号送入高速A/D转换器进行模数转换,结果送入DSP中。这里DSP芯片采用了TI公司具有高速数据运算和处理能力的TMS320VC5402,运算结果通过HPI传送到单片机,利用单片机方便的接口电路和控制功能,输出并显示结果或送入PC机做进一步处理。图1为该系统的结构框图,其中FLASH用于存放自举引导程序。

2 数据处理系统硬件接口设计

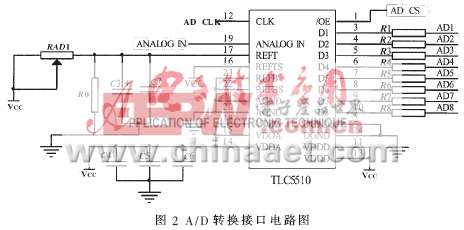

2.1 A/D接口电路设计

该数据处理系统首要的任务是将传感器的信号经过调理后进行A/D转换。为了实现高速、实时的数据采集转换和处理,系统中A/D转换模块采用了TI公司的8位并行A/D器件TLC5510A[3-4],最高频率可达20MHz,能实现实时的数据采集。该模块采用单一+4V电源供电,正常工作时的最大功耗为150mW,适合便携式仪器仪表使用。传感器的信号通过TLC5510A的模拟量输入引脚送入,利用DSP内部定时器来控制A/D采样率,在每次产生定时器中断时对数据进行读取,这样可通过设置定时器的初始值来改变采样率。图2为A/D转换接口电路图,其中 为片选端,低电平有效,时钟由DSP内部时钟提供,送入A/D芯片的CLK引脚。转换后的8位数字量经电平转换(A/D转换器和DSP工作电压不同)后直接送入DSP中,结合相关算法进行数据处理。

为片选端,低电平有效,时钟由DSP内部时钟提供,送入A/D芯片的CLK引脚。转换后的8位数字量经电平转换(A/D转换器和DSP工作电压不同)后直接送入DSP中,结合相关算法进行数据处理。

2.2 数据处理系统FLASH引导加载[5]

由于系统用于便携式仪器中,加电后要有独立运行的能力,而所使用的DSP芯片内无永久性存储器,所以系统运行时需进行自举引导。DSP为脱机运行提供了五种引导模式,分别是:主机端口(HPI)引导模式;串行EEPROM引导模式;并行引导模式;标准串行口引导模式;I/O引导模式。其中并行引导方式在这里被认为是最佳的,因为HPI端口引导方式、串口引导方式、I/O引导方式只适用于由其他处理器为DSP TMS320VC5402提供运行代码的多处理器系统中,SPI串行EEPROM引导方式和并行引导方式虽然都适用于以TMS320VC5402为核心的独立系统,但是SPI EEPROM引导方式价格偏高,而并行引导方式则可以采用FLASH,因为FLASH种类很多且价格较低,可以充分体现系统的性价比优势,故该系统中采用并行引导方式实现程序的自举引导加载。

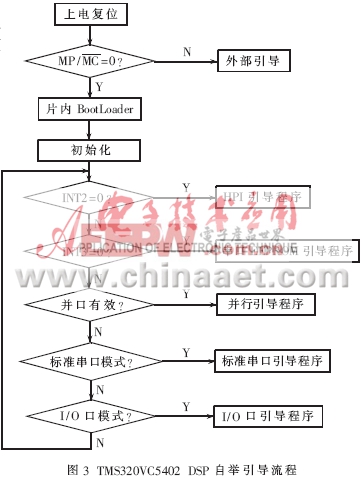

2.2.1 自举引导过程

TMS320VC5402 DSP的引导加载选择过程如图3所示。系统上电或硬件复位后,首先判断芯片的 引脚。如果该引脚为高电平,则选择微处理器模式,片内ROM从程序空间移去,DSP执行FF80H处的跳转命令,跳转到F800H处的引导程序段并实现代码移植功能,最后再次跳转到加载的用户程序起始地址并执行应用程序;如果

引脚。如果该引脚为高电平,则选择微处理器模式,片内ROM从程序空间移去,DSP执行FF80H处的跳转命令,跳转到F800H处的引导程序段并实现代码移植功能,最后再次跳转到加载的用户程序起始地址并执行应用程序;如果 引脚为低电平,则选择微计算机模式,片内ROM被映射到程序存储器空间,DSP执行FF80H处的跳转命令,自动跳转到内部引导程序入口地址F800H,启动内部引导程序,选择引导模式。本系统的

引脚为低电平,则选择微计算机模式,片内ROM被映射到程序存储器空间,DSP执行FF80H处的跳转命令,自动跳转到内部引导程序入口地址F800H,启动内部引导程序,选择引导模式。本系统的 引脚置低。

引脚置低。

图3为DSP自举加载的流程,上电判断 为0后,依次检测INT2、INT3,当满足要求且并口有效时,即开始执行并行引导程序。否则,按引导流程依次判断,直到满足条件为止。

为0后,依次检测INT2、INT3,当满足要求且并口有效时,即开始执行并行引导程序。否则,按引导流程依次判断,直到满足条件为止。

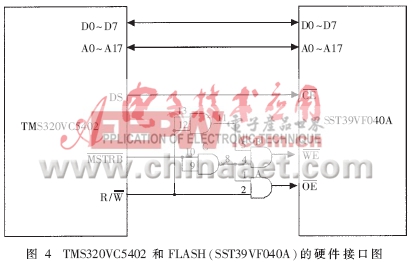

2.2.2 实现自举硬件接口电路的设计

根据设计的需要,FLASH采用TI公司的SST39VF040A。图4为TMS320VC5402和FLASH的硬件接口电路[5]。由于TMS320VC5402和FLASH都是3.3V供电,接口中TMS320VC5402的D0~D7直接与FLASH的D0~D7相连,二者的地址信号线A0~A17也相连,TMS320VC5402的DS接FLASH片选端CE,TMS320VC5402的 和

和 经逻辑组合后接FLASH的

经逻辑组合后接FLASH的 。由于FLASH是512K×8bit的芯片,地址线为18位,超过了Bootloader所能访问的16位地址空间,而FLASH在被访问时,高位的地址线必须是确定态(高或低),所以在访问FLASH之前必须先对扩展页寄存器XPC进行初始化,以使超出16位的地址线也具有确定的状态,通过设计逻辑电路满足读写时序要求。

。由于FLASH是512K×8bit的芯片,地址线为18位,超过了Bootloader所能访问的16位地址空间,而FLASH在被访问时,高位的地址线必须是确定态(高或低),所以在访问FLASH之前必须先对扩展页寄存器XPC进行初始化,以使超出16位的地址线也具有确定的状态,通过设计逻辑电路满足读写时序要求。

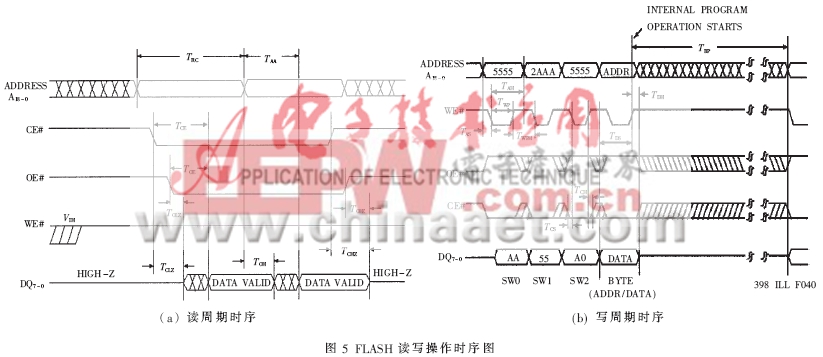

2.2.3 FLASH读写操作

2.2.3.1 FLASH的读操作

FLASH的读操作基本上与普通的存储器读操作一致,具体的读周期时序如图5(a)所示。当CE与OE为低电平时,DSP就可以读取FLASH中的数据。要注意的是, 信号是由DSP产生的,在读取一个数据后,DSP必须在

信号是由DSP产生的,在读取一个数据后,DSP必须在 引脚给出一个上升沿标志,通知FLASH已经将数据读取,之后FLASH会自动将下一个存储单元的数据送到数据线上,重复以上过程,DSP可以将需要的数据依次读出。

引脚给出一个上升沿标志,通知FLASH已经将数据读取,之后FLASH会自动将下一个存储单元的数据送到数据线上,重复以上过程,DSP可以将需要的数据依次读出。

2.2.3.2 FLASH的写操作

FLASH的写操作相对复杂一些,它需要一串命令序列,通过对FLASH的命令寄存器写入相应的命令字来完成写入和擦除。对应的写操作时序图如图5(b)所示。

3 主机接口(HPI)通信设计

主机接口[6-7](HPI,Host Port Interface)是TMS320C54x系列定点芯片内部具有的一种接口部件,主要用于DSP与其他总线或CPU进行通信。HPI接口通过HPI控制寄存器(HPIC)、地址寄存器(HPIA)、数据锁存器(HPID)和HPI内存实现与主机通信。其主要特点有:接口所需外围硬件很少;HPI单元允许芯片直接利用一个或两个数据选通信号、一个独立或复用的地址总线以及一个独立或复用的数据总线接到微控制单元MCU上;主机和DSP可独立地对HPI接口进行操作;主机和DSP握手可通过中断方式来完成。

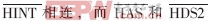

由于本数据处理系统采用双CPU(DSP+MCU),经A/D转换后的信号先保存在DSP的存储器中,DSP和MCU之间需进行数据通信,同时HPI方式还能让单片机共享DSP内部的双口RAM,弥补单片机内部RAM不足等缺陷。在硬件设计时,要注意单片机89C51是+5V供电,DSP是+3.3V供电,需进行电平转换。

图6为89C51与DSP HPI通信硬件接口图。其中89C51的端口P0.1~P0.7与HPI的8位数据线(HD0~HD7)相连作为数据传输通道,P2.0~P2.4设置为输出来控制HPI接口的操作。其中P2.0为读写控制选通信号连接 P2.1连接字节识别信号HBIL,控制读写数据是属于16位字的第一字节还是第二字节;P2.2和P2.3分别连接HCNTL0和HCNTL1以实现对HPIC、HPIA和HPID寄存器的访问;P2.4连接

P2.1连接字节识别信号HBIL,控制读写数据是属于16位字的第一字节还是第二字节;P2.2和P2.3分别连接HCNTL0和HCNTL1以实现对HPIC、HPIA和HPID寄存器的访问;P2.4连接 作为数据选通信号来锁存有效的HCNTL0/1、HBIL和

作为数据选通信号来锁存有效的HCNTL0/1、HBIL和 信号;P2.5与

信号;P2.5与 相连作为片选信号;INT0作为输入与HPI的主机中断信号

相连作为片选信号;INT0作为输入与HPI的主机中断信号 一直接高电平。在数据交换过程中,89C51向HPI发送数据时通过置TMS320VC5402的HPI控制寄存器HPIC中的DSPINT位为1来中断TMS320VC5402;89C51接收来自HPI的数据时通过查询方式,当TMS320VC5402 DSP准备发送数据时置

一直接高电平。在数据交换过程中,89C51向HPI发送数据时通过置TMS320VC5402的HPI控制寄存器HPIC中的DSPINT位为1来中断TMS320VC5402;89C51接收来自HPI的数据时通过查询方式,当TMS320VC5402 DSP准备发送数据时置 为低,89C51查询到INT0为低时调用接收数据子程序来实现数据的接收。

为低,89C51查询到INT0为低时调用接收数据子程序来实现数据的接收。

4 系统调试及结果

为了调试该系统,可以在A/D转换器输入端输入一个确定信号,观察其采集和输出的情况。为此设计了A/D转换和数据处理程序。将信号发生器DG2000的输出转换后存入DSP数据存储器的连续单元中,设计了简单明晰的频率计算程序,通过零点检测计算出信号的频率,最终结果经HPI传送给单片机并显示出来。

测试中所用仪器为:RIGOL系列信号发生器DG2000。

将信号发生器DG2000的输出经一个保护电阻接到A/D输入端。波形输入和LED显示界面如图7所示。

通过对不同信号和不同算法程序运行的实践,LED的输出显示均与输入量相符合,证明系统工作稳定。由于本采集系统具有高速转换器和DSP硬件基础,只需根据采集信号种类的不同及输出要求的不同设计相关的算法软件,对所获得信号进行处理即可。可以在各种工业生产过程和仪器仪表中应用该系统,还可利用RS232串口实现与上位PC机之间的通信,对数据做进一步的处理。

评论