基于DSP的视频图像语音传输系统的硬件设计

随着科学技术的高速发展,视频图像和语音数字化处理在军事、科研、工农业生产、医疗卫生等领域的应用越来越广泛。早期的粮情监测主要是基于对粮仓温度、湿度的采集观测。随着粮情系统的进一步完善,人们提出了更高要求,希望对粮仓内部进行实时图像语音监控,进一步加强对虫害和火灾观测和预防。本文所采用的基于TMS320C6201的视频图像语音传输系统就是应用于粮情的监测,在满足以上要求的前提下设计完成的。

图像语音的压缩传输系统有二种基本的实现方法:一种是基于微机实现,图像语音处理系统通过PCI总线以插卡的形式集成在微机系统中,数据通过PCI总线或卡上所带的接口进行交换和传输;另一种是脱离了微机而独立运行,利用微处理芯片对图像语音进行数字化压缩传输。本文介绍的设计采用了后一种方法。

1 系统的组成和基本原理

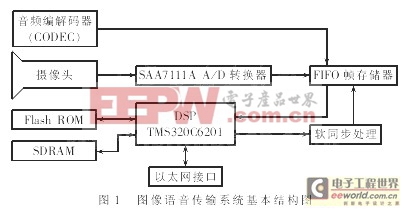

一个完整的视频图像语音传输系统不但要具备对图像语音信号的采集功能,还要求完成对采集上来的图像语音信号的分析及处理算法(如图像压缩等),最后采用一定的媒质将处理好的信号传输到终端主机显示。视频图像语音信号的分析及处理算法的运算量很大,同时又要满足实时显示的要求,因此采用了高速DSP芯片作为数据核心的处理单元。系统的基本结构模型如图1所示。

2 硬件结构

2.1 模拟视频输入接口设计

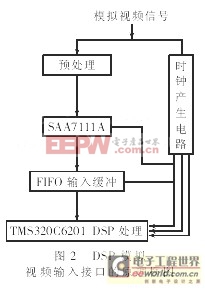

(1)视频采样要求。模拟视频输入接口电路的作用是对输入的模拟视频信号进行预处理,并将其数字化。视频采样有2个重要指标:采样分辨率和采样频率。采样分辨率代表图像灰度量化的等级,位数越多,图像层次越丰富,同时图像数据量也越大;采样频率决定可数字化后图像的空间分辨率,为了不失真,它必须大于模拟视频信号的频谱中最高频率的2倍。另外,还要求模拟视频输入接口所引入的系统噪声最小。DSP模拟视频输入接口的原理框图如图2所示。

(2)模拟视频解码模块。视频解码模块的作用是将复合视频、YC分量等模拟视频信号进行A/D转换,提取其中的同步和时钟信号,所有转换电路均集中在一块芯片内。根据以上要求,选择Philips公司生产的可编程的数字视频A/D变换器SAA7111A,它有4路模拟输入和2路模拟信号处理通道,可以通过编程选择信号制式。输出信号可以是YUV411(12位)、YUV422(16位)、YUV422(CCIR-656)(8位)、RGB(5、6和5)(16位)或RGB(8、8和8)(24位)格式。系统通过I2C总线对SAA7111A编程,完成初始配置工作。来自摄像头的模拟信号,首先在模拟信号控制下,进行信号箝位、模拟放大、反混淆滤波、A/D转换,然后将得到的8位亮度信号和8位色度信号分别送往亮度处理电路和色度处理电路进行处理,产生16位的YUV信号。Y(7:0)为8位数字亮度信号,UV(7:0)为不同颜色(B-Y和R-Y)复用信号。信号输出格式由I2C总线控制(YUV信号输出格式由I2C总线控制电路决定),帧时序由HREF信号控制。在系统中将采用带有I2C接口的、与51系列兼容的单片机T89C51IC2对SAA7111A进行控制,即对模拟视频前端SAA7111A的采样率、箝位电平、锁相环等进行编程设置,以使整个视频输入接口电路按照预先设计的方式工作。

(3)采用FIFO作为实时图像数据输入缓冲器。从性能上来说,普通型的帧存储体在采集的同时不能读取采集数据。虽然采用双端口RAM也可以解决并发访问的问题,但它所必需的地址译码和占用大段的主存储器映射空间(或繁杂的页面切换)是不可忽视的实际问题。从对采集到的数据的处理方式可以看出,对于单纯采集应用(不需要对数据做诸如叠加等预处理工作),其系统缓存单元在结构上相当于先进先出(FIFO)队列,即按信号时间顺序先采集的数据先被主处理芯片读取及处理。所以采用专门的FIFO芯片可去掉复杂的缓存器帧内地址译码电路,大大简化了系统设计。FIFO(IDT72V3640)用于向TMS320C6201传输经SAA7111A转换后的16位实时图像数据VPO(0:15)。FIFO不存在地址线的问题,所以不用连接地址线。

2.2 音频编解码器的选取

采用Crystal公司的CS4231A芯片作为核心音频编码解码器(CODEC)模块。CS4231A多媒体芯片为系统提供一个灵活、通用的音频前端。它是一个16位立体声器件,包含完整的片上滤波、模拟混音和可编程控制的增益和衰减调节。CS4231A支持8、9.6、11.025、16、22.05、32、44.1、48kHz等通用的采样频率,如此宽范围的采样频率可以适应从电信到音频的各种应用需求。CS4231A采用频率分别为16.9344MHz和24.576MHz的2个晶振来作为采样频率的时钟源。

CS4231A同时提供了并行和串行接口,支持DMA及中断工作方式,因而可以通过多种方式与DSP进行连接。这里采用的是其中最有效的方式:即串行接口传输音频数据,并行接口传输控制信息。CS4231A使用与DSP的McBSP(多通道缓存串行口)相兼容的串行音频数据接口,这种接口方式为串行音频数据提供了一个专用通道而不必占用DSP的EMIF的带宽。在串行数据流中,CS4231A先传输左声道数据然后传输右声道数据,并且传输时高位在前(与McBSP的工作方式相兼容)。CS4231A串口通过多路复用芯片CBT3257的4个2选1复用器连接到DSP的McBSP,这一设置使McBSP可以与板上的CS4231A相连,也可以在任一时刻与自己的具体应用子板相连。CS4231A包含1个8位宽度的并行控制/状态接口,通过把接口寄存器映射到DSP的EMIF空间来进行控制和状态读取。这样就使控制接口和音频数据相分离,避免了在单个码流上的信号复用,简化了软件驱动设计。CS4231A是5V器件,DSP是3.3V器件,它们相互连通后得并行控制信号,并且必须通过总线收发器进行信号转换。

CODEC模块支持线性和话筒的多路输入:音频的放大器用来对话筒输入信号进行预防和滤波;线性输入经过无源滤波、交流耦合送入CS4231A,输入插座可以用来连接立体声源,通过软件可以独立控制左、右输入声道的选择和各自的增益。CODEC还包含一个可通过DSP软件控制衰减的线性输出。

2.3 系统扩展存储器接口设计

(1)程序存储及数据预置。由于对不同的成像条件,要求其视频运动估算和图像处理算法能够自动适应,所以必须存储多种算法备选。因此要求选用大容量的存储器或者多片小容量的存储器。片外8位或16位的程序存储器必须配置在TMS320C6201EMIF(外存接口)的CE1空间。这是因为:①系统复位后只能从CE1载入引导程序。②EMIF的4个存储空间中,只有CE1可以与8位或16位的“窄存储空间”接口。根据预存程序和数据的大小估计,采用相应容量的Flash ROM。

(2)采用SDRAM扩充系统外部数据动态存储单元。在高速DSP视频处理系统中,数据存储器的作用是暂存图像数据。而高速DSP器件TMS320C6201的片上数据RAM只有3Mb,无法保证大量数据的处理,因此必须扩充片外数据存储器。其原因是:①系统对外部数据存储器的容量要求。假如图像要求分辨率为320×240,每个采样点的灰度层为8位,则1帧单色图像所占的的存储空间为256KB,三色图像为3×256KB。如果处理算法涉及到n帧图像,存储空间就为n倍。一般情况下,DSP视频处理系统工作时允许在多种算法之间进行选择,它所要求的数据存储容量应该以涉及到帧数最多的算法来估计。②视频图像处理过程中图像数据的存放安排。根据本系统的特点,在内部数据RAM和片外数据RAM的构成中,为了获得较快的处理速度,必须注意数据的存放位置。这里,针对视频图像处理算法的性质给出存放数据的原则是:(a)帧内处理算法。处理时所用到的只是当前帧的一部分数据。需要存放的数据量很小,此时待处理以及已处理的视频数据可以同时存放于片上RAM。(b)帧间处理算法。涉及到的数据量超过2帧以上时,则待处理的数据及处理过的数据均存于SDRAM,片内RAM只存放运算的中间结果。(c)片上数据的存放应注意地址的冲突问题。③SDRAM型号的选取。出于为系统图像压缩处理充分预留空间的需要,选用型号为MT48LC8M16A2(16MB)的SDRAM,根据DSP数据线为32位宽,选用2片MT48LC8M16A2进行扩展,总的扩展存储容量为32MB。

2.4 系统以太网接口设计

本系统采用以太网作为传输介质。但目前还未有自带以太网接口的DSP。所以采用以太网控制器RTL8019AS与DSP构成以太网互连接口。

RTL8019AS是台湾Realtek公司生产的以太网控制器,支持IEEE802.3;支持8位或16位数据总线;内置16KB的SRAM,用于收发缓冲;全双工,收发同时达到10Mbps;支持10Base5、10Base2、10BaseT,并能自动检测所连接的介质,在ISA总线网卡中占有相当比例。RTL8019AS与主机有3种接口模式:跳线模式、PnP模式和RT模式。

为了简化DSP网络接口的软、硬件设计,不使用远程自举加载功能,并且选用跳线接口模式。用DSP的扩展I/O口代替跳线器对RTL8019AS进行初始化配置。这样既省去了93C46的功能,又避免了跳线器更改资源配置的麻烦。RTL8019AS的总线接口与ISA总线兼容。虽然不能与DSP的外部总线直接接口,但是只要进行一些简单的逻辑变换就可以实现直接接口。另外,DSP的总线电平为3.3V,而RTL8019AS的接口电平为5V,因此二者接口时要使用电平转换器。

2.5 电源模块及复位电路的设计

TMS320C6201的电源采用2种电压供电:即内核电压1.8V,I/O电压3.3V。DSP对这2个电压有上电顺序的要求,要求内核电源(CVdd)先于I/O电源(DVdd)上电。为此在电源模块的选用上,采用二套电源模块,通过拨码开关构成互补模式,这样就能够保证系统在一套电源模块失效时还能够继续工作,增强了系统的可靠性。这二套电源模块分别是:PT公司针对TI公司的DSP生产的电源模块PT6405B(5V~3.3V)和PT6502B(5V~1.8V),该类型的电源模块具有稳定、额定电流大(3A)等优点;另一套是由MAXIM公司生产的、采用带有同步整流器的DC-DC转换器MAX1742(输出电流1A)和MAX1644(输出电流2A),配合适当的外围电路分别对DSP的I/O和内核供电。

为了保证TMS320C6201芯片在电源低于要求的电平时不会产生不受控制的状态,系统中应加入电源监控电路,以确保DSP在系统加电过程中及电源电压低于一定门限值时始终处于复位状态。监控电路采用TI公司的TPS3307-33d(它还可接一手动复位开关)。

3 结束语

本文设计的基于TMS320C6201的视频图像语音传输系统,与采用专用芯片加FPGA构成的系统比较,其硬件性能有了很大的提高。在软件实现上也更加灵活多样、修改方便。该系统结构紧凑,可靠性高,实时性强,能够广泛地运用于军事、科研、工农业生产和医疗卫生等领域。

评论