基于DM9000A的以太网接口设计与实现

摘要:为了实现DSP与外围设备进行以太网数据通信,采用了一种基于网络控制芯片DM9000A的DSP以太网接口实现方式。它以TI公司的DSP处理器和DM9000A网络芯片为硬件平台,通过DSP总线控制DM9000A内部寄存器,完成DM9000A的初始化以及底层以太网数据的发送接收,并对TCP/IP协议进行裁剪,包括IP,ARP,ICMP,UDP和TCP等协议,实现了适用于DSP设备的以太网数据通信功能。

本文引用地址:https://www.eepw.com.cn/article/234974.htmDSP(Digital Signal Processor)是一种独特的微处理器,是以数字信号来处理大量信息的器件。它强大的数据处理能力和高运行速度,是最值得称道的两大特色。随着网络技术的发展,在工业控制、智能仪器、智能家庭等领域,越来越多的DSP设备要求具有以太网通信功能,以便与外部网络设备进行数据通信。以太网控制芯片是以太网接口的核心器件,其性能是影响网络性能的关键因素之一,如何正确使用网络控制器是设计以太网接口的关键。本文采用处理器+以太网控制芯片+TCP/IP协议的DSP以太网接入方式,设计并实现了基于DSP的精简TCP /IP协议栈,并固化在DSP内,无需操作系统也可运行。

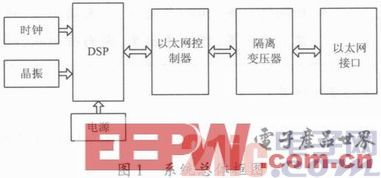

1 总体设计

本系统使用32位DSP处理器TMS320F28335和以太网控制芯片DM9000A为核心,DSP控制整个系统的运行,DM9000A实现网络传输的底层功能。并对TCP/IP协议栈自行裁剪,构成了DSP的以太网接口,实现了网络通信。其系统总体框图如图1所示。

2 系统硬件设计

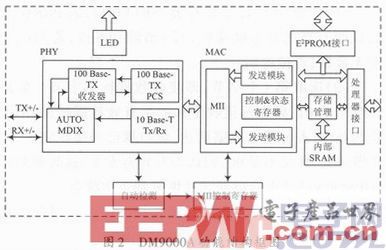

2.1 DM9000A功能结构

DM9000A是DAVICOM公司推出的一款高度集成、低成本的快速以太网控制器,实现以太网媒体介质访问层(MAC)和物理层(PHY)的功能。该芯片具有通用的处理器接口,片内集成了10/100M自适应的PHY,内部含有16 KB SRAM用于接收/发送的FIFO缓存,3.3 V供电,并且支持IEEE 802.3以太网传输和8/16接口的两种主机工作模式协议。功能结构如图2所示。

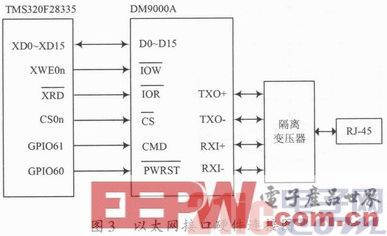

2.2 接口电路的连接

接口电路主要由DSP、以太网控制芯片DM9000A、隔离变压器和RJ-45构成。DSP控制整个系统的运行,DM9000A实现以太网数据的底层传输。隔离变压器的主要作用:其一,可以增强信号,使其传输距离更远;其二,使芯片端与外部隔离,增强抗干扰能力,并对芯片端起保护作用;其三,当接到不同电平(如有的PHY芯片是2.5 V,有的PHY芯片是3.3 V)的网口时,不会对彼此设备造成影响。RJ-45接口可用于连接RJ-45接头,适用于由双绞线构建的网络,这种是最常见的以太网接口。DM9000A采用16位接口模式,数据地址复用总线D0~D15与DSP总线XD0~XD15相连;DM9000A的写信号引脚与DSP的XWE0n相连;读信号引脚与DSP的读引脚相连;DM9000A的片选信号引脚与DSP的CS0n相连;DM9000A的访问类型引脚CMD与DSP的普通I/O口GPIO61相连,高电平访问DM9000A的数据端口,低电平访问地址端口;DM9000A的复位引脚与DSP的GPIO 60相连;DM9000A的物理层接口TX+,TX-,RX+,RX-通过隔离变压器连接RJ-45至以太网。其以太网接口硬件连接如图3所示。

3 系统软件设计

网络接口的软件主要有DM9000A驱动程序设计和上层通信协议程序设计两个部分。DM9000A驱动程序设计主要是通过TMS320F28335控制总线配置DM9000A内部寄存器,完成对DM9000A初始化、以太网数据帧的发送和以太网数据帧的接收三部分。上层通信协议程序设计是对TCP/IP栈裁剪移植,主要完成对接收到的以太网数据帧进行解析并处理,并把要发送的数据封装成以太网数据,然后发送。

3.1 DM9000A驱动程序设计

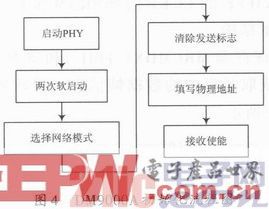

3.1.1 DM9000A初始化

DM9000A正常工作需要在上电后对内部寄存器进行初始化,具体流程如下:

(1)启动PHY。设置通用寄存器GPR(1FH)的GEPIO0=0。

(2)进行两次软启动。设置网络控制寄存器NCR(00H)的RST=1,10μs后RST=0,同样的操作进行两次。

(3)选择网络模式。设置NCR的LBK=00,设置网络工作模式为正常模式。

(4)清除发送标志。设置网络状态寄存器NSR(01H)WAKEST=1,TX2END=1,TX1END=1。

(5)写6 B的以太网节点地址到物理地址寄存器PAR(10H~15H)中。

(6)设置中断屏蔽寄存器IMR(FFH)的PAR=1,使能指针自动跳回,当SRAM读/写指针超过SRAM的大小时,指针自动跳回起始位置;PRI=1,使能数据包接收中断。

(7)设置接收控制寄存器RCR(05H)的WTDIS=1,看门狗定时禁止;DSI_LONG=1,丢弃长数据包;DIS_CRC=1丢弃CRC校验错误的数据包;RXEN=1,使能接收功能。

初始化流程如图4所示。

完成上述初始化步骤后,DM9000A就处于正常工作状态,可以收发数据包。若有异常发生,就需要重复上述步骤,重启DM9000A以使芯片恢复到正常状态。

3.1.2 数据帧发送

DM9000A内部有16 KB的SRAM作为接收/发送数据的缓存区,其中前3 KB的空间,地址从0x0000H~0x0BFFH,用来缓存需要发送的数据。

数据发送的具体步骤如下:

(1)利用写操作寄存器MWCMD(F8H),将需要发送的数据帧写入DM9000A的发送缓存区。

(2)将数据帧长度写入长度寄存器TXPLL(FCH)和TXPLH(FDH)。

(3)设置发送控制寄存器TCR(02H),TXREQ=1,数据帧开始发送。

(4)检查网络状态寄存器NSR(01H)的TX2END和TX1END位,判断此帧数据是否发送完。

数据帧发送流程图如图5所示。

tcp/ip相关文章:tcp/ip是什么

双绞线传输器相关文章:双绞线传输器原理

评论