多种降低内核功耗的技术

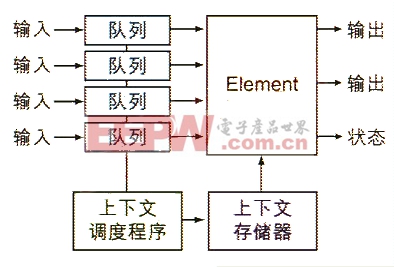

Element CXI使用了介于FPGA基本功能单元与完整处理器的计算模块之间的网状计算单元(见图)。Element CXI模块使用数据流架构实现异步操作。

PA Semi公司基于64位PowerPC的PWRficient内核的功耗几乎降低了一个数量级。一个单内核功耗稍高于3W,多内核解决方案最多可使用16个处理器。该设计采用了大量时钟区域,可以根据系统中运行的线程尽量减少活动区域的数量。

Handshake Solutions公司则采取了完全不同的无时钟技术。ARM的ARM996HS处理器采用的就是Handshake Solutions公司这种独特的无时钟IC设计技术。无时钟设计的功耗平均要比类似的ARM968E-S低2.8倍。ARM996HS还具有更低的电磁辐射。

|

| Element CXI采用这种类似FPGA功能单元的16位功能块实现复杂的系统。 |

Tarari则另辟奚径,通过它的Windows Media加速器实现高性能低功耗解决方案。该公司在这些产品线上有许多解决方案,包括可以分担XML处理等任务的RAX4模式匹配处理器。像Tarari的T9000专用处理器可以将性能提高1到2个数量级,从而使传统的主处理器能集中处理数据移动等其它任务。

评论