基于MATLAB的1.5位/级10位流水线结构模数转换器系统仿真(图)

目前,数字信号处理技术在许多通信系统的信息传输中得到了越来越广泛的应用,而在要处理的模拟信号与数字信号处理系统之间需要一个模数转换界面,把模拟信号转换成数字信号,以供数字信号处理系统进行信号处理。流水线结构模数转换器凭借其高速度、高精度得到了广泛的应用。本文以1.5位/级10位流水线模数转换器系统为仿真对象,对其性能进行了仿真。

1.5位/级10位流水线模数转换器结构分析 1.5位/级10位流水线模数转换器采用了图1所示的结构,共九级实现10位数字输出。每级流水线包括子模数转换器(adc)、子数模转换器(dac)、减法电路和增益电路。输入的模拟信号经采样保持(s/h)后送到第一级,每级子adc产生两位数字输出,同时保持的输入信号减去由子dac变换输出的模拟量,余量被残差放大器放大2倍后送入下一级。其中前八级,采用相同的1.5位/级,第九级则是一个标准的2位flash adc。由九级产生的18位数字量送到数字校正电路,产生10位数字输出。

1.5位/级10位流水线模数转换器采用了图1所示的结构,共九级实现10位数字输出。每级流水线包括子模数转换器(adc)、子数模转换器(dac)、减法电路和增益电路。输入的模拟信号经采样保持(s/h)后送到第一级,每级子adc产生两位数字输出,同时保持的输入信号减去由子dac变换输出的模拟量,余量被残差放大器放大2倍后送入下一级。其中前八级,采用相同的1.5位/级,第九级则是一个标准的2位flash adc。由九级产生的18位数字量送到数字校正电路,产生10位数字输出。

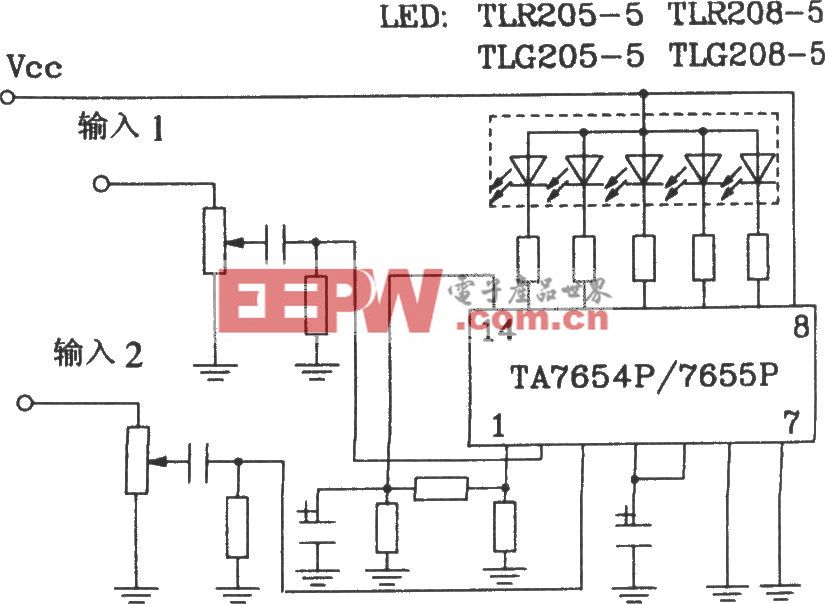

这种流水线结构的每级应用框图如图2所示。为了简单一些,图中只画了单边结构,实际应用中是采用全差分结构。这里 采用了开关电容电路,在两相不交叠时钟下工作。在第一相时钟其间,输入信号vin被加到子adc上,子adc有两个比较电压,vref/4,-vref/4。输入信号的变化范围是从-vref到+vref(差分结构)。同时,输入信号vin也被加到采样电容cs和cf上。在第一相时钟结束时,vin通过cs和cf被采样,并且子adc的输出被锁存。在第二相时钟时,cf另一端接到运放的输出端,形成负反馈。而cs的另一端则接到dac的输出端。通过这个结构在vo端将产生残差输出。子adc的输出通过一个模拟多路器来选择dac的输出电压vdac。1.5位/级流水线模数转换器的每级传输函数如下。

采用了开关电容电路,在两相不交叠时钟下工作。在第一相时钟其间,输入信号vin被加到子adc上,子adc有两个比较电压,vref/4,-vref/4。输入信号的变化范围是从-vref到+vref(差分结构)。同时,输入信号vin也被加到采样电容cs和cf上。在第一相时钟结束时,vin通过cs和cf被采样,并且子adc的输出被锁存。在第二相时钟时,cf另一端接到运放的输出端,形成负反馈。而cs的另一端则接到dac的输出端。通过这个结构在vo端将产生残差输出。子adc的输出通过一个模拟多路器来选择dac的输出电压vdac。1.5位/级流水线模数转换器的每级传输函数如下。

1.5位/级10位流水线模数转换器的仿真模型

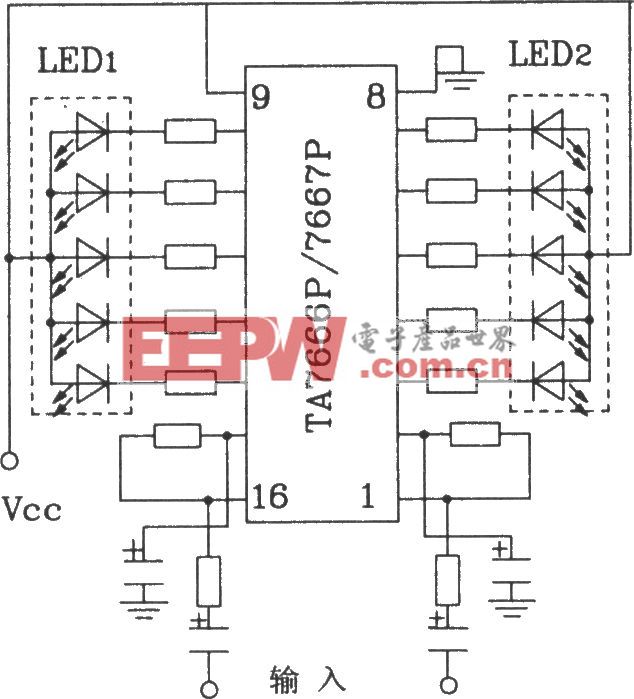

本文建立的10位流水线模数转换器是由九级级联而成的,前8级采用了相同的结构。下面给出了前8级每级的模型以及第九级的模型,如图3所示。

图(a)中子adc模块是对采样以后的模拟信号与参考电压进行比较输出两位的数字量,同时这两位的数字量经译码器译码后送到子dac,作为子dac进行数模转换的依据。子dac模块主要是根据子adc提供的数字量进行模数转换,输出一个模拟量送到加法器。图(b)是一个标准的2位flash结构的模数转换器,其原理及实现的功能跟上述子adc基本相同。

1.5位/级10位流水线模数转换器系统的仿真

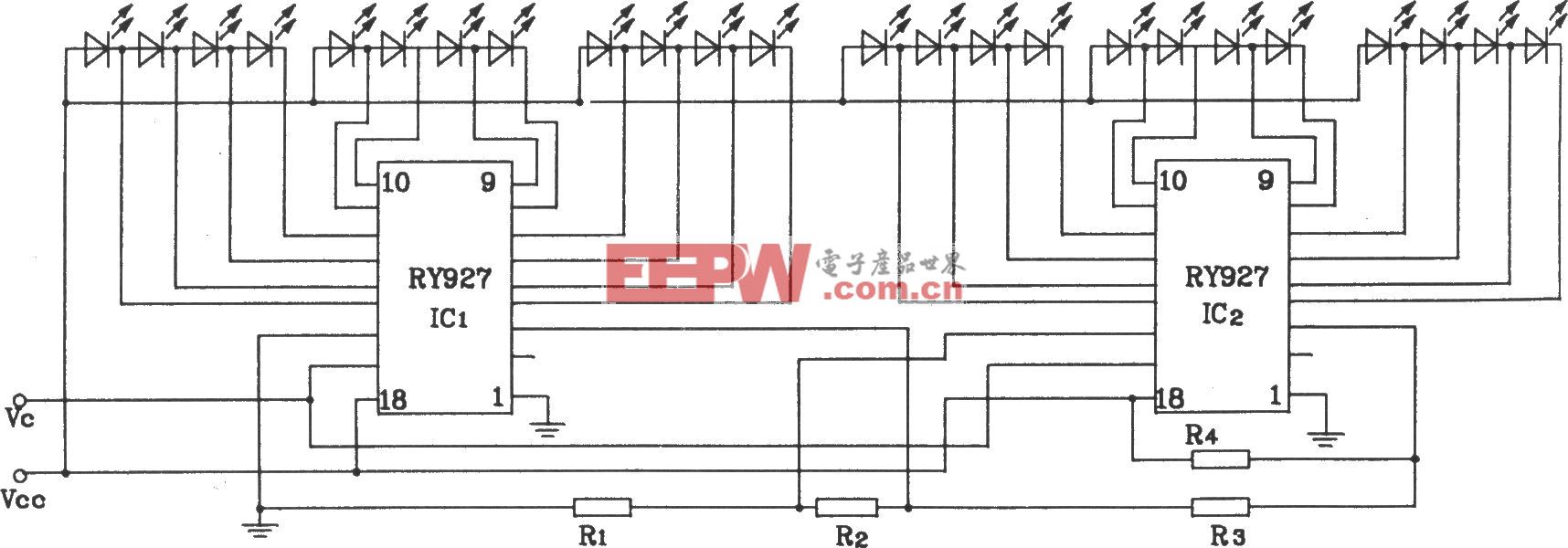

图4是1.5位/级10位流水线模数转换器的九级系统模型,其中上面的前8个框图结构与图3中的图(a)相同,第九个框图与图(b)相同。图中的下半部分为数字校正电路,因为有了这部分数字校正电路,使模数转换器对子adc中比较器的要求大大降低,其误差可以达到±1/2lsb。

评论