松下32nm HKMG工艺分析出炉

日本松下公司曾表示其首款基于HKMG工艺的32nm芯片产品将于2010年的10月份上市。而经过长时间的等待之后,最近知名芯片技术分析公司 Chipworks的分析师Dick James终于发表了对松下这款32nm HKMG芯片产品的研究报告,报告称该公司经过分析已经核实松下的这款32nm HKMG芯片产品采用的是gate first工艺制作。至于为什么号称去年10月份已经上市,而到现在外界才拿到这款芯片进行分析,Dick James则解释称:“这款芯片产品确实如松下所承诺的那样是在去年10月份即第44周上市的,不过由于产品流通环节繁琐,因此我们到最近才得到了有关的实际产品。”

松下当年还曾经推出过基于HKMG工艺的45nm制程产品,当时其这款产品上市的时间和Intel的HKMG 45nm产品非常接近。不过在32nm节点,Dick James则表示,松下推出同类产品的步调则“要比Intel慢了一年左右,不过据我们所知,松下应该是首家开始批量生产32nm HKMG芯片产品的厂家。”

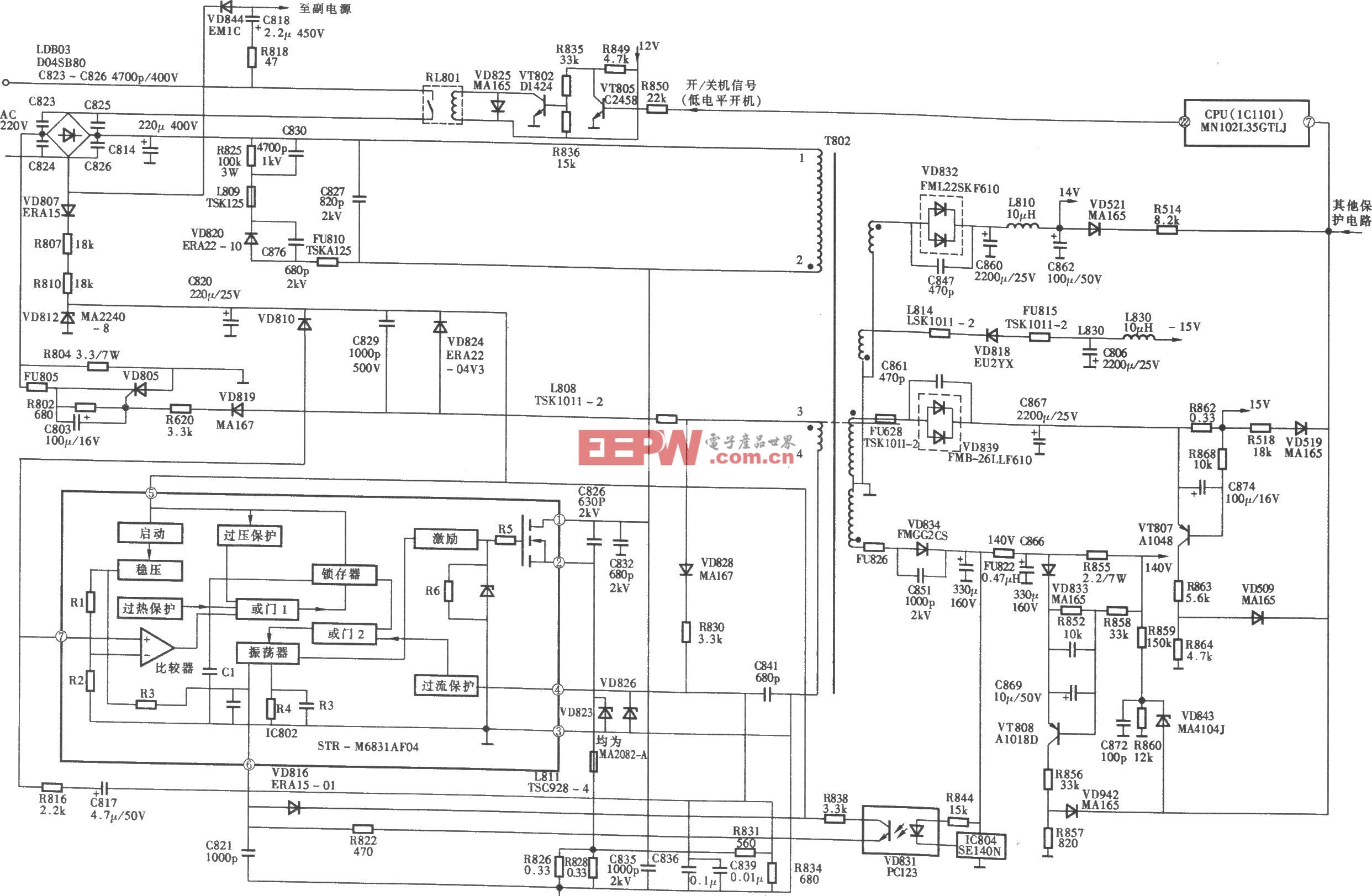

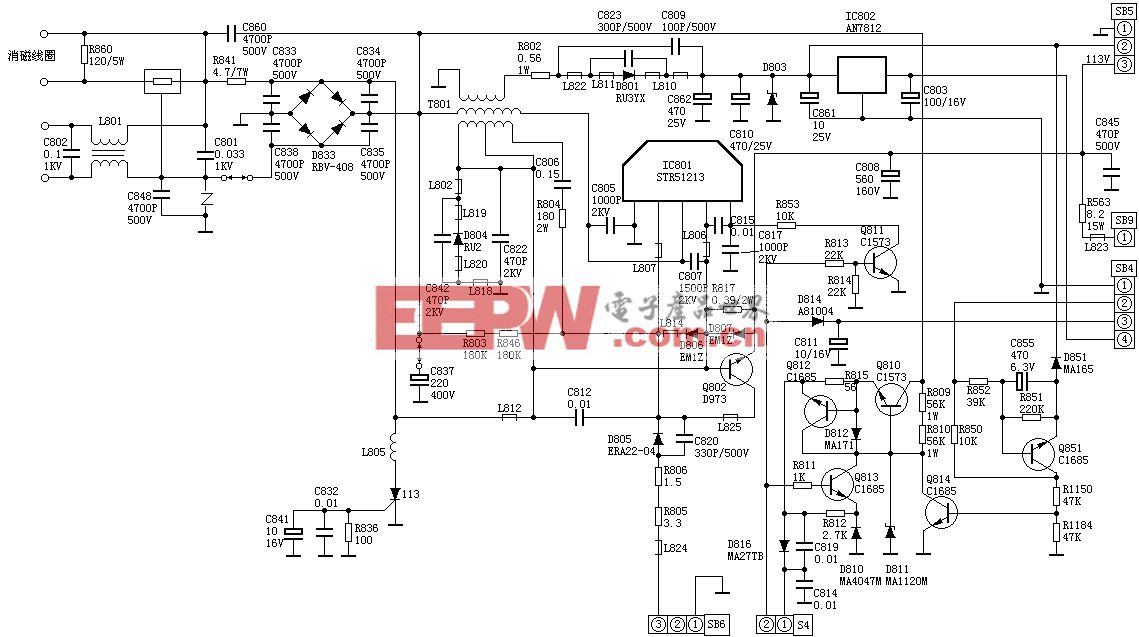

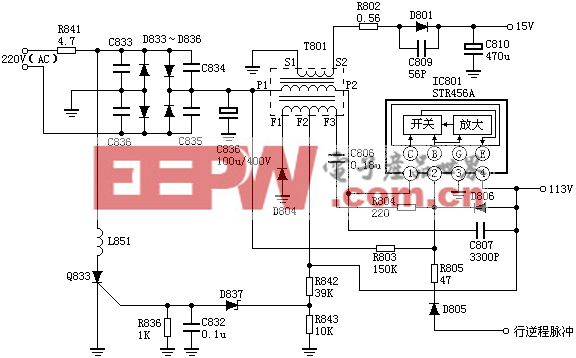

对松下32nm HKMG芯片产品的分析显示,这款产品“采用九层金属互连层设计(8层为铜互连,1层为铝互连),互连层电介质则采用了low-k和extra-low-k两种电介质混合的结构。芯片核心尺寸约45平方毫米,采用常规的FC-BGA封装形式。最小的金属触点节距尺寸据松下公布的数据为120nm,不过我们在之前的分析中得出的实际节距尺寸则是125nm左右。”

松下还宣称其32nm HKMG产品的性能提升了40%,同时功耗则减少了40%,芯片面积则缩小了30%。

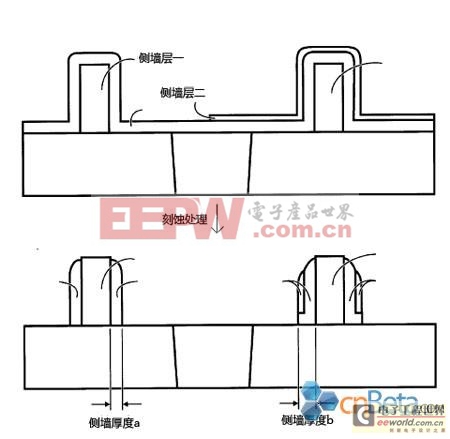

分析文章进一步指出:“可见松下32nm HKMG芯片的栅极采用多晶硅栅+底部TiN金属功函数层的结构,在TiN层的底部可以观察到high-k绝缘薄层结构。另外,值得注意的是这款产品的栅极采用了双侧墙工艺(dual-spacer),双侧墙工艺有时又被称为差动式偏移隔离侧墙(differential offset spacer)技术。另外在晶体管的漏源极顶部可观察到一层薄薄的氮化物,这显示松下这款产品的high-k绝缘层底部和硅沟道顶部之间可能采用了氮氧化物(推测应该是SiON)中间层。”

dual-spacer并不算是一项较新的技术,因此在近年的报道中较少被提及,这种技术的实质是通过调节侧墙厚度来调整栅极的长度,从而控制漏源极扩散区和栅极的重合程度,以达到控制沟道有效长度,及减小漏源极与栅极的寄生电容的作用。

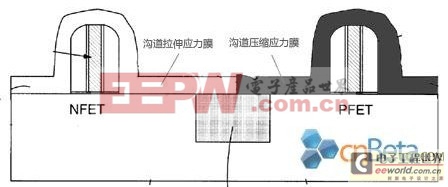

“栅极和漏源极的金属化工艺(salicide)则采用常见的镍金属化掺杂铂的工艺。不过松下32nm HKMG产品上产生应变力的机制则比较不明显,他们采用的既不是基于栅极氮化层的技术,也不是嵌入式SiGe技术,另外也没有使用双应变力膜(dual-stress liner:即用两层分别可对沟道施加拉伸应力和压缩应力的氮化膜控制沟道应变力)技术。”

回顾松下当年的45nm HKMG工艺“似乎没有使用任何沟道应变增强技术,PMOS沟道迁移率增强方面则只采用了100>晶向设计(普通芯片为110>晶向,但100>晶向的PMOS沟道空穴迁移率相对较高,当然晶向工程的效能与应变工程是无法相比的)。可见松下与Intel的45nm HKMG工艺其诉求的重点不同,Intel侧重于晶体管性能的提升,而松下则侧重于集成度的提高和成本的下降.而到32nm节点,松下的侧重点又增加了high-k绝缘层的使用和由此带来的低功耗/低漏电。”

评论