基于可编程逻辑器件PLD的数字电路设计方案

0 引 言

可编程逻辑器件PLD(Programmable Logic De-vice)是一种数字电路,它可以由用户来进行编程和进行配置,利用它可以解决不同的逻辑设计问题。PLD由基本逻辑门电路、触发器以及内部连接电路构成,利用软件和硬件(编程器)可以对其进行编程,从而实现特定的逻辑功能。可编程逻辑器件自20世纪70年代初期以来经历了从PROM,PLA,PAL,GAL到CPLD和FPGA的发展过程,在结构、工艺、集成度、功能、速度和灵活性方面都有很大的改进和提高。

随着数字集成电路的不断更新和换代,特别是可编程逻辑器件的出现,使得传统的数字系统设计方法发生了根本的改变。可编程逻辑器件的灵活性使得硬件系统设计师在实验室里用一台计算机、一套相应的EDA软件和可编程逻辑芯片就可以完成数字系统设计与生产。

1 Max+plusⅡ简介

Max+plusⅡ是一种与结构无关的全集成化设计环境,使设计者能对Altera的各种CPLD系列方便地进行设计输入、快速处理和器件编程。Max+plusⅡ开发系统具有强大的处理能力和高度的灵活性,其主要优点:与结构无关、多平台、丰富的设计库、开放的界面、全集成化、支持多种硬件描述语言(HDL)等。

数字系统的设计采用自顶向下、由粗到细,逐步分解的设计方法,最顶层电路是指系统的整体要求,最下层是具体的逻辑电路的实现。自顶向下的设计方法将一个复杂的系统逐渐分解成若干功能模块,从而进行设计描述,并且应用EDA软件平台自动完成各功能模块的逻辑综合与优化,门级电路的布局,再下载到硬件中实现设计,具体设计过程如下。

1.1 设计输入

Max+plusⅡ支持多种设计输入方式,如原理图输入、波形输入、文本输入和它们的混合输入。

1.2 设计处理

设计输入完后,用Max+plusⅡ的编译器编译、查错、修改直到设计输入正确,同时将对输入文件进行逻辑简化、优化,最后生成一个编程文件,这是设计的核心环节。

1.3 设计检查

Max+plusⅡ为设计者提供完善的检查方法设计仿真和定时分析,其目的是检验电路的逻辑功能是否正确,同时测试目标器件在最差情况下的时延,这一查错过程对于检验组合逻辑电路的竞争冒险和时序逻辑电路的时序、时延等至关重要。

1.4 器件编程

当电路设计、校验之后,Max+plusⅡ的Program-mer将编译器所生成的编译文件下载到具体的CPLD器件中,即实现目标器件的物理编程。

2 以计数器为例介绍具体的设计方法

计数器是非常常用的时序逻辑电路。计数器类型有多种,实现计数器的方法也有很多。可以买到大部分类型的中规模集成的计数器直接使用,也可以用触发器搭建符合要求的计数器。但是采用以上方法实现的计数器灵活性不够,不能随时进行修改,通用性差。这里介绍基于可编程逻辑器件的实现方法。

2.1 设计输入

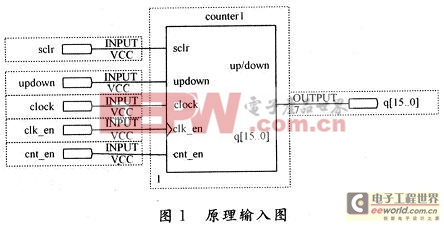

采用原理-图输入的思维方式比较适合一直采用传统设计方法人的使用。原理图输入如图1所示。

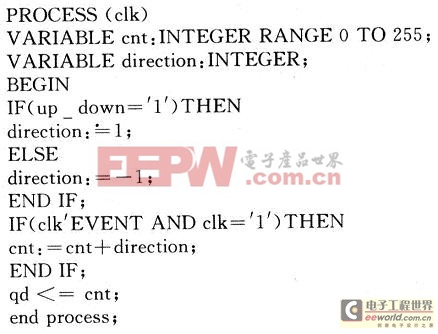

采用硬件描述语言输入的方法对于没有传统设计方法经验的人更容易入门,修改起来也更方便。给出了一个可逆计数器的实现实例,程序的核心部分如下:

评论