四大FPGA供应商专家谈FPGA设计诀窍

他们将就一系列大家非常关心的关键设计问题发表他们的独到见解,包括:什么是目前FPGA应用工程师面对的最主要设计问题?如何解决?当开始一个新的FPGA设计时,你们会推荐客户采用什么样的流程?对于I/O信号分布的处理,你们有什么建议可以提供给客户?如果你的客户准备移植到另外一个FPGA、ASIC和结构化ASIC之间进行抉择?结构化ASIC或ASIC,你会建议你的客户如何做?

问:目前FPGA应用工程师面对的最主要设计问题是什么?如何解决?Actel:当用户通过TAP接口进行JTAG测试或者编程时我们发现了许多问题。与目前最先进应用的逻辑复杂度和速度相比,TAP接口和指令集是非常简单和慢速的。这导致用户想当然地认为TAP接口处的信号完整性没有问题,甚至设计中其他位置的其他信号也适当地进行了端接。虽然数据和时钟速率很慢,但是其边沿速率和其他任何信号一样快,因此必须进行适当的端接匹配。此外,我们发现很多用户在规划减小SSO/SSN问题。

Altera:功耗、性能优化、调试、接口复杂性、信号完整性和系统复杂度是FPGA开发工程师目前面临的最主要设计问题。

1. 功耗:Quartus II软件的PowerPlay功率分析和优化技术与Stratix III可编程功率技术可以帮助用户在设计过程中显著减小功耗。

2. 性能优化:关注点集中在如何实现FMAX,以及系统级性能(如通过PCI Express接口实现足够的吞吐量)。Quartus II软件提供精确时序预报的TimeQuest时序分析器允许用户定制系统需求的时序约束。

3. 调试:传统上,工程师会使用一台逻辑分析仪分析待测器件的引脚。不过,由于今天FPGA的高容量,很多元件可以集成到一个器件中,但逻辑分析仪不能检测到设计内部的信号。SignalTap II逻辑分析仪是一个系统级调试工具,它可在一个系统级可编程芯片(SoPC)上捕获和显示实时的信号行为,从而为设计师提供了观察系统设计中硬件和软件之间交互的功能。

4. 接口复杂性:为了实现更高的性能,系统使用的接口正变得更加复杂(如DDRII SDRAM接口比以前的SRAM接口要复杂)。Altera提供多种IP核,它们可帮助设计师很轻松实现所需的接口。

5. 信号完整性:Altera提供了多种模型(包括HSPICE和IBIS)以及内置片内端接,这些有助于确保信号正确地从A传输到B。

6. 系统复杂度:设计者今天面临的挑战是,尽管开发的系统复杂度越来越大,但分配的开发时间不会比先前开发较低复杂度项目的少。Altera提供简化系统通用部分设计开发的IP核、系统验证和板级布局工具,从而允许用户集中全力开发差异化性能。

Lattice:1. 满足硬件时序要求。对规格的高级别评估,并判断它是否能满足系统的要求。例如,如果系统要求是1.2Gbps I/O,但是FPGA I/O只能支持到800Mbps,那么这种FPGA将不能满足系统速度的要求。

2. FPGA设计时序收敛。进行足够的静态时序分析和时序仿真以确保HDL设计满足硬件的时序要求。拥有已经过实践验证的硬件模块,例如DDR存储器I/O接口和串行/解串器(SERDES)/PCS模块,将有助于FPGA设计师更轻松地满足时序要求和减轻对软件工具的依赖。我们低成本的 LatticeECP2/M FPGA系列和高端的LatticeSC FPGA系列可以提供这些硬件模块。

3. SERDES在系统中的实现:虽然概念上比较简单,但是硬件实现要求很多细节正确无误,如信号端接、参考时钟的生成、锁相环(PLL)的使用、背板信号完整性和位错误率的评估。Lattice提供预定义的针对不同SERDES应用的SERDES示范平台,如PCI Express和通用8/10位SERDES完整收发硬件演示平台。

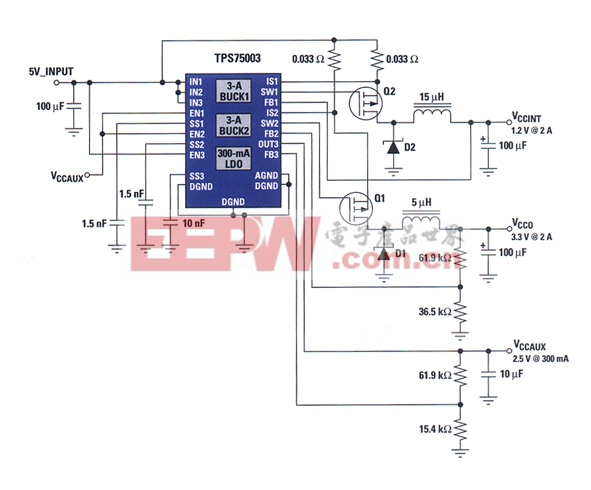

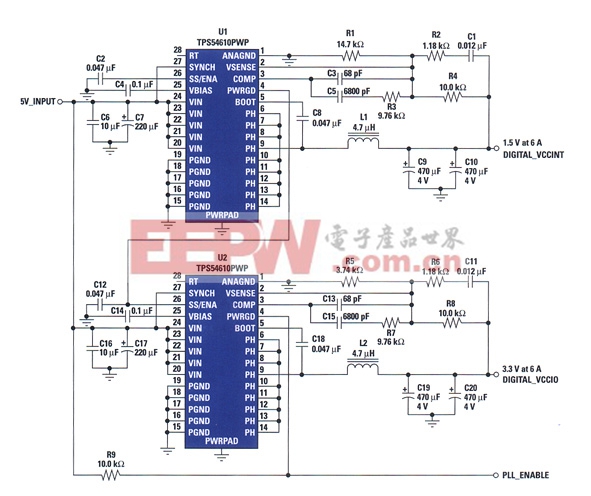

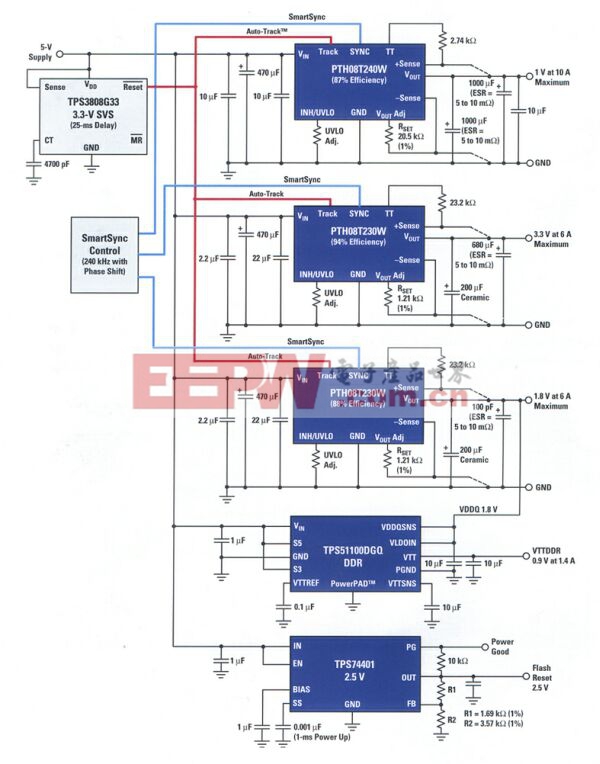

4. 功率管理:对所有FPGA电源规划功率预算。通常,2到3个FPGA电源(VCC、VCCAUX和VCCIO)是关键的。需要对器件初始上电和运行期间的不同温度进行精确估计。

5. 配置需求:这个关键步骤保证上电后FPGA将从外部引导闪存进行正确配置。

问:当用户开始一个新的FPGA设计时,你们会推荐用户采用什么样的设计流程?

Actel:逻辑设计传统上是利用硬件描述语言(如HDL)或图形化的原理图来实现的。对逻辑设计的描述越抽象,就需要更智能化的工具来自动进行推断、编译和实现这个设计。通过融合内部开发工具和业内领先的OEM和第三方工具,Actel支持所有这些不同的设计风格和工具流程。

另一个设计考虑是应该从头开始创建你的设计,还是利用现有的私有或者商业化IP。高质量IP内核可使得产品能够更快地推向市场。Actel在开发和支持内部开发的及第三方IP内核方面进行了很大的投资,我们的Libero IDE(集成设计环境)具有很多可帮助设计师高效查找和使用IP的功能。Actel也开发了已经过实践验证的系统级参考设计、HDL代码、软件驱动器、应用程序、有时甚至还包括PCB设计文件,以为设计师开展其定制工作提供一个起点。

Xilinx:客户可以使用第三方工具,如用XST、Precision或Synplify进行综合,然后使用Xilinx ISE 9.1i进行布局和布线。对于仿真,客户可以使用ModelSim、NC Sim或VCS。他们始终应该输入用于综合的时序约束。

问:关于I/O信号分配的处理,你们有什么建议可以提供给客户?应采用什么样的顺序对各种信号类型进行分配?(即从VREF开始,然后高速I/O等)

Actel:为了回答这个问题,让我们假设用户正在使用Actel基于闪存的ProASIC3E FPGA。它含有8个专用I/O块,每个块能够被分成5个微型块。这些专用I/O块共享电源电压(输入VMV、输出VCCI、GNDQ)。微型块是在一个专用I/O块内使用一个共同电压参考VREF的I/O用户定义组。只用共享电源电压和电压参考的I/O可以置于同一个专用块内。

首先,安排专用I/O块。Actel的I/O Bank Assigner工具将为该设计自动配置I/O块。如果用户想定制该I/O块的配置,他可以很容易地利用PinEditor GUI或PDC约束脚本完成这一配置。

在安排I/O块时,牢记SSO问题是很重要的。切换总线应该尽可能多地分布在整个裸片上,并且远离PLL的电源管脚及异步输入/输出管脚。在安排好I/O块之后,用户可以开始分配I/O信号。利用GUI拖拉I/O并将它放置到合适的块,或者在PDC约束文件中进行分配。差分I/O需要相邻的N/P对,因此建议先分配差分I/O。然后,分配电压参考I/O和相关的VREF管脚,它们可以从任何绑定的I/O中进行配置。最后,对所有其它单端I/O进行分配。

Altera:虽然灵活的管脚分配对FPGA很重要,但某种程度的专用化也可通过减少管脚电容改善信号的完整性和系统的性能。例如,用于高速收发(如PCI Express)的管脚不能用作通用I/O。Altera不要求按照某一顺序对管脚进行分配,但管脚分配要求匹配管脚的功能。客户可以在开始设计前使用 Quartus II软件进行一次管脚检查,从而允许同时进行板和芯片的设计。

Lattice:FPGA I/O结构比具有固定I/O管脚的标准产品复杂。FPGA需要正确的I/O布局来确保:分配的多个I/O在块内能够共存,没有冲突;它们能够以要求的I/O速度运行而没有噪声或信号完整性问题。

I/O分配应从专用I/O最先开始,如DDR2存储器接口、SERDES接口和PCI接口等。这将决定关键的管脚分配,然后再在剩余管脚上分配通用I/O管脚,如LVCMOS33、LVCMOS25和LVTTL等。

此外,要特别注意特殊的引脚,如VREF、高速CLK输入和PLL/DLL输入。用户可以指定使用哪个器件引脚,也可以让工具选择需要的引脚。在后一种情况下,用户需要对这些引脚的分配进行备注,从而使得以后的PAR运行时继续使用相同的配置。ispLEVER提供两个基本特性以支持该功能。

Design Planner工具支持用户生成符合复杂I/O块规则的I/O布局约束。从封装的角度来看,用户可以直观地过滤具有某一特定性能的管脚(如主时钟输入引脚和差分信号引脚对),然后将设计信号分配到过滤后的引脚上。I/O Assistant Flow允许实际的PAR引擎和用户提供的I/O布局约束仅用在该设计的I/O环上,以生成一个合理的I/O布局。这可以在设计过程的较早阶段完成,从而实现早期板级设计。

Xilinx:FPGA I/O分配常常必须调整多次才能成功,因为它有时候会和以下约束发生冲突:1. PCB约束,如冗余通道、板空间拥塞、信号完整性效应(长度匹配、最大衰减、最大过孔等);2. FPGA架构约束(I/O规则、SO、时钟规则等);3. 客户设计约束(时序、器件内逻辑源点/终点的位置等)。

每个FPGA架构/客户设计都有其独特的约束环境。提出通用的规则不是件容易的事。通常,你先要确定约束最强的FPGA管脚。管脚分配的一个典型顺序可以是:1. 全局/局部时钟输入管脚和FPGA配置管脚;2. MGT(SERDES)、高速单端存储器/CPU接口、差分信号、由于特殊的客户设计(DCI参考电压和输入参考电压)而不能用作用户I/O的多功能管脚;3. 其它用于内部定时或PCB布局的需要在FPGA上具有邻近管脚位置的管脚组(总线);4. 最后,慢信号(如复位信号)。

可以使用多种方法进行I/O分配:ISE(PACE、Floorplan Editor)、第三方供应商(Mentor Graphics I/O Designer)、PlanAhead,或甚至Excel电子数据表。

问:在处理不兼容的I/O标准、不同电压参考和其他有关块及区域兼容性问题时,你们建议用户采用什么方法去解决?

Altera:我们的目标是使客户尽可能方便地处理这个问题。为了达到这个目的,我们的FPGA管脚能够支持工作在不同电压的多个I/O标准(例如,大多数器件上采用 2.5V供电的管脚仍然可以接收3.3V的输入)。此外,大多数管脚可以支持热插拔,这使得我们的FPGA能够作为插入一个带电系统的板上接口。即便当系统规范没有热插拔要求时,这一特性仍然很重要。采用多个供电电压的系统可能采用不同的上电顺序,因此Altera设计的FPGA支持系统按照任意顺序对内核、各种I/O块以及信号驱动器上电。Altera FPGA的这一特性使得设计师可以轻松地将它与其它需要按照一定顺序上电的芯片设计在一起,或至少减少了一个需要担心的事情。

问:如果你的客户准备移植到另外一个FPGA、结构化ASIC或ASIC,你会建议你的客户如何做?

Actel: Actel已经为多代基于闪存的FPGA器件(从ProASIC到ProASIC Plus到ProASIC3)提供了独一无二的管脚兼容移植功能。一般来说,只有当客户必须采用更新的技术进行设计时才会考虑移植。此时,设计师可以先采用适合启动设计/开发的较低风险成熟器件(或技术)。这也为客户提供了一条到更低成本解决方案的简单且预先确定好的移植路径,该解决方案只需要最少的系统和设计修改(通常只需要重新综合、布局和重新进行时序设计)就可进行批量生产。这一成本移植策略允许客户避免移植到ASIC/标准单元时所冒的高风险和高成本。

Altera:如果从一个FPGA转移到另一个相同系列的FPGA,我们提供管脚移植。如果从一个系列转移到另外一个系列,通常需要开发出一块衍生板,因为管脚排列是不同的。通过采用MegaFunctions(如lpm_mult),设计师可以确保最大限度地复制专用模块(如DSP 模块)的性能。

我们推荐使用HardCopy II结构化ASIC。在Quartus II软件中选择HardCopy选项,可以很轻松地移植到结构化ASIC。例如,通过确保所使用的管脚从FPGA映射到HardCopy II器件。另外一个关键点是,HardCopy II器件上的模块(如存储器、LVDS接口或PLL等)与FPGA是相同的,这可使得移植变得非常轻松。

将逻辑从FPGA移植到ASIC是相对比较简单的。不过,把其它元件从FPGA移植到ASIC中就相对比较困难,因为PLL或存储器模块可能工作起来不太一样。由于我们不知道ASIC模块是怎样工作的,因此在此方面提出建议已超出了我们的能力范围。

Xilinx:考虑到结构化ASIC或ASIC转换时必须在再验证和测试向量生成方面花费很长的时间,因此降低FPGA设计成本的最好替代方法是使用Xilinx的 EasyPath解决方案。它利用同样的FPGA芯片,但是使用不同的测试方法来创建一个提高良率和降低成本的面向设计的测试方法学。在这一移植过程中,没有必要做特殊准备或者避免使用任何FPGA功能,因为这些功能都可以在EasyPath实现中获得。

对于采用更大容量Xilinx FPGA做ASIC原型设计的用户而言,简化这一转换过程的常用方法是将与器件相关的功能(如存储器)保留在它们各自独特的分层模块中。这样,它们以后就可以被具有相同功能的ASIC版本所取代。当然,这个方法的缺点是用户放弃了充分使用嵌入式硬模块的能力(如复杂RAM块、DSP/乘法器模块、数字时钟管理器、以太网MAC和PCI Express端点模块),除非在ASIC中创建有相似的定制功能。

问:当将FPGA器件整合到PCB上时,关于SSO/SSN问题你们会给客户什么建议?

Actel:由于客户需要更全面地了解和解释SSN特性,因此我们非常重视这个问题。通过测试、描述和与客户一起工作的经验,我们发现造成SSN问题的主要因素是封装的选择、I/O布局和输出时序。在PCB上进行适当的去耦、端接和布局是非常重要的。不过,最好是在问题的源头完全避免SSN。

QFP封装由于其封装引脚和邦定走线带来的电感越来越大,实际上不如市面上各种BGA封装。因此,我们针对QFP封装的SSN建议更为严厉。为了防止QFP封装带来的SSN问题,建议避免在裸片上将较大的SSO组安排在相近位置。不过,如果这是不可避免的,用户应该确保灵敏的“安静”I/O位于VCCI或者GND附近。或者,用户可以利用相对不活跃的输出将SSO总线与灵敏的I/O隔开。如果I/O布局已经被锁定而且客户无法满足我们的建议,他们可以在总线内创建小的时序组。这里,I/O以大于1ns的间序交错排列。如果做到了这点,总线输出将不再同步切换。

问:你们建议如何处理全局和本地/区域时钟?

Actel:我们基于闪存的ProASIC3E FPGA系列提供18个专用全局时钟,这意味着大部分设计不会受到时钟的限制。对于区域时钟,这些全局时钟中的12个被局部化到该器件的四分之一区域。那么,FPGA设计师应该如何处理跨越用户设计区域和IP模块的公共全局时钟呢?通常,客户必须在更低一级的模块中例示一个全局时钟,将其带到一个输出端口,然后再分发到设计的其他部分。借助Actel的Libero IDE 7.3,客户可以获得基于模块的设计方法,并补救时钟分配问题,客户只需要例示一个全局时钟占位符(CLKINT)。然后,全局缓存可以在设计的顶层中实现。这使得时钟分配和分发更加直观,并简化了在多个设计中模块的重利用。

问:在IP模块集成方面,你看到了哪些问题?你能给工程师什么购买IP的建议?

Actel:IP产生了边界,限制了自动化工具能够优化的东西。另一方面,让IP边界可辨识对调试是非常有帮助的。对于一个复杂度越来越大的设计流程,IP模块是一个用来限制改变的自然边界。

现代FPGA除了逻辑门之外还有很多固定资源。通常多个IP模块共享这些资源。很少FPGA供应商的工具可以最优化处理这一资源共享问题,但Actel Libero在设计时就考虑到了这一问题。其中一个例子是在Actel Fusion混合信号FPGA上多个IP模块间时钟和内存资源的高效共享。

在选择IP时,应该检查其功能和配置以确定它是否能满足你的设计要求。你应该观察该IP是否是针对你的目标FPGA而设计的,以及其尺寸和性能是否高效。好的IP还配有完整的测试向量和高质量的文档。最后,在你答应使用前检测一下该IP核的来历和供应商。

Xilinx:在集成IP模块时的确有一些小挑战,这主要是由于IP供应商实际交付的IP模块与那些可交付使用的IP模块之间存在细微差别而引起的。集成IP模块的一个较大的挑战是确保客户设计仍然能够满足时序和资源要求。我们提供给购买IP的工程师的最重要建议是,确定IP供应商是如何检测和验证该IP的,也就是确认质量和易用性。

问:什么样的时序问题正在引起最大的麻烦?你们建议如何处理?

Actel:最小延时和保持时间分析似乎经常被忽视。外部保持时间和跨时钟域路径(而不是与时钟歪斜时序相对的简单的寄存器到寄存器数据路径)会引起大部分导致硬件失败的时序问题。首先,用户应该进行时序仿真和静态时序分析。仿真提供了功能验证,静态分析提供最好的时序覆盖。为了进行精确的外部保持时间计算,时序应该在最好的工作条件下(包括最高电压、最低温度和最快速度)从发送端、接收端和PCB提取。Actel SmartTime时序分析仪允许用户输入外部输入和输出延时,然后进行所有这些计算。

我们看到的与跨时钟域路径相关的主要问题是时序验证不够充分。当设计中存在跨时钟域路径时,静态时序分析是非常关键的。但是,一些静态时序分析工具不能自动进行这一分析。为了进行这一分析,用户必须定义每个时钟的频率,在最好和最坏的工作条件下进行分析,以及对于每一种工作条件,估计不同时钟之间最大和最小时序偏移。

Lattice:下列三大时序问题正在引起最大的麻烦:高速时钟域转移、竞争条件和保持时间不足。随着工作频率提高,时序窗口正变得越来越小。仔细的时序分析和强大的软件工具可以帮助工程师确定问题区域并解决这个问题。

由于Lattice FPGA交换逻辑的极高性能,保持时间不足的可能性已经开始明显增加。保持时间不足通常发生在时钟偏移大于数据时延的时候。即使Lattice FPGA的主时钟走线具有非常小的偏移,但由于数据路由太快以致于这些不足情况是可能发生的。Lattice ispLEVER设计工具提供自动校正保持时间不足的功能。

评论