基于FPGA的LED点阵显示字符设计

采用现场可编程逻辑器件( FPGA) 作为控制器, 选择合适的器件, 利用器件丰富的I/O 口、内部逻辑和连线资源, 采用自上而下的模块化设计方法, 可以方便地设计整个显示系统。

电子设计自动化(EDA)技术是基于可编程器件( PLD) 的数字电子系统设计, 它是进行系统芯片集成的新设计方法, 也正在快速地取代基于PCB 板的传统设计方式。在EDA工具软件MAX+PLUSⅡ的支持下, 本设计通过了编译、适配和软件仿真验证。最后用载入真实实验系统的硬件实验证明了它的正确性。

1 系统结构及其原理

本设计结合上海航虹高科技公司生产的EDA实验箱, 需要显示的16 个字符的字模已存放在EPROM 的8000H~807FH, 采用单个8×8LED 点阵(WTD3088)显示字符, 显示控制由现场可编程门阵列( FPGA) EPF10K20TC144- 4 来实现。系统原理是FPGA首先产生点阵字模地址, 并从存储器读出数据存放在16 位寄存器中, 然后输出到LED 点阵的列, 同时对点阵列循环扫描以动态显示数据, 当需要显示数据字模的列和被选中的列能够协调配合起来, 就可以正确显示字符。

2 FPGA设计及其原理

为在8×8LED 发光二极管点阵上显示字符, 首先要把字符表示成为8×8 像素点( AD0~AD7) , 分别为按列抽取依序排列的字符像素信息, 均具有8 位字长。然后依次对多字符抽取像素信息, 并按序排队存放于EPROM 之中, 便可得到一个待显示数据序列。进一步通过寻址的方法来控制该数据序列的释放过程, 就可实现在8×8LED发光二极管点阵上滚动显示多个字符信息的目的。page 控制字符显示的滚动速度, 它的取值范围应为0~N, col 决定LED 点阵的列开关的扫描速度,它的取值范围应为0~7.某一时刻能在显示数据序列中定位待显示数据的地址指针可用下式计算: addr=page+col应当注意的是, 扫描速度应远大于滚动速度, 本设计中使用的扫描时钟是1KHz, 字符的滚动速度是1 秒/ 个。调节字符信息的滚动速度;改变col 的重复扫描周期, 可改善在LED 点阵上显示完整字符信息的稳定性。

另外还需指出, 由于addr 的运算要靠硬件实现, 故地址指针addr的模应取为N, 而且为实现全部字符信息滚过LED 点阵, 必须在数据N前补充8 个空数据字节。根据其工作原理, 设计了描述FPGA内核硬件功能的VHDL 语言程序。本设计结合了EDA实验箱和ALTERA公司的MAX+PLUSⅡ研发工具, 并采取了行为的描述方式。

VHDL程序如下:

libraryieee;

use ieee.s td_logic_1164.all;

use ieee.s td_logic_arith.all;

use ieee.s td_logic_uns igned.all;

entityledis

port (clk1,clk2,reset: ins td_logic;

led_s: out s td_logic_vector(2downto0);

memcs,rd,wr,cs0809,sELmled:out s td_logic;

a: out s td_logic_vector(15downto0);

ad: out s td_logic_vector(7downto0));

end;

architecture led_archofledis

s ignalcol:integerrange 0to7;

s ignalpage :integerrange 0to15;

s ignaloe:s td_logic;

begin

proces s(clk2,reset,col)

begin

ifreset=''1'' then

col=0;

els if(clk2''event andclk2=''1'')then

col=col+1;

endif;

led_s = conv_s td_logic_vector(col,3);

a(2downto0)=conv_s td_logic_vector(col,3);

endproces s;

proces s(clk1,page)

begin

if(clk1''event andclk1=''1'')then

page=page+1;

endif;

a(6downto3)=conv_s td_logic_vector(page,4);

endproces s;

ad= "ZZZZZZZZ";oe = ''0'';

memcs = ''0'';rd= ''0'';

wr= ''1'';selmled=''1'';cs0809= ''1'';

a(15downto7)="100000000";

endled_arch;

3 实验验证

通过使用EDA工具软件MAX+PLUSⅡ中的仿真器, 对通过编译的字符滚动显示器的VHDL设计进行了模拟仿真验证, 证明FPGA的内核硬件工作良好。此外, 将VHDL 程序下载到由上海航虹高科技公司生产的EDA实验箱上后, 能正确显示存放于EPROM 中的字符。从而说明了在硬件系统中字符滚动和显示扫描情况也均正常, 验证了设计的正确性。

4 结束语

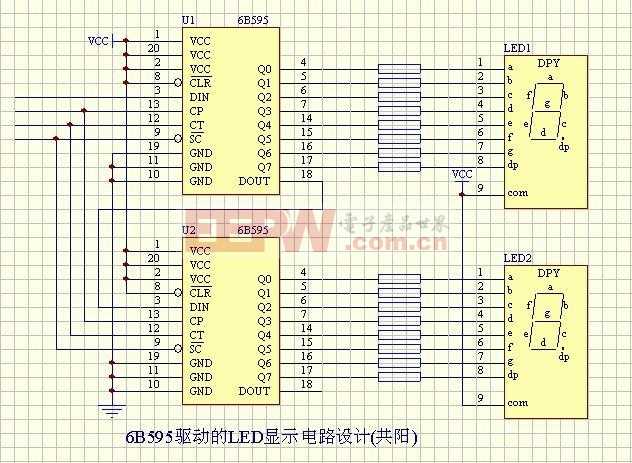

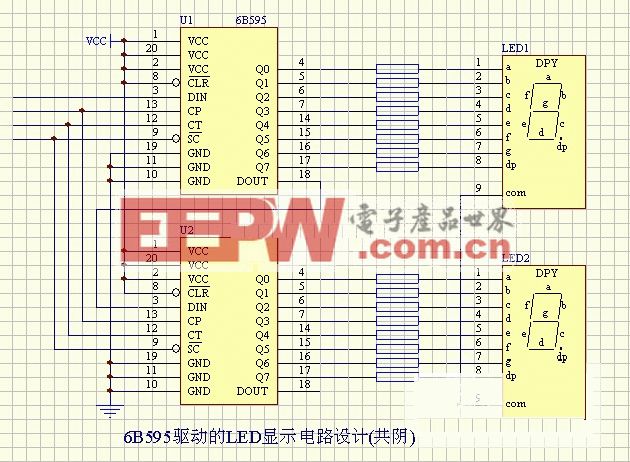

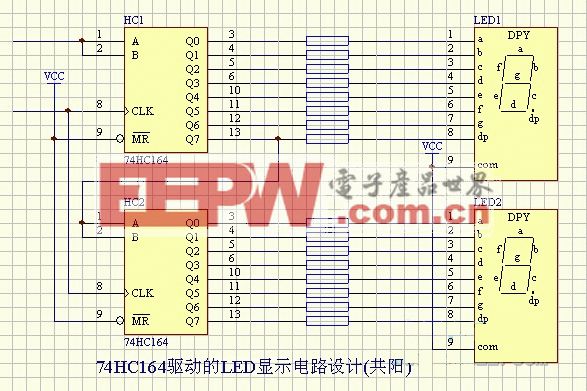

本设计为显示单个字符系统, 若要同时显示多个字符时, 可以加入多个LED 点阵即可。同时采用外部译码器时, 可以控制的字符数将大大增加, 但须注意时钟CLK的频率需要提高, 以眼睛看到整个字符的不闪烁为基准。此外, 由于FPGA的驱动能力有限, 当点阵LED 显示亮度不够时, 需要为LED 点阵添加驱动电路( 如高压大电流达林顿阵列集成电路) 以提高的LED显示亮度。

评论