I2C串行总线在单片机8031应用系统中的设计与实现

1 I2C总线概述

I2C (inter IC bus)总线是由Philips公司提出的串行通信接口规范,常见的中文译名有“集成电路间总线”或“内部集成电路总线”。它使用两条线:串行数据线(SDA)和串行时钟线(SCL),使连接到该总线上可访问的器件之间传送信息,属于多主控制总线。总线上的每个器件均可设置唯一的地址,从而可实现器件的有效访问。自Philips公司推出I2C总线后,Philips公司及其他公司纷纷相继推出了许多I2C总线产品,如各种微处理器、存储器(PCF8571/8570,128/256 字节)、A/D(PCF8591)、D/A(TDA8442/8444)转换器、E2PROM及各种I2C总线接口电路(PCF8584)等。由于I2C总线的使用可以简化电路,省掉了很多常规电路中的接口器件,提高产品的可靠性,在许多领域尤其在目前使用的IC卡获得了广泛的应用,国际标准ISO7816-2规定了IC卡与读写设备信息传输是基于I2C总线传输协议的。不仅如此,I2C总线在家电方面也有较广泛的应用,如国产长虹NC-3机芯彩电,东芝火箭炮等。尽管Philips公司推出带有I2C 总线接口的80C31系列单片机,如:8XC528、8XC552、8XC562、8XC751等,但在单片机组成的智能化仪表和测控系统中,乃有相当比例数量使用的是MCS51、AT89C5X系列单片机,如8031、8751、AT89C51、AT89C52等,它们不具有I2C串行总线接口。本文将结合笔者在开发智能化产品用到的E2PROM,介绍在不具有I2C串行总线接口的单片机8031应用系统中实现I2C总线接口的方法和软件设计。

2 I2C总线的组成及I2C总线性能

2.1 I2C总线的特点

由于I2C总线仅用二条线来传达信息,因而具有独特的优点:

① 可最大限度地简化结构;可实现电路系统的模块化、标准化设计。

② 标准I2C总线模块的组合开发方式大大地缩短了新产品的开发周期。

③ I2C总线系统具有很大的灵活性;I2C总线各节点具有独立的电气特性。

④ I2C总线系统可方便地对某一节点电路故障进行诊断与跟踪,有很好的可维护性。

2.2 I2C总线的组成

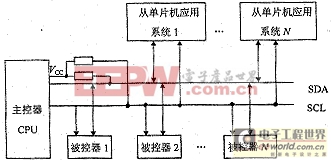

I2C总线是芯片间串行传输总线,与SPI,MICROWIRE/PLUS接口不同,它以一根串行数据线和一根串行时钟线组成,如图1所示,它是全双工双向数据传输线,核心是主控CPU,被控器的SDA,SCL要相应地接到I2C总线的SDA,SCL上,可以方便地构成多机系统和外围器件扩展系统。I2C总线采用了器件地址的硬件设置方法,从而使硬件系统具有简单而灵活的扩展方法。按照I2C总线的规定,其SDA、SCL各要通过上拉电阻接到电源VCC上。

图1 I2C总线的组成

2.3 I2C总线协议

任何总线的推出及应用都有其特有的规定,其总线时序图如图2所示。

图2 I2C总线时序图

I2C总线一般须满足如下协议:

① 只有当总线不忙时,数据传送才能开始;

② 数据传送期间,无论何时时钟线为高,数据线必须保持稳定。当时钟线为高时,数据线的变化将认为是传送的开始或停止;

③ 当时钟线为高时,数据线由高到低的变化决定开始条件;

④ 当时钟线为高时,数据线由低到高的变化决定停止条件;

⑤ 在开始条件后,SCL低电平期间,SDA允许变化,每位数据需一个时钟脉冲,当SCL为高时,SDA必须稳定;

⑥ 主控器在应答时钟脉冲高电平期间释放SDA线高,转由接收器控制。受控器在应答时钟脉冲高电平期间必须拉低SDA线,以使之为稳定的低电平作为有效应答;

⑦ 总线不忙时,数据线和时钟线保持为高电平。

2.4 I2C总线上的数据传输方式

图3为I2C 总线数据传输格式示意图,第一部分为数据传输起始信号,即由此开始进行数据传送;第二部分为受控IC的地址,用来选择向哪一个受控IC传送数据;第三部分为读/写位,它指示出受控IC的工作方式;第四部分为应答信号,它是被CPU选中的受控IC向CPU传回的确认信号;第五部分为传送的数据;第六部分为停止位。在I2C总线上挂接的所有被控IC都要有一个自己的地址,CPU在发送数据时,I2C总线上的所有被控IC都会将CPU发出位于起始信号后面的受控电路地址与自己的地址相比较,如果两者相同,则该被控IC认为自己被CPU选中,然后按照读/写位规定的工作方式接收或发送数据。

| 起始 | 被控IC地址 | 读/写控制位 | 应答位 | 数据 | 停止 |

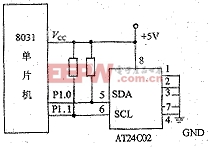

图3 I2C总线数据传输格式 3 I2C总线在单片机8031中的实现 因为8031单片机不带有I2C总线硬件接口,只能靠编写软件来模拟I2C总线时序。这里以单片机应用系统中较为常见的E2PROM中AT24C02为例,给出了在8031上利用I/O线实现I2C串行总线的方法和软件设计。根据I2C总线时序图和I2C总线的数据传输规范,给出详细的AT24C02起始、停止、发送和接收R7个字节的驱动程序清单。

图4 I2C总线接口原理图 ORG ×××× ;程序开始地址。 4 结束语 本文给出了用8031汇编语言模拟I2C总线的时序的起始、停止及主控器向I2C总线的发送和接收R7字节的程序,读者也可根据I2C总线的操作时序在ATMEL89系列、68HC05系列等单片机及其外设接口如8255、8155或74LS377上实现I2C总线的操作,具有一定的通用性,且易于嵌入移植。 参考文献 |

评论