基于DSP的列车应变力测试系统设计方案

摘 要:本文介绍了基于TMS320VC33 DSP芯片的应变力测试系统的设计,给出了结构原理框图,并围绕DSP设计了测试系统的中断、复位子系统、存储子系统和通信子系统。同时还对测试系统进行了信号完整性分析。

关键词:测试系统;DSP;应变力;信号完整性

车轮与轨道间的作用力是评价车辆运行品质的重要因素,能否准确及时地获取轮轨间的作用力直接影响着车辆脱轨系数等参数的计算。应变力测试系统是设计列车运行状态地面安全监测平台的关键环节,本文用DSP芯片开发的测试系统正是针对这一需要。

测试系统硬件设计

系统整体结构

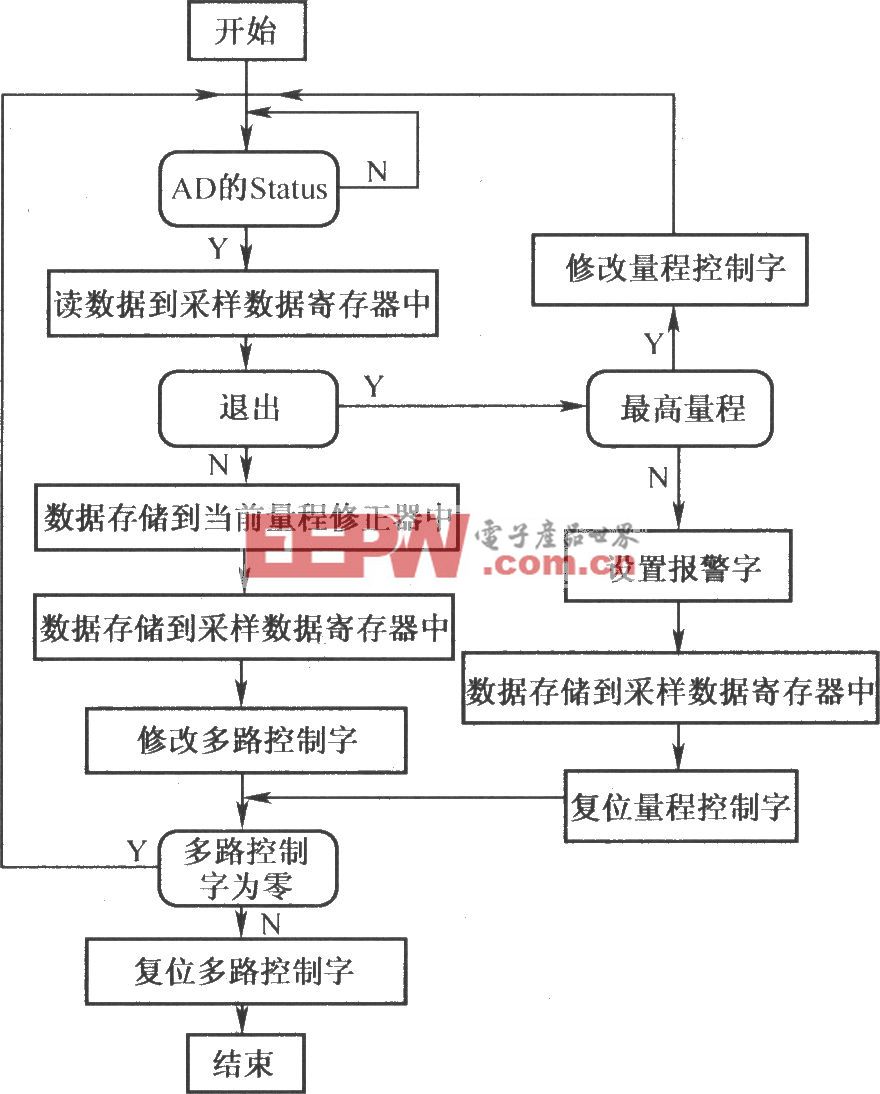

测试系统以高速、高精度的DSP为核心,构成了包括模拟信号预处理、A/D转换、D/A转换等环节的实时信号测试处理系统。其原理框图如图1所示。

应变传感器输出的模拟信号,经RC滤波网络初步滤去信号中的高频成分,然后经A/D转换后,变为数字信号。RC滤波网络、A/D转换构成了测试系统的前向通道。

中央处理单元以TMS320VC33为主体,该DSP是一款高精度、大容量、宽功率范围的浮点处理器,具有高度的并行化,以及DMA协处理器通道。同时,本设计还在系统中设置了1个64K×32位的数据存储器和512K×8位的程序存储器,与DSP共同构成了整个系统的存储系统。

可编程逻辑(CPLD)是测试系统的硬件控制核心。其主要任务是控制A/D转换、产生存储系统的片选信号。

中断、复位子系统不仅起到系统复位的作用,同时还用来确定系统应用程序的位置。DSP根据此系统来装载应用程序并运行。

中断、复位子系统设计

在本测试系统中,DSP需要单独地组成一个系统,因而把TMS320VC33设置为微计算机模式,此时TMS320VC33具有程序引导功能。当系统上电或复位时,TMS320VC33监测4个中断管脚的状态,根据BootLoader程序定位表来确定用户程序的地址,然后运行自身的BootLoader程序把用户程序下载到指定地址空间。实现系统BootLoader的复位电路如图2所示。

时钟电路的设计

TMS320VC33的时钟,既可由外部提供,也可由板上的振荡器来提供,但外部时钟的精确度高、稳定性好、使用方便,因而本设计中使用了12MHz的外部时钟CLKMD0 CLKMD1=11的时钟模式,经内部5倍频后,产生60MHz 的系统时钟。

总线驱动

由于DSP的地址总线和数据总线的驱动能力有限,当负载较大时,需要用总线驱动对其负载能力进行扩展,以保证系统能稳定工作。本设计选用了TI公司的宽总线16位双向总线驱动器SN74LVTH16245,它具有很高的集成度和性能。

评论