VME总线接口芯片SCV64原理及应用

关键词:VME总线;总线接口;SCV64

1 引言

VME总线即Versa Module Eurocard Bus,自1981年由Motorola公司同Signetics/Philips、Mostek以及Thompson CSF等公司推出之后,几乎在所有的工业领域中都得到了广泛的应用。它具有良好的物理特性、严格的技术规范和与32位微处理器方便灵活的接口,用户可根据VME总线标准按需求自行开发应用系统。实际应用中,系统往往不仅需要以从者(Slave)接受来自VME总线的访问,还需要以主控者(Master)访问VME总线。因此,设计时就必须考虑到系统与VME总线的接口问题。为了缩短设计周期,设计者一般都选用专业公司的现成ASIC。早期开发的VME总线系统多采用Cypress公司的VIC068A或VIC64作为桥接控制器件。但是,VlCx系列接口器件的局部总线是为Motorola公司的68K系列处理器设计的,对于与68K处理器总线不兼容的其他类型处理器(如x86系列、PowerPC系列等)来说,使用VICx系列器件,需要的外部转换逻辑较为复杂。而且,VICx系列器件自身只提供8位地址和数据通道,要构成8位以上的总线接口,则需要锁存器件或Cypress公司其他接口电路的配合。比如要构成32位VME总线接口,就需要一片VIC64和3片CY7C964相配合组成总线接口。这样,逻辑设计复杂,对PCB板空间资源占用也较大。所以,VME总线的开发者不推荐在未来的系统设计中以VICx系列器件作为接口解决方案目。Tundra公司的SCV64是一种通用的单芯片总线桥控制器,片上具有高速的VME64数据通道、VME总线控制器、中断控制器、DMA控制器等功能模块,支持MC68K系列、x86系列以及TMS320CxO系列等多种处理器。相比VICx系列,该器件集成度高,外部一般仅需地址译码逻辑即可,因此,可以方便地用于开发VME总线接口电路。

2 SCV64功能原理及其特性

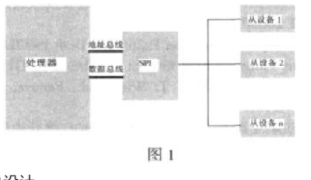

SCV64是单片VME总线至本地处理器的互连器件,集成了VME总线系统控制器、中断控制器、DMA控制器等功能,具有众多功能模式供用户选择。用户可以根据自己的需求来“定制”不同应用环境下的VME总线接口。其功能框图如图1所示。

由图l可知,SCV64的功能块可分为本地总线接口、数据通路以及VME总线接口三部分。其设计的最大独特性是数据通路采用后置写FIFO结构。由于使用了接收FIFO以及发送FIFO在本地总线和VME总线之间传输数据,即用非耦合(Decouple)方式传输,可弥补两个总线性能的差异,从而使得每个总线以各自最佳速率运行,互不牵制。

VME总线系统必须有且只能有一个总线系统控制器,必须位于背板的第1槽。SCV64具有插槽1自动识别的能力,可自动使能总线系统控制器功能,完成VME总线仲裁、菊花链驱动等功能。由于系统加电后,除第l槽外(第l槽的BG3IN*信号不会与任何信号连接),其余插槽的BG3IN*信号均被前边插槽所传递下来的BG30UT*菊花链信号置高,因此,在复位信号释放后的500 ns内,若SCV64检测到BG3IN*为低,即说明本板所处插槽为第1槽,须启用总线系统控制器功能;若检测到BG3IN+为高,则此功能被禁止。SCV64的这种设计,可摆脱原来易出错的人工硬跳线方法。

与VICx系列器件相比,SCV64另外一个优势是其内部有一个本地总线仲裁器(可选)和VME总线地址译码器,这样就省去了外部逻辑的设计,方便了用户。另外,它还提供一种总线隔离(Bus lsola-tion-BI)工作模式,通过若干信号进行配置。进入BI模式后,SCV64会将本地系统与VME总线隔离,退出BI模式则又重新恢复连接。BI模式可用于热备份系统、系统诊断或例行维护,也可在本地板失效后将其隔离而不致影响其他插槽的设备。

3 SCV64的数据传输

3.1 主周期传输

SCV64的耦合模式传输过程与VICx系列器件基本相同。在非耦合模式下,当本地处理器需要发起一次VME总线的主传输周期时,先发出有效地址和数据等信息,地址译码逻辑据此驱动SCV64的VMEOUT和KAS信号,通知SCV64,CPU欲访问VME总线。检测到KDS有效后,SCV64将本地总线上的数据锁存到发送FIF0(TXFIFO),记录此周期相关信息并使其进入TXFIFO的内部队列,随后驱动KDSACKx信号,通知本地处理器结束本地周期,释放本地总线。此过程时序如图2所示。

回复本地处理器后,SCV64根据相应寄存器的配置驱动某级BRi*信号请求VME总线。经系统控制器仲裁,若收到了同级BGilN*菊花链信号,SCV64就将其截止,不再往下传递,同时驱动BB-SY*信号,占用VME总线,依据VME总线时序规范将TXFIFO队列中的内容发出。

TXFIFO的深度为15级,字长72位。其中的每条72位记录(72-bit entry)由控制、地址、数据三部分组成。这三部分的信息分别读自SCV64的TX-FIFO控制寄存器TXCTL(8位有效位)、地址寄存器TXADDR(32位)和数据寄存器TXDATA(32位)。若TXFIFO已满,则不会再接受写周期,直到某条记录发往VME总线后让出了可用空间。

3.2 从周期传输

SCV64的VMEBAR寄存器中存储的是其VME从地址映射范围信息。其内部地址译码器“监听”高5位VME地址VADDR[3l-27],若落入映射范围,则SCV64接受此次从传输。在非耦合模式下,SCV64将地址、数据以及控制信息锁存入71位字长的接收FIFO-RXFIFO,之后驱动DTACK*,回复VME总线主设备,通知其传输结束。

随后,SCV64请求本地总线,取得本地总线所有权后,通过单周期或突发(burst)模式将RXFIFO中的一条记录发往其指向的本地地址。SCV64自带的本地总线仲裁器具有本地总线仲裁能力,但是此仲裁器的仲裁机制较为固定,用户可通过在复位信号释放时拉低KBGACK信号来“回避”此功能,用户可自行设计外部仲裁逻辑。SCV64生成本地周期的时序如图3所示。

3.3 SCV64寄存器访问

在系统初始化、读取状态信息或者写控制位时,需要访问SCV64的内部寄存器。SCV64具有45个32位寄存器(通过本地低8位地址编码),既可通过本地总线访问,也可通过VME总线访问。

本地CPU对SCV64寄存器的访问过程与其需要访问VME总线时对SCV64的操作基本类似,只不过本地地址译码逻辑驱动的是SCV64的片选信号SCV64SEI,而不是VME总线请求信号VMEOUT。当SCV64寄存器被来自VME总线的访问时,SCV64将其自身映射为本地设备,请求本地总线,生成一次本地周期。此时,需要本地地址译码逻辑驱动SCV64EI信号,将该本地周期指向SCV64寄存器。有关SCV64寄存器访问的详细内容,可参照其用户使用手册。

4 SCV64的中断处理

根据VINT寄存器的设置,SCV64的VME总线中断请求器(VME Bus Interrupter)可生成7级VME总线中断(IRQl*-IRQ7*)的任一级。检测到对应本级中断的IACK周期时,SCV64将在数据线VDA-TA07-VDATA00上提供8位的中断向量,同时驱动DTACK*信号回复系统控制器。

本地总线中断请求器(Local Bus Interrupter)通过KIPL2-KIPL0信号向CPU生成中断,编码7级本地CPU中断。中断源撤销中断的同时SCV64将此组信号置为无效(111)。处理过程中若发生更高级别的中断,KIPL2-KIPL0立即改变为新中断级别的编码。

中断处理器模块将中断源分为3组:第七级中断(L7IMEM、L7INMI、L7LACF)、一般本地中断、VME总线中断。其中第七级中断默认为最高级别的CPU中断,其次是系统错误中断(如SYSFAIL+)和一般本地中断(LIRQ5-0),而VME总线中断(IRQ7*-IRQ1*)优先级最低。中断源的中断请求通过中断处理器转发给CPU,CPU响应中断后,要向SCV64发出中断确认周期。此周期可通过外部译码逻辑译码,也可通过SCV64内部译码。这两种情况都会驱动SCV64的KIACK信号,SCV64就对中断源发出一个IACK周期,同时驱动KAVEC,通知CPU中断确认结束。

5 PowerPC与VME总线桥接实现

PowerPC系列微处理器是业界公认的高性能、低功耗32位RISC处理器,可以进行高性能计算和图像处理,被美国国家航空和宇宙航行局(NASA)列为航天设备的标准处理器,而航天电子设备应用最广泛的总线就是VME总线。国内该方面的研究紧随其后,已经有了PowerPC 603e的国产化产品,但是对其与VME总线的接口问题研究还不多。事实上,以603e为例,要将其通过SCV64接入VME系统,主要涉及两个问题:一是电平转换的问题,CPU为3.3 V而接口器件为5 V;二是本地接口控制信号功能转换的问题,CPU总线是60x总线,而SCV64的本地接口采用680x0协议,因此需要外部逻辑实现功能转换。

第一个问题可通过固定电平变换模块来解决。第二个问题则归结为SCV64控制功能的实现,主要包括复位功能的实现、系统初始化、映射译码功能、主从传输的实现、中断功能实现、寄存器访问、仲裁功能、块(DMA)传输实现等,可借助FPGA或PLD器件来完成。

选用Altera公司的EPM9560ARI208-10型CPLD实现接口转换和控制逻辑,如图4所示。复位控制模块接收来自电源监测电路(MAX706)的上电复位或SCV64发出的复位信号,控制SCV64以及其他转换逻辑的复位,并完成PowerPC的工作模式选择;本地仲裁模块用于解决CPU与SCV64之间的本地总线竞争;地址译码模块主要是根据CPU的有效地址,发送适当的器件或外设的选通信号;总线周期控制逻辑完成同步总线协议与异步协议的时序间匹配,向CPU(主周期)或SCV64(从周期)以及其他控制逻辑发出相应的总线周期终止信号(或插入等待周期),以开始下一周期或者做出相应的操作处理错误;PowerPC仅有一个外部中断输入信号INT接受外部中断,因此需要中断控制逻辑来接受和转发中断矢量,对中断信号进行适配。

上述设计的核心部分为仲裁模块和周期控制模块,这两个模块可用状态机实现,仲裁模块的状态机示意图如图5所示,依据状态图,可以很容易地写出VHDL代码。

SCV64接往VME总线的信号中有三组需要通过外部缓冲器件驱动后才能接入VME总线,分别由VADDROUT、VDATAOUT和VSTRBOUT信号控制缓冲器件的方向:A31-A00和VLWORD分别为地址和字长信号;VDATA31-VDATA00为32位数据信号;VAS,VDS1,VDS0,VWR以及VAM5-VAM0分别为VME总线地址、数据选通信号、读/写信号和地址修改码。其他VME接口信号均可直接接入总线背板。

6 结束语

SCV64提供了全面的VME总线至本地总线接口,采用CPLD或FPGA器件实现少量外部逻辑就可实现其与非MC68K系列CPU的连接,但需要对SCV64的工作过程比较了解。本文介绍了SCV64的数据传输和中断处理过程,并给出了外部逻辑的设计思想,用户据此可自行开发VME总线应用系统。

评论