提高数字设计寄生提取的精度

寄生参数提取在集成电路 (IC) 设计中是必不可少的,因为它可以识别可能影响电路性能的意外电阻、电容和电感。这些寄生元件来自电路的布局和互连,会影响信号完整性、功耗和时序。随着 IC 设计缩小到更小的节点,寄生效应变得更加明显,因此精确提取对于确保设计可靠性至关重要。通过对这些效应进行建模,设计人员可以调整电路以保持性能,避免信号延迟或功率损耗等问题,并成功实现设计收敛。

什么是寄生参数提取

在半导体设计中,寄生元件(如电阻、电容和电感)是集成电路 (IC) 物理制造过程中意外但不可避免的元件。这些元素是所用材料和制造过程复杂性的结果。虽然寄生元件不是原始设计的一部分,但它会显著影响电路性能。例如,寄生电阻会导致电压降和功率耗散增加,而寄生电容会导致相邻导线之间的信号延迟、失真和串扰。此外,interconnect parasitic 会引入传播延迟,从而影响 timing 和信号完整性,从而导致更高的功耗和更低的整体性能。

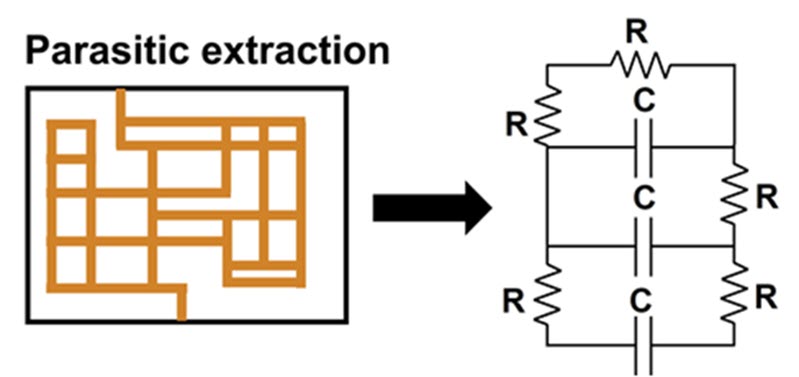

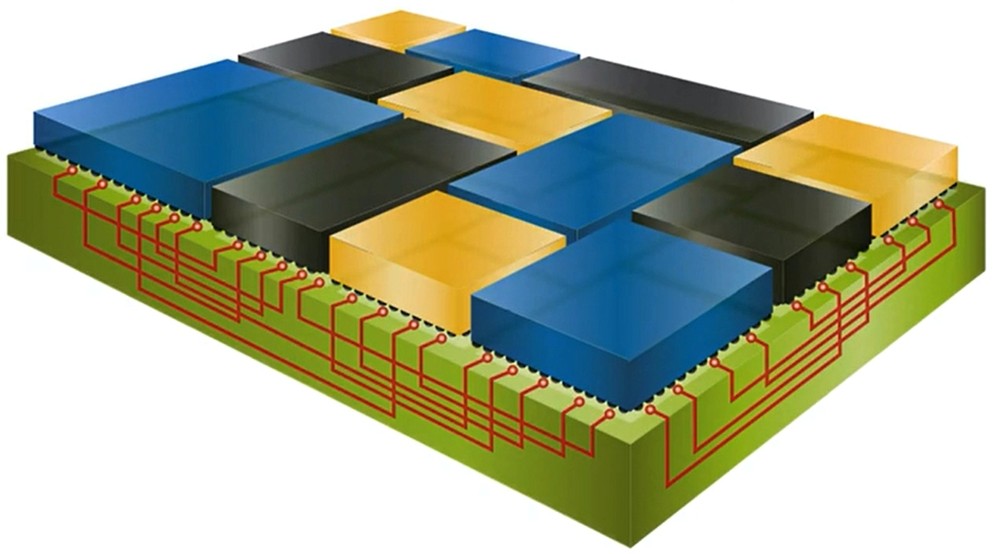

寄生参数提取是 IC 设计中的一个关键过程,用于识别和模拟这些意外的寄生效应,以确保可靠的性能。在数字设计中,寄生参数提取在很大程度上依赖于 LEF (Library Exchange Format) 和 DEF (Design Exchange Format) 等标准化格式,它们描述了设计的逻辑和物理方面(图 1)。

图 1.寄生参数是从有关设计的物理和逻辑信息中提取的。

寄生参数提取过程通常遵循以下关键步骤:

数据准备:此步骤涉及组装和对齐逻辑和物理设计数据,通常来自 LEF 和 DEF 文件。目的是确保每个 logical component 都正确映射到 layout中的相应物理位置,确保寄生 extraction 过程的准确连接。

提取:在提取过程中,从设计布局和技术数据中识别和捕获寄生元件,例如电阻、电容和互连。这构成了理解这些寄生元件如何影响电路整体性能的基础。

归约:提取寄生元后,使用分布式 RC 或集总元模型等模型对其进行简化。这些模型压缩了寄生数据,使其更易于管理,同时仍能准确反映寄生效应以进行仿真和分析。

验证:提取后,对数据进行验证。这包括将寄生参数数据与设计规范和仿真结果进行比较,以确保其符合预期的电路性能,并符合必要的设计规则和签核标准。

优化:验证寄生效应后,设计人员可以应用各种优化技术来减少它们对电路的负面影响。这可能包括优化 routing paths、添加 buffers 或进行其他调整,以提高性能、时序、功耗和信号完整性。

准确的寄生参数提取对于成功的 IC 设计至关重要,尤其是在技术进步和寄生效应变得更加明显的情况下。通过系统地建模、验证和优化这些效应,设计人员可以确保他们的电路在制造和最终生产期间可靠运行并满足所需的规格。

模拟和数字设计流程

模拟和数字设计流程是半导体设计中的两种不同方法,每种方法都适合模拟和数字集成电路 (IC) 的特定要求。模拟设计涉及处理连续信号的电路,例如放大器、滤波器和模数转换器 (ADC)。在这些电路中,精度对于降低噪声、失真和功耗至关重要。设计人员面临的挑战包括平衡电源效率和降噪之间的权衡,需要手动调整布局以避免因微小变化而导致的性能问题。SPICE 仿真器等工具有助于对不同条件下的电路行为进行建模,以确保可靠性和性能。模拟电路对其物理布局高度敏感,并在不同的工作条件下进行了全面测试。

另一方面,数字设计侧重于使用二进制信号(0 和 1)的电路和组件,例如逻辑门、触发器和各种类型的逻辑电路。数字设计优先考虑速度、能源效率和抗噪性,更多地依赖自动化和标准化组件来简化流程。Verilog 和 VHDL 等工具允许设计人员定义电路的行为,然后将其自动综合到布局中。数字工作流程利用时序分析、逻辑仿真和验证工具来确保电路正常运行并满足性能要求。虽然数字电路可能很复杂,但与模拟电路相比,它们的二进制特性允许更直接的布局。

然而,随着技术的进步和节点规模的缩小,模拟和数字设计都面临着新的挑战。模拟设计必须处理增加的噪声灵敏度和寄生效应,而数字设计需要解决更高电路密度下的时序、功耗和信号完整性问题。尽管存在这些复杂性,但现代设计工具和方法有助于确保 IC 满足所需的性能、功耗和可靠性标准。这两种设计流程在 IC 开发中都发挥着关键的互补作用,模拟设计侧重于精度和手动调整,而数字设计则强调自动化和效率。这两个领域的设计人员都必须在快速发展的技术环境中进行复杂的权衡,以生产高性能、可靠的 IC。

寄生提取工具

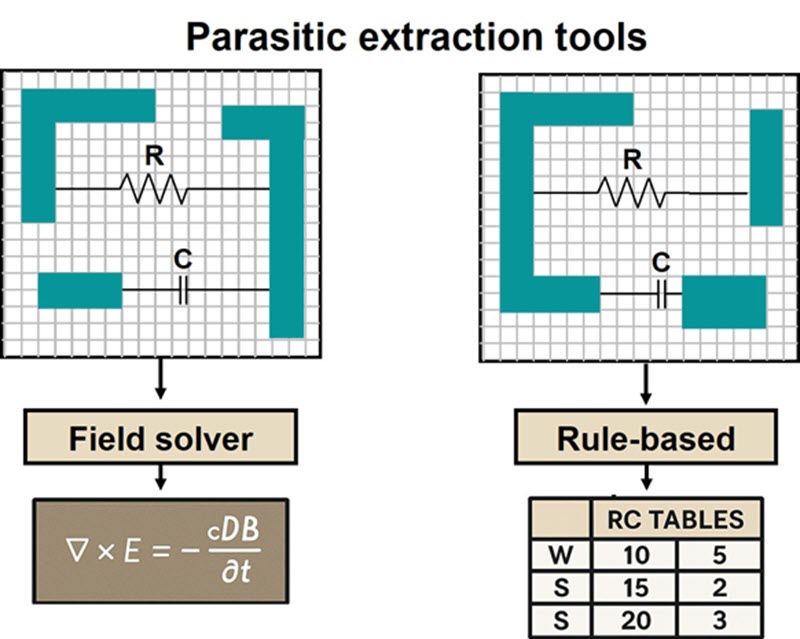

用于半导体设计的寄生提取工具通常分为三大类:基于场求解器、基于规则的提取和模式匹配,每种工具都有自己的优势,适合不同的设计要求(图 2)。

图 2.用于寄生提取的软件工具传统上是场求解器或基于规则的工具。模式匹配是一种较新的技术。

场求解器。基于场求解器的方法使用数值技术来求解电磁场方程,例如麦克斯韦方程组,这使它们能够高精度地对复杂的几何形状和互连进行建模。这些方法在捕获分布式寄生方面表现出色,这使得它们对于对电磁现象的详细洞察至关重要的设计特别有用。这种精度对于高频电路、射频 (RF) 设计和其他需要深入了解寄生效应以确保性能完整性的高级应用至关重要。然而,场求解器方法的权衡是它们的计算强度。由于它们求解跨精细几何细节的复杂数学方程,因此需要大量的计算资源和时间,尤其是在应用于大规模设计时。这限制了它们在日常工作流程中的广泛使用,使它们主要用于需要最高准确性的专业任务。

基于规则。相比之下,基于规则的提取工具根据预定义的模型和设计指南进行作,这使它们能够以更快、更可扩展的方式估计寄生元素。这些工具依赖于从以前的模拟和物理定律中得出的既定规则,将它们应用于整个设计布局以提取寄生效应。尽管基于规则的方法可能无法捕获与现场求解器相同水平的精细细节,但它们效率很高,可提供更快的提取时间,并且能够处理更大、更复杂的设计,而不会占用大量计算资源。这使它们成为大多数数字和模拟 IC 设计工作流程的首选,在这些工作流程中,设计人员优先考虑速度、精度和可扩展性之间的平衡。基于规则的工具特别适合主流应用,在这些应用中,精度的权衡是可以接受的,并且设计几何形状不像高频或射频电路那样复杂或要求苛刻。这些工具也更加用户友好,需要更少的设置和计算开销,使它们可用于更广泛的设计项目。

模式匹配通常被认为是一种 2.5D 提取技术,通过识别设计中重复出现的布局模式来提供帮助。它使用特定几何配置的预先表征寄生值来加快提取过程,而无需对每个实例执行复杂的计算。图案匹配提供了速度和精度之间的平衡,使其适用于涉及重复结构的大规模设计,例如标准单元或重复电路块。

选择提取工具

不同寄生提取工具之间的决定取决于设计的具体需求。场求解器方法非常适合精度不影响的特殊应用,例如射频、微波和毫米波设计,或具有密集和复杂互连结构的高级节点。基于规则的工具是主流设计流程的支柱,为大多数数字和模拟 IC 提供实用且可扩展的解决方案。图案匹配提供了灵活的中间解决方案,提高了重复结构的提取效率。

设计人员必须评估其设计的性能、资源限制和复杂性,以选择适当的方法。在许多情况下,可以使用不同方法的组合:用于需要高精度的关键区域的现场求解器和基于规则的方法用于大部分设计,在整个设计过程中提供效率和准确性的最佳平衡,以及模式匹配以优化重复设计模式的效率。

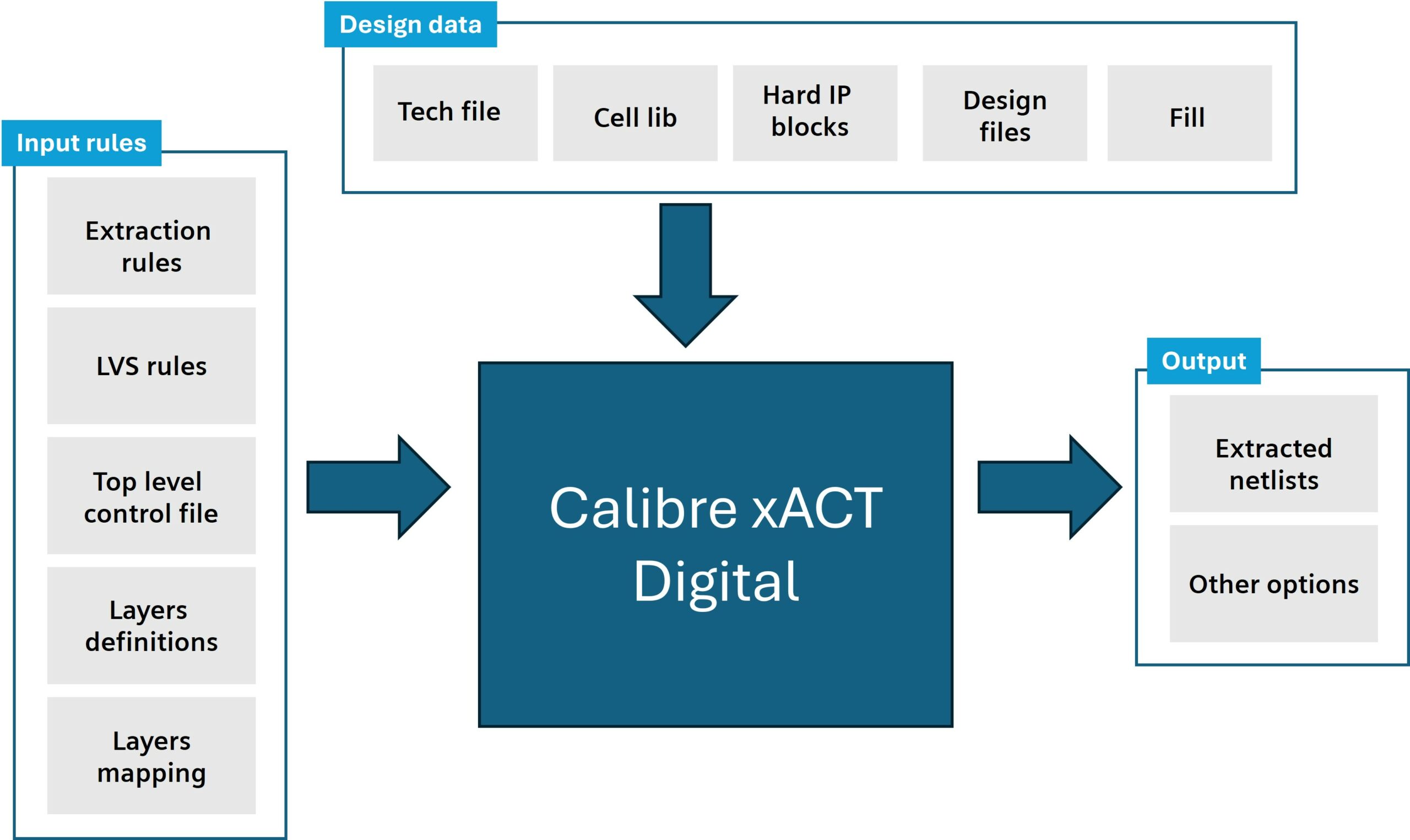

有一些工具,包括 Calibre xACT,它采用基于规则和场求解器的方法,并提供模式匹配。对于大多数设计人员来说,拥有一种高精度的工具来提取互连寄生效应(如电阻和电容)对于了解IC性能至关重要。先进的提取工具可以捕获 IC 内互连和器件之间的详细交互,为优化设计性能和解决信号完整性挑战提供重要见解(图 3)。

图 3.数字提取流的输入和输出。

图 3.数字提取流的输入和输出。

结论

高效的寄生提取对于通过精确建模电阻、电容和其他寄生元件来优化 IC 性能至关重要。设计人员在提取工具方面有多种选择,因此应考虑支持模拟和数字设计流程、能够发现并减轻影响信号完整性、时序收敛和电源效率的寄生效应,并且适用于所有设计节点的工具。精确的提取结果可帮助设计人员在设计过程的早期做出明智的决策,确保稳健可靠的 IC 开发。

评论