使用开源工具设计芯片:Silicluster的发展

在半导体设计领域,从头开始学习设计芯片的挑战常常被低估。工具和知识方面的障碍可能是压倒性的。然而,随着开源软件和硬件计划的兴起,对于那些希望接受这一挑战的人来说,出现了一个新的机会。

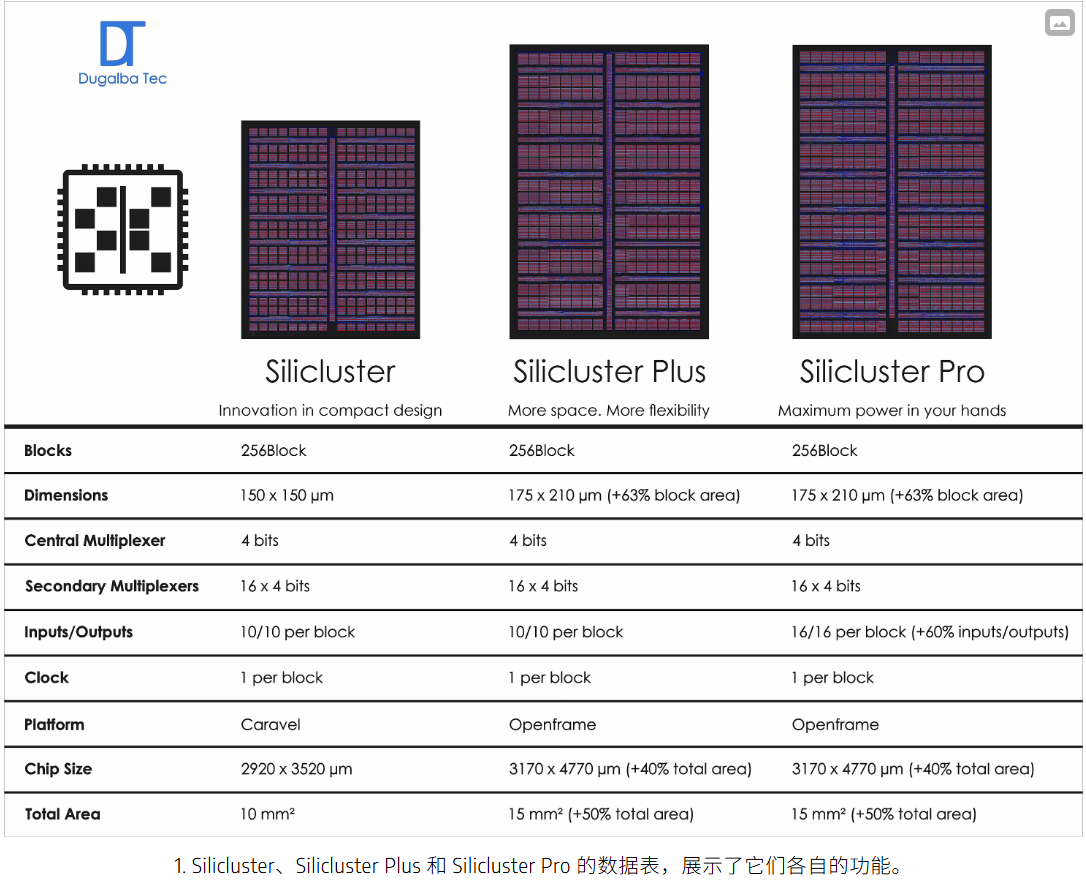

本文详细介绍了设计 Silicluster 的过程,这是一种使用开源工具设计的芯片,重点关注可访问性和可负担性(图 1)。

芯片设计的开始

芯片设计之旅出人意料地开始了。从小,人们就一直对事物的运作方式着迷,但从未想过这种好奇心会转化为对电子产品的热情。学术道路导致我攻读了电子工程学士学位、电子设计硕士学位,并最终获得了博士学位。

然而,后来人们发现,使用传统芯片设计工具的高成本和障碍是一个挑战。在许多墨西哥机构中,由于许可证成本高昂,无法获得高端工具。

这一认识导致了对开源工具的探索,这有望减少半导体设计的障碍。它导致了 Silicluster 的创建,这是一种旨在让学生、教育工作者和小型企业都能负担得起且易于使用的芯片。

安装和学习工具

这段旅程中面临的第一个障碍是安装必要的工具。与拥有官方支持和文档的传统商业 EDA 工具不同,开源工具更像是一种“自己动手”的体验。这是首次与用于 RTL 到 GDS 流程的 OpenLane 和用于原理图捕获的 Xschem 等工具进行交互。虽然没有官方支持结构,但社区和可用文档有助于入门。

最大的挑战之一是应对安装过程的复杂性。每个工具都需要不同的依赖关系,即使在安装后,也需要一个学习曲线来了解如何有效地使用它们。不过,回报是值得的。Magic、Netgen 和 OpenLane 等工具使设计和制造定制芯片成为可能,而成本仅为传统解决方案的一小部分。

学习过程需要时间,但社区的协作性质使其成为一种更有价值的体验。如今,这些工具可以相对轻松地安装,并且由于共享知识和社区努力,该过程变得更加顺利。

设计选择:Silicluster

当需要选择要设计的芯片时,目标是创造一些可以作为各种项目基础的东西。这个想法是设计一种可以容纳多个小模块(多达 256 个独立电路)并且足够灵活以处理数字和模拟信号的芯片。这导致了 Silicluster 的发展。

该芯片的目标是提供一个低成本平台,让多个用户分担制造成本,同时支持独立项目。它基于多路复用架构,其中每个项目(ASIC 或多路复用器)通过辅助多路复用器连接,最终选择由中央多路复用器进行。该架构允许集成多达 16 个单独的模块,从而优化芯片上的空间利用。

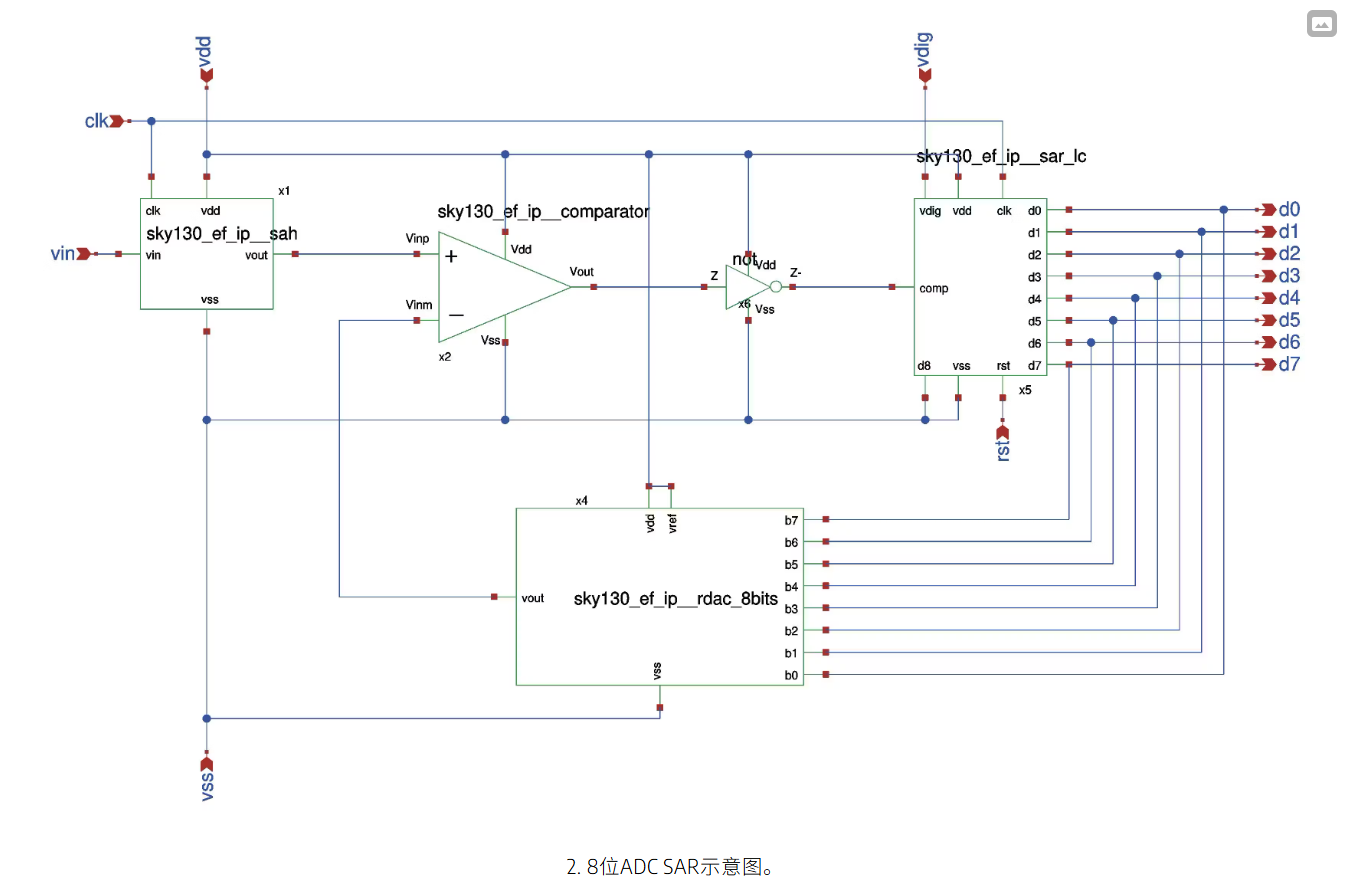

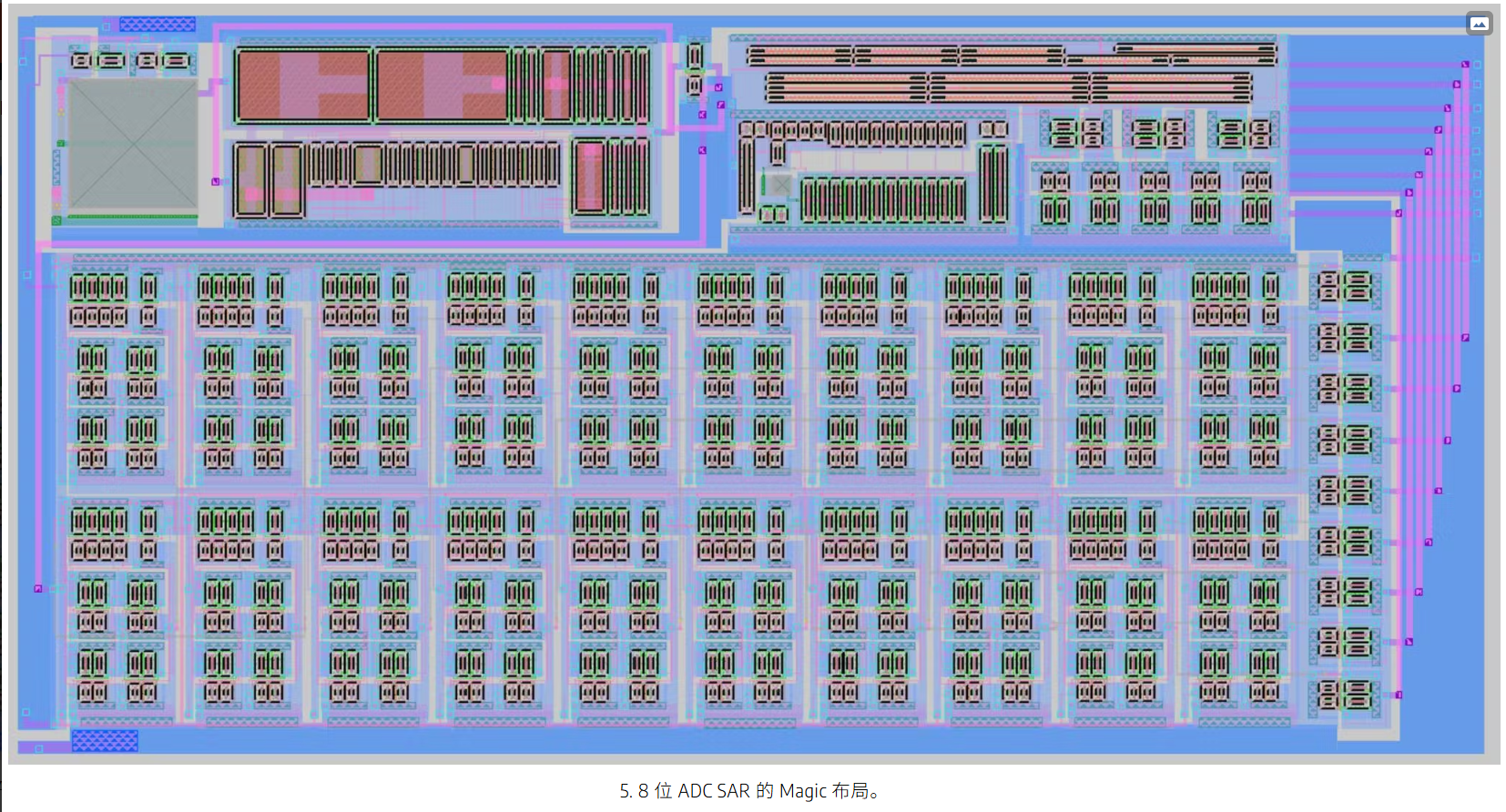

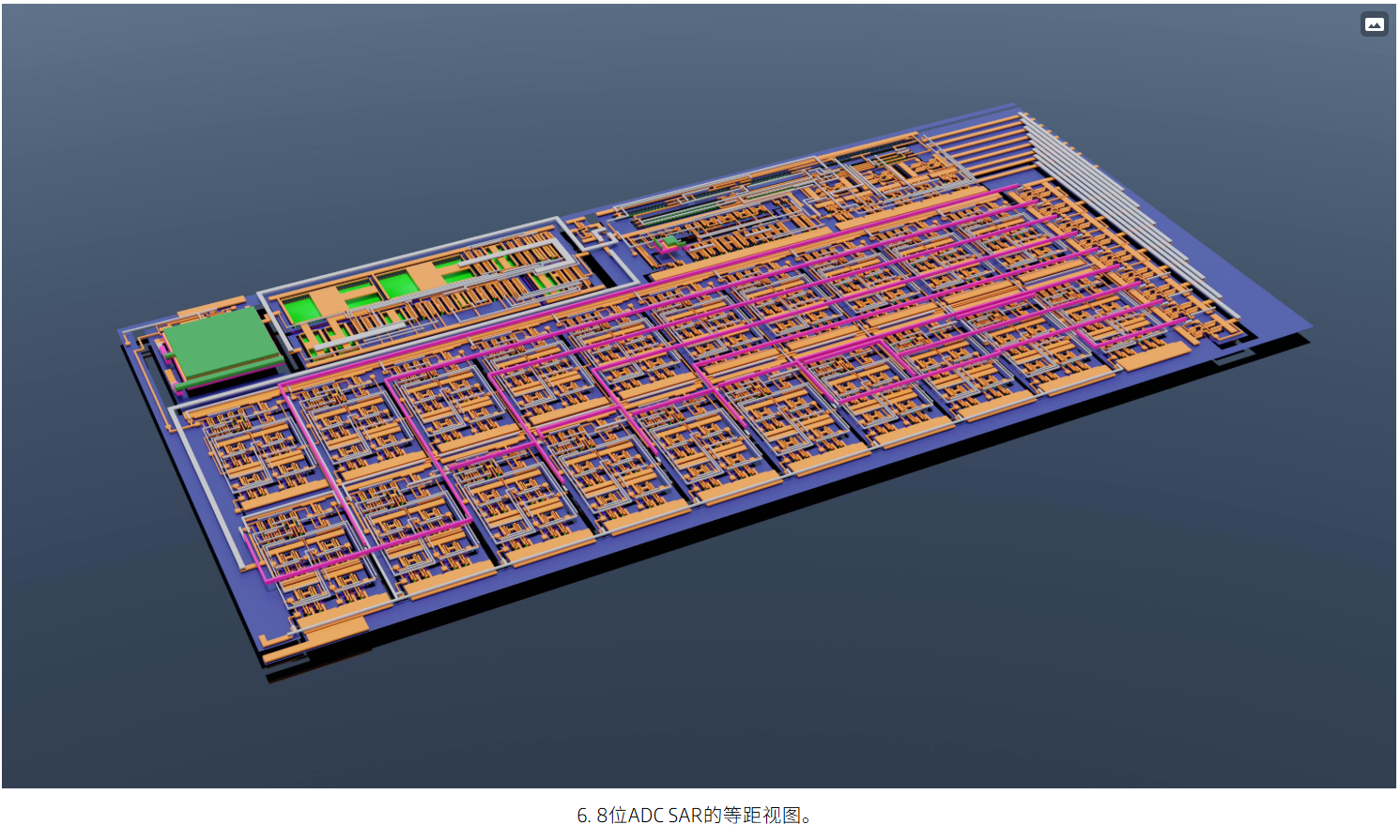

该设计的一个关键部分是 8 位逐次逼近寄存器 (SAR) ADC,负责将模拟信号转换为数字信号(图 2)。

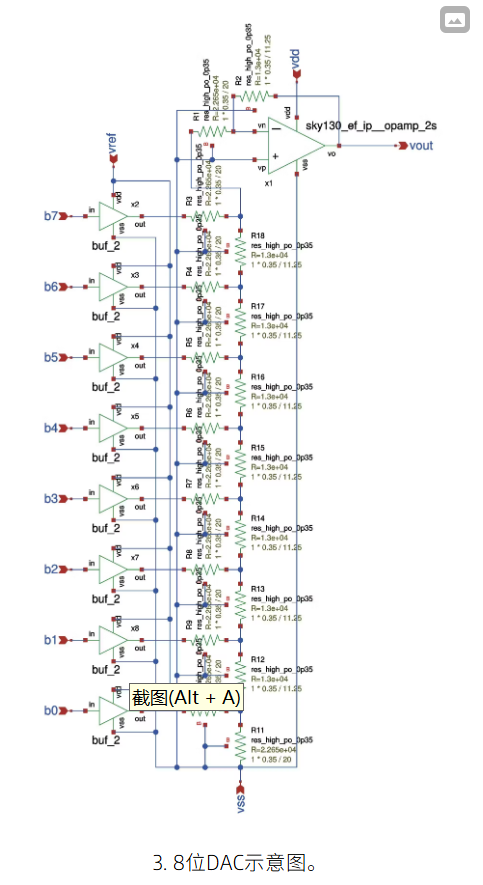

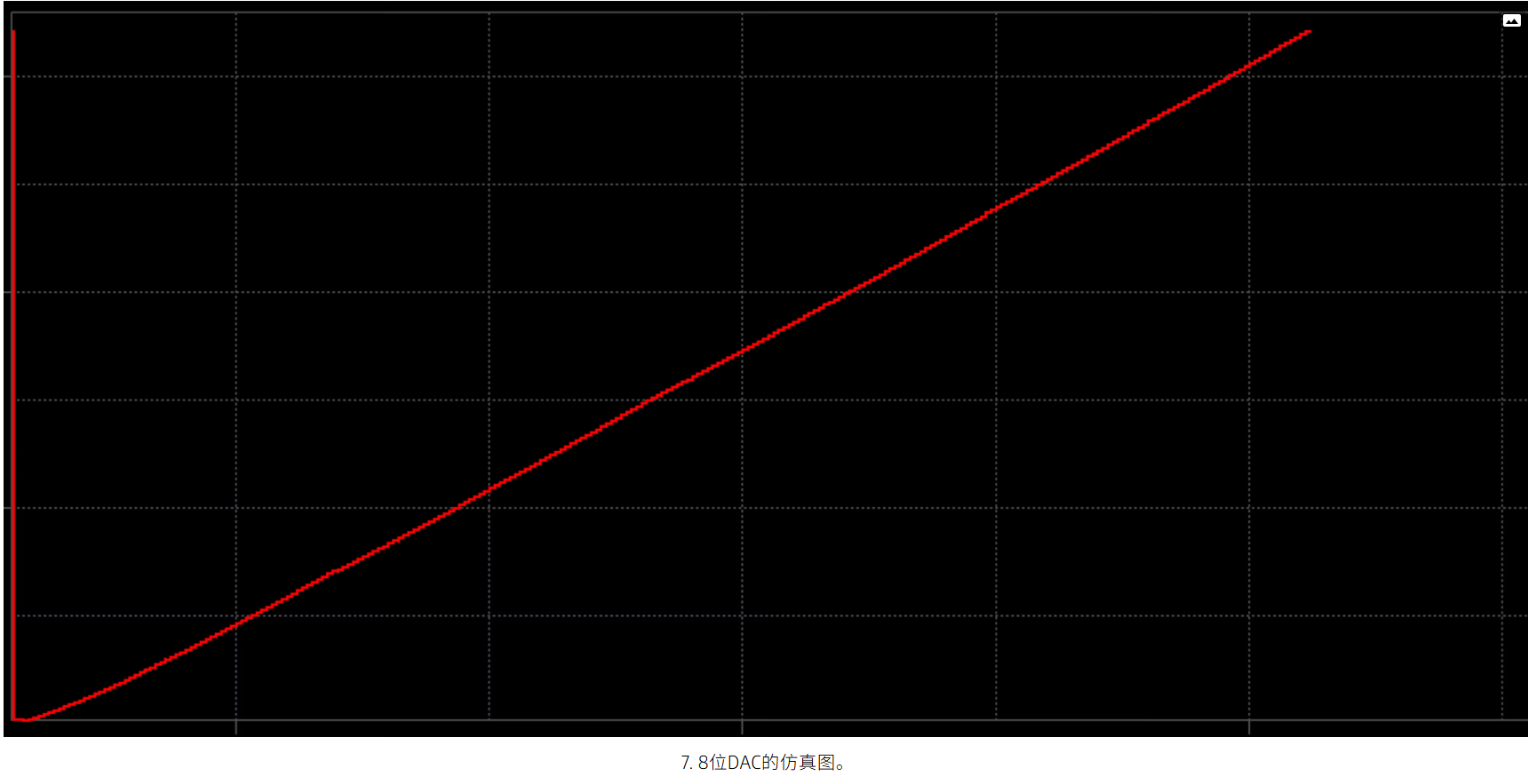

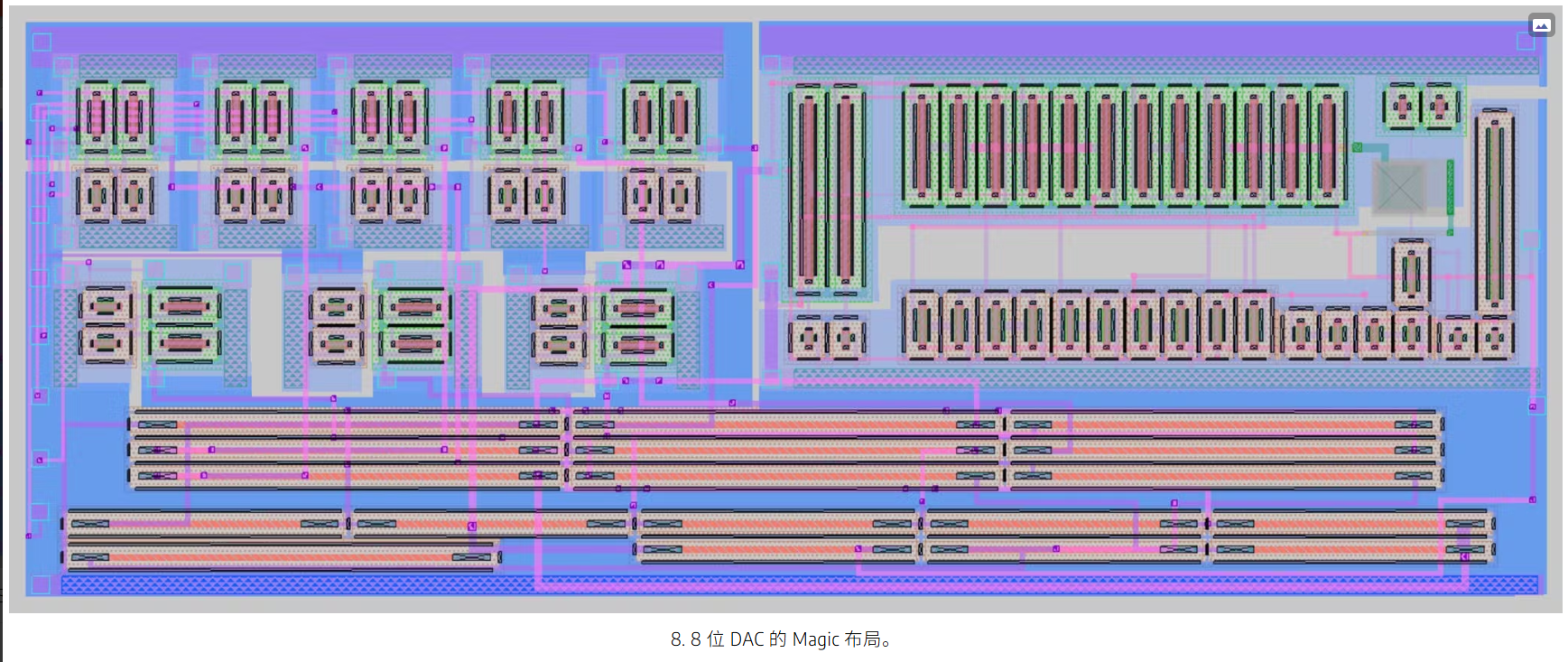

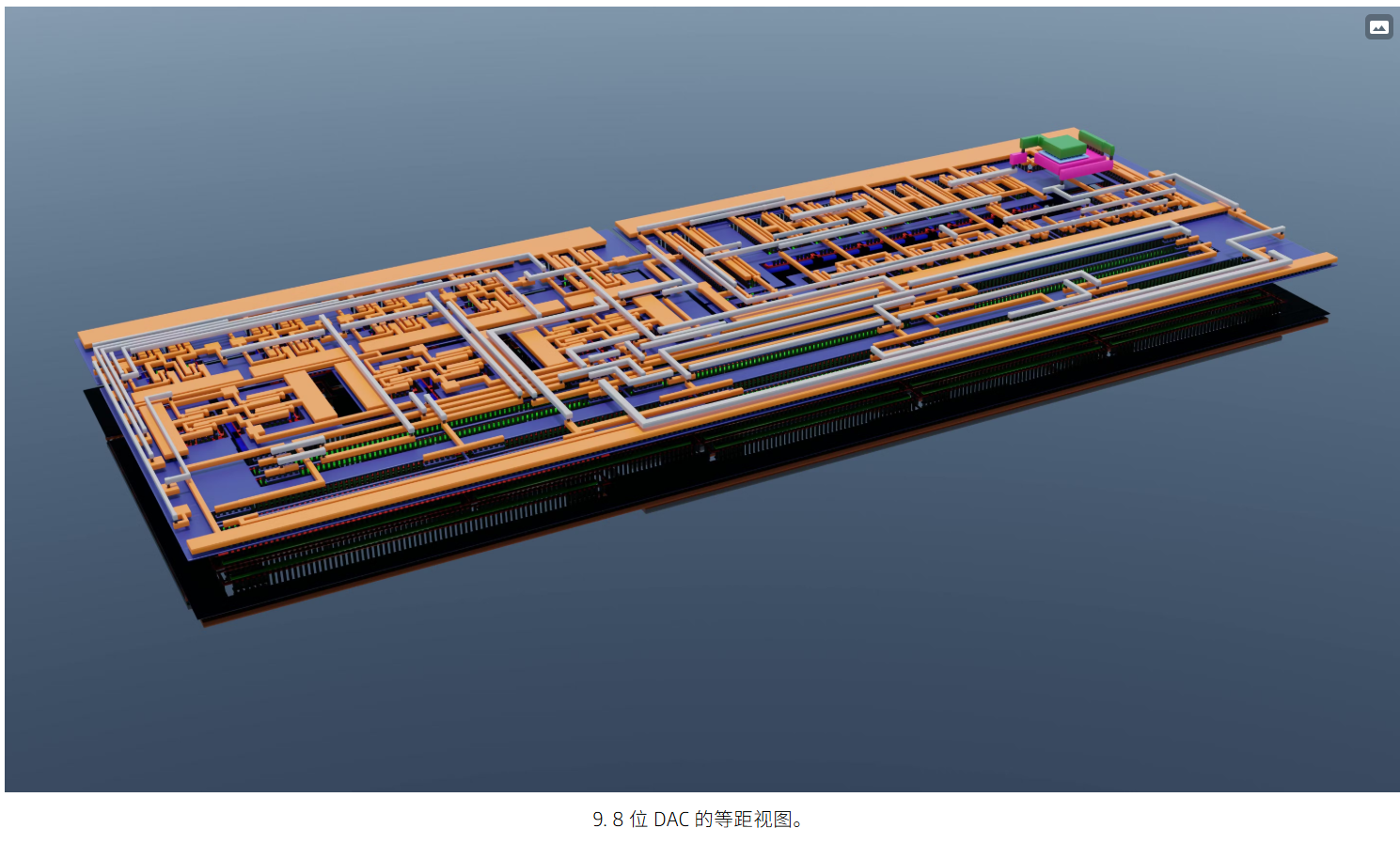

这与 8 位 DAC 相辅相成,以确保芯片的数字和模拟组件之间的兼容性(图 3)。

将模拟和数字电路集成到单个设计中的能力是 Silicluster 最吸引人的功能之一。它为希望构建复杂系统而无需为每个功能使用单独芯片的用户提供了许多可能性。

Silicluster 背后的技术

Silicluster 采用 SkyWater 的 130 纳米技术设计,这是开源半导体项目的经济实惠且功能强大的选择。这项技术与开源工具相结合,大大降低了与芯片设计和制造相关的成本。

值得一提的一个重要方面是这个过程中的中介:Efabless,一家促进设计师和制造设施之间联系的公司。通过 Efabless,可以利用可用的制造基础设施,而无需传统方法的高成本。这种合作对于实现 Silicluster 和其他项目至关重要。

学习电路设计

Silicluster 的设计涉及学习电路设计的基本原理以及构建可以处理数字和模拟信号的芯片所需的具体细节。首先,我们查阅了经典书籍和在线资源,例如 Allen 和 Holberg 的 CMOS 模拟电路设计,以了解模拟电路的复杂性。

同时,回顾了数字逻辑设计的教程和文档,重点关注电路不同组件之间的相互作用。一个关键的要点是使电路的每个部分尽可能高效的重要性。

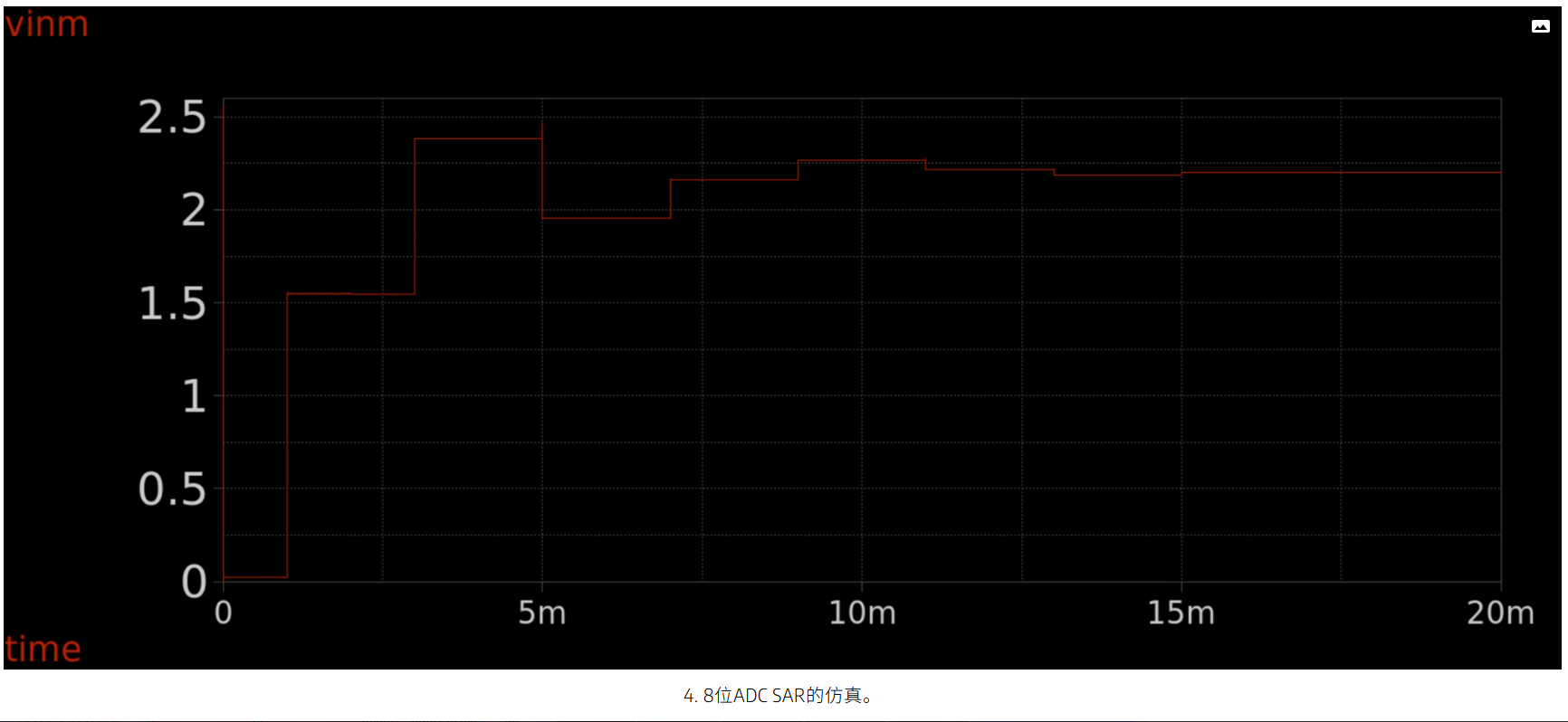

设计具有合理分辨率(图4)的ADC,以适应芯片的严格面积限制(图5和6),同时保持低功耗是一项需要仔细考虑的挑战。

设计流程:原理图、仿真、布局

在对电路要求有了深入的了解后,是时候继续设计流程了。第一步是使用 Xschem 进行示意图捕获。创建原理图既是一次有益又令人沮丧的经历,因为必须就每个组件的配置做出许多决定。

完成原理图后,使用ngspice进行仿真,以验证电路是否按预期工作,如图7所示的DAC。仿真有助于识别可能影响芯片功能的问题,例如信号完整性问题或不正确的配置。

通过仿真验证原理图后,下一阶段是布局。这尤其具有挑战性,因为它需要将设计安装到非常小的芯片区域中。空间限制虽然在创新方面令人兴奋,但也造成了设计瓶颈。

每个组件的放置都必须正确,而且必须以最小化干扰和最大化性能的方式排列。这部分设计过程需要多次迭代,因为每个布局决策都会影响后续步骤(图8和图9)。

布局完成后,Magic 和 OpenLane 等工具将用于最后步骤:DRC(设计规则检查)、LVS(布局与原理图)和 GDSII 生成。此过程的每一步都需要仔细注意,以确保最终设计能够顺利制造。

设计流程中最困难的部分是在芯片有限的区域内调整所有内容。在优化空间、功耗和功能设计之间不断来回,这让人筋疲力尽,但最终是必要的,以确保芯片能够在现实条件下运行。

经验教训和需要改进的领域

设计 Silicluster 是一个复杂但回报丰厚的过程。我们学到的最重要的经验之一是迭代和仔细规划的价值。事后看来,在设计的早期阶段,本可以花更多的时间来完善架构,以更好地适应布局约束。这将在流程的后期节省大量时间,因为有几次重新设计设计以适应可用空间的情况。

另一个学习经验是,使用开源工具需要耐心和创造力。很多时候,无论是通过论坛、GitHub 上的问题还是阅读大量文档,都会向社区寻求支持。使工具顺利运行的过程教会了坚持和协作的价值。

下一步是什么?

展望未来,计划继续完善 Silicluster 并将新功能集成到设计中。目的是提高芯片的能效,并可能探索更先进的制造技术,例如使用更新的工艺或集成更复杂的模数转换机制。此外,该芯片应该更容易获得,为其他人提供全面的指南,让他们使用所学的工具设计自己的芯片。

未来的项目还有其他想法,包括开发一种针对物联网应用的新型低功耗微控制器芯片。这将建立在 Silicluster 的经验教训之上,但更具体地关注某些市场。

最后的想法:会推荐吗?

对于那些有数字或模拟电路设计经验的人来说,绝对推荐尝试使用开源工具设计芯片。这个过程乍一看似乎令人生畏,但学习经验是无价的。这是扩展半导体设计知识和获得实践经验的绝佳方式。

对于初学者来说,建议先从更简单的项目开始,然后再处理像 Silicluster 这样复杂的项目。但无论经验水平如何,当今可用的工具和资源都使芯片设计比以往任何时候都更容易获得。

评论