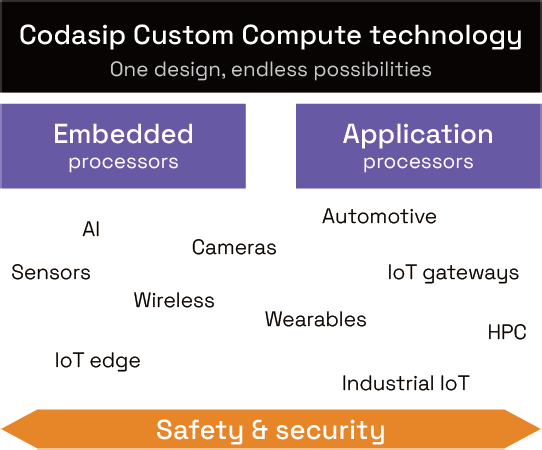

助力RISC-V处理器用于边缘AI,Codasip提供EDA工具集和IP

1 关注的嵌入式AI市场

机器学习算法给我们的生活带来的益处是前所未有的。我们看到越来越多的智能应用正在靠近边缘,并集成到各种类型的产品中。

胡征宇(Codasip大中华区总经理)

随着对高性能处理器的需求不断增长,摩尔定律等半导体缩放定律继续显示出其局限性,对处理器优化的需求不可避免;RISC-V 的设计就是为了实现这一种优化的演进模式。然而,没有放之四海而皆准的处理器优化方法:由于每个工作负载和应用都有自己的需求,实际上存在不同的优化方法。您可以在不同层面修改处理器IP,而每个层面都有自己特有的价值和优点。通过为RISC-V 处理器提供定制功能,更大范围的算法可以在边缘得到实现。

Codasip 是一家专门帮助开发人员使其产品实现差异化的处理器解决方案公司。我们通过结合开放的RISC-V ISA、Codasip Studio 处理器设计自动化工具集和高质量的处理器IP 来提供定制计算。

2 工程师遇到的开发挑战

开发人员主要面临与机器学习算法所需计算要求相关的挑战。这些要求可能总体量很大,并且在小型边缘计算上实现此类算法的实际情况中,它们可能因受到限制而成为更小、更简单的模型。但是,可以通过将定制化引入到给定模型中,来解决小型处理器可能必须要去处理的问题。这种定制化功能可以实现更快的模型推理、更低的功耗和更高的应用性能。

在Codasip,我们不认为存在一种固定和绝对的性能、功耗和芯片面积(PPA)指标衡量标准。重要的是我们的客户在其最终芯片中获得的最终PPA 指标,因此使用相同IP 的不同客户得到的PPA 则很可能大不相同。无需花费大量时间手动调整IP,您可以使用我们的工具来定制IP,以获得比市场上任何产品都更好的PPA。而且,当您在同一个SoC 中使用多个处理器时,您可以决定对每个处理器进行不同的优化,以确保获得最大效率。

3 Codasip的解决方案

借助我们的工具链Codasip Studio,我们可提供处理器设计自动化工具。客户可以从我们的任何一个基准性IP 内核开始,然后做出最佳的软件和硬件权衡,并实现最优功能和PPA。

我们的L31 内核是一款低功耗、通用型的嵌入式RISC-V CPU,在人工智能边缘设备中很受欢迎。我们最近还推出了A730 内核,这是一款多功能的中端64 位应用内核,能够运行Linux 和RTOS,非常适合在功率受限的设备上执行复杂的计算任务。A730 内核经过高度优化,具有更大的灵活性。它可以通过控制以下几个选项来适应特定的用例,包括:

● 内核数量:1~4 个

● 具有可定制内存映射的内存保护

● 分支预测

● 指令和数据缓存大小

● 共享L2 缓存大小和结合性

● 转译后备缓冲器(TLB)

(本文来源于《EEPW》2023年11月期)

评论