满足数据中心和服务器 SMPS 发展趋势需求的封装和热解决方案

云端互联网服务、人工智能和加密货币相继出现,推动全球数据中心处理能力迅速发展。此外,电力和房地产价格持续攀升,这一趋势迫切需要高效紧凑的服务器电源。本文将阐述如何使用硅和宽禁带 (WBG) 开关来满足电源设计要求。

本文引用地址:https://www.eepw.com.cn/article/202210/439460.htm为实现所需的高功率密度,必须考虑以下三个主要方面:

● 提高效率,为了保持特定体积下的总功率损失在接受范围之内,从而推动向新拓扑和新技术过渡;其中的成功示例就是从采用硅 (Si)实现的 经典升压 PFC 到采用 GaN/SiC实现的 图腾柱 PFC。

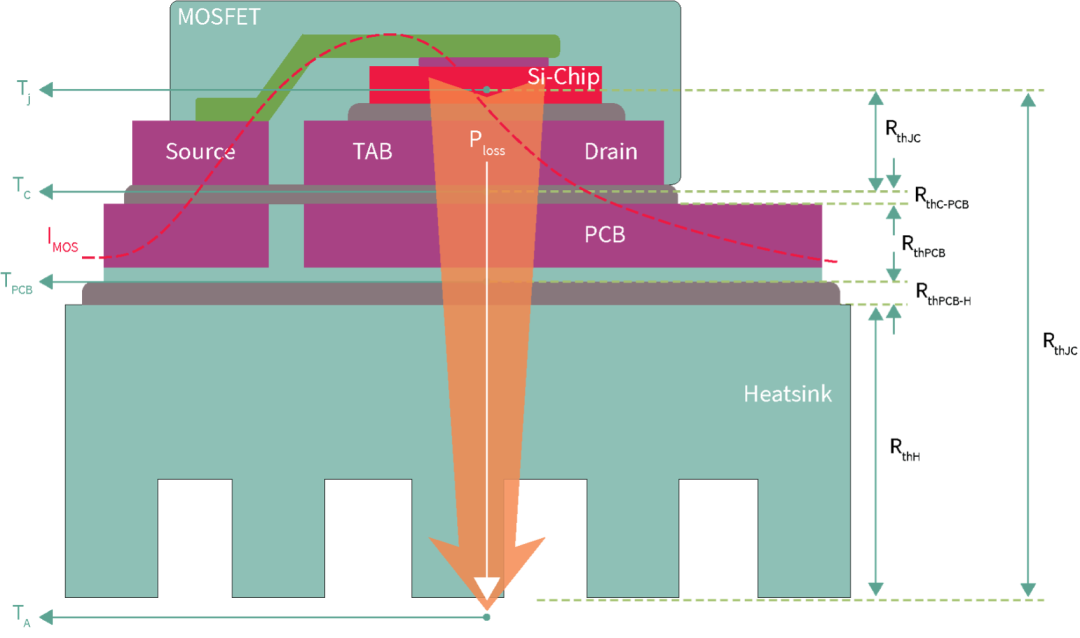

● 改进封装和热解决方案可将器件结点处热能向散热器和周围环境耗散。小型 SMD 封装是高密度转换器的主要推动因素,对其而言,这更具挑战性。

● 优化系统设计和开关频率,在满足效率要求或温升限制下获得最高的功率密度。进而促使开关频率的提升,推动从传统封装过渡至新型封装和热解决方案。

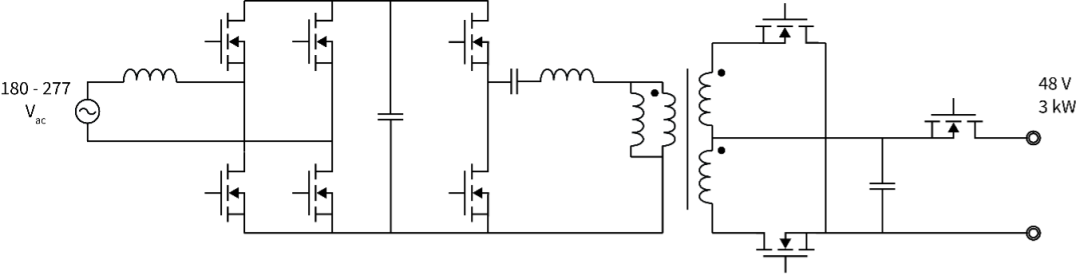

通常情况下,最先进的高效电源由图腾柱无桥 PFC 级和 LLC 转换器等谐振 DC-DC 级组成(见图 1)。服务器电源的示例规格为 Vin = 180 V – 277 V,Vout = 48 V,Pout = 3 kW。

图1. 由图腾柱 PFC 和 LLC DC-DC 转换器组成的服务器电源

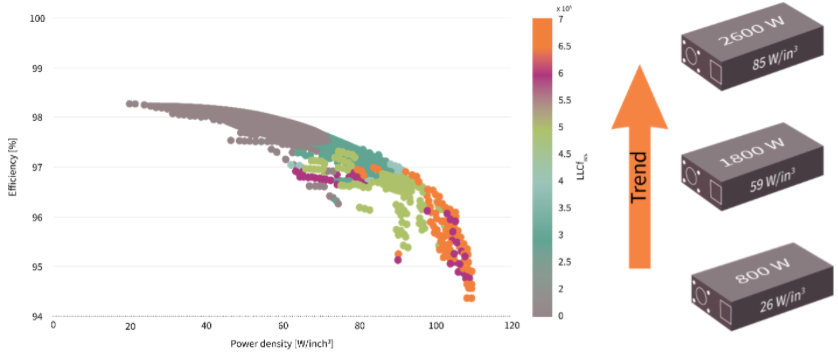

为量化效率与功率密度之间性能权衡,采用了帕累托最优分析。该方法系统考虑不同转换器系统设计中的所有可用自由度。通过采用详细的系统和组件模型,可确定位于帕累托前沿的最佳设计。该效率计算的基础为 50% 额定输出功率,包括 PFC 和 LLC 级损耗。

计算整个服务器电源系统的帕累托前沿,优化结果如图 2 所示。该图表明,对于中等功率密度 (~40 W/inch3 ),效率可接近 98.2%,而超过 80 W/inch3 的设计,效率则低于 97.5%。从该图得出的另一重要结论为:LLC 级的开关频率越高,所需功率密度设计也越高。这些结论证实了封装在高频工况下实现高效的必要性。

图2. 采用优化 LLC 级频率的整个服务器电源的优化结果,展示效率与密度间的关系

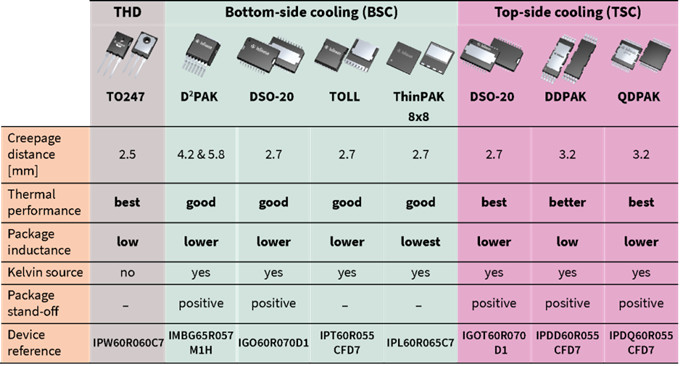

SMPS 拓扑所用 SMD 封装

英飞凌提供广泛的底部散热 (BSC) 和顶部散热 (TSC) 封装产品组合,可满足高功率和高密度服务器 SMPS 应用的发展趋势。本节讨论并对比了与装配、热性能和电气寄生参数等主题相关的不同封装。

底部散热和顶部散热封装的组装实现

底部散热 (BSC)

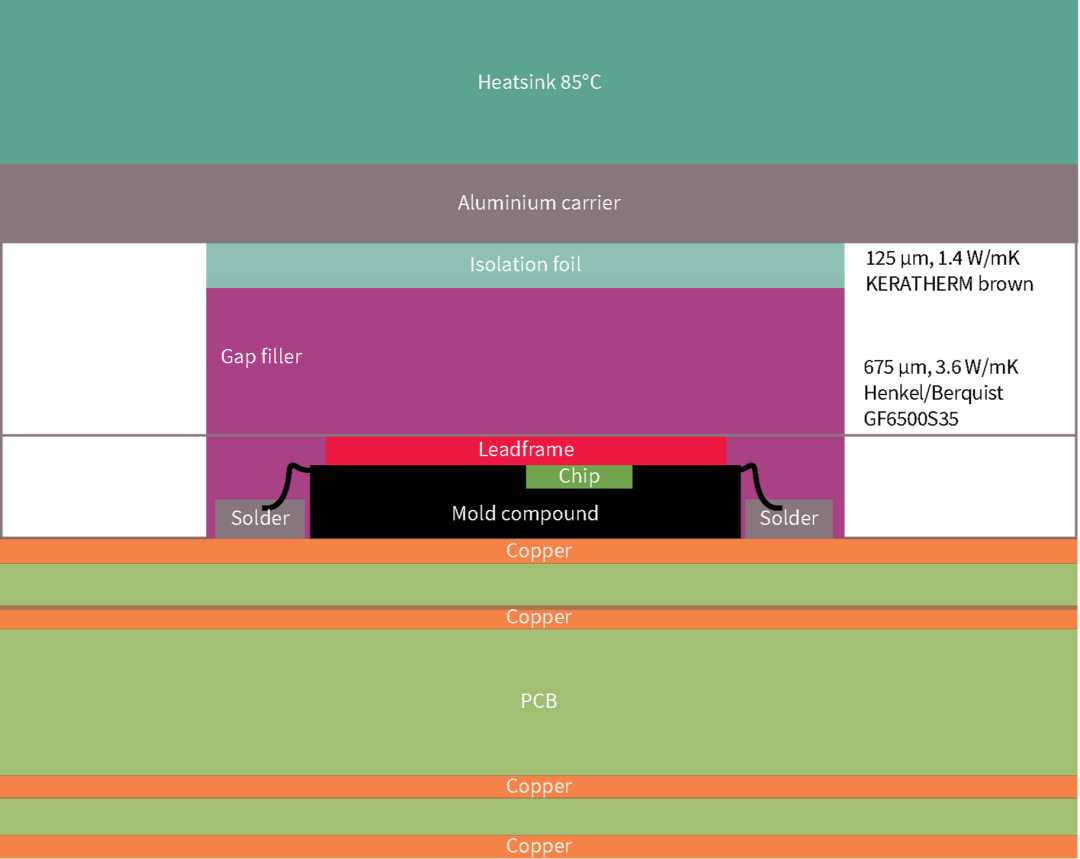

图 3 和 4 所示为底部散热和顶部散热的主要散热概念。在这两种情况下,通常采用回流焊接工艺将 SMD 封装安装在 PCB 上。对于 BSC,主要热量从封装底部的器件散热器(外露焊盘)经 PCB 传导至安装在 PCB 另一侧的外部散热器。因此,使用基于 FR4 的 PCB 时,需要封装下方穿过 PCB 的散热过孔来传热。在 PCB 背面,外部散热器安装在具有散热过孔的区域。散热器和 PCB 通过热界面材料 (TIM) 实现电气隔离。通常情况下,厚度为 100-500 μm 的箔片用作 TIM,在理想状态下具有良好的热导纳 λ。理想情况下,这会使整个系统具有低热阻抗 Zthja。

图3.采用底部冷却的示例解决方案

PCB 具有一定厚度,受电路设计所需铜层数量和散热过孔密度限制的影响。因此,与器件散热器提供的传热面积相比,通过 PCB 传热的有效截面积更小,这是第一个瓶颈。第二个瓶颈是 TIM,其热导纳比器件散热器和外部散热器低得多。

在某些情况下,用绝缘金属基板 (IMS) 替换基于 FR4 的基板,可在不超过器件或 PCB 最高温度的情况下获得更高的热流量。特别是对于单层 PCB 设计,既不需要散热过孔,也不需要额外 TIM。由于电路板的铝基用作散热器,因此无需外部散热器。然而,尽管降低了 Zthja,但板上温度循环 (TCoB) 次数也减少了,特别是无引脚 SMD 封装,比如无引脚 TO 封装(TOLL) 或 ThinPAK,这是因为基于 FR4 的 PCB 非常柔软,而基于 IMS 的 PCB 更为刚硬。

顶部散热(TSC)

在 TSC 封装中,封装顶部的器件散热器通过 TIM 直接与外部散热器相连(图 4)。在这种情况下,没有热量通过 PCB 和散热过孔,因此,这部分热阻不会体现在总热阻中。因而可提高导热性和封装的最高功耗。

此外,TSC 封装的另一优点是 PCB 对面的空闲区域可用于布置其他器件,例如栅极驱动器和无源元件,封装体正下方还具有信号布线空间。

图4.采用顶部冷却的示例解决方案

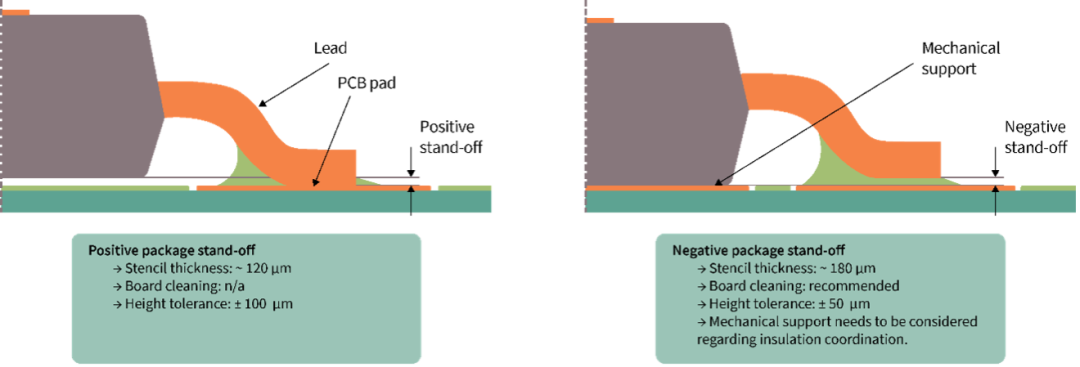

为获得良好热接触,在 TSC 器件上,建议将散热器安装在TSC器件上时施加一定的力。对于具有托脚高差为正的带引脚 SMD 封装(图 5 左),该力和其他温度循环引起的力均被封装引脚吸收,如果使用 QDPAK[6],TCoB 循环可达 2000 次,非常不错。

对于托脚高差为负的封装(图 5 右),为避免系统可靠性问题,PCB 设计需要考虑其他因素,可能会增加系统设计和制造的工作量和复杂性。负托脚高差具有降低 Zthja 的优势,因为其降低了封装高度公差,进而减小了 TIM 的厚度。然而,考虑 PCB 翘曲等其他公差时,特别是对于较大的 PCB 尺寸和多个功率器件共用散热器的情况,负封装托脚高差的热优势不再那么重要。

图5.标准正封装托脚本体高差(左)和负封装托脚本体高差(右)。封装体下方的铜焊盘有利于作为高度确定的机械支撑,对于负托脚本体高差,电路板可靠性非常高 [2]

对于常见散热器方法,图 6 示意性显示了器件和散热器之间的 TIM 堆叠,在本例中由绝缘箔和间隙填充物组成。间隙填充物用于补偿器件、散热器和 PCB 的相关制造公差。仅使用间隙填充物进行传热时,必须确保器件与外部散热器之间的可靠绝缘。此外,间隙填充材料必须满足必要击穿等级,PCB 装配过程中,还需防止气孔和封闭颗粒进入间隙填充物。一般而言,洁净的 PCB 组装制造环境可降低系统制造过程中因污染而导致的系统故障风险。

图6.外部散热器与器件之间的电隔离箔和间隙填充物

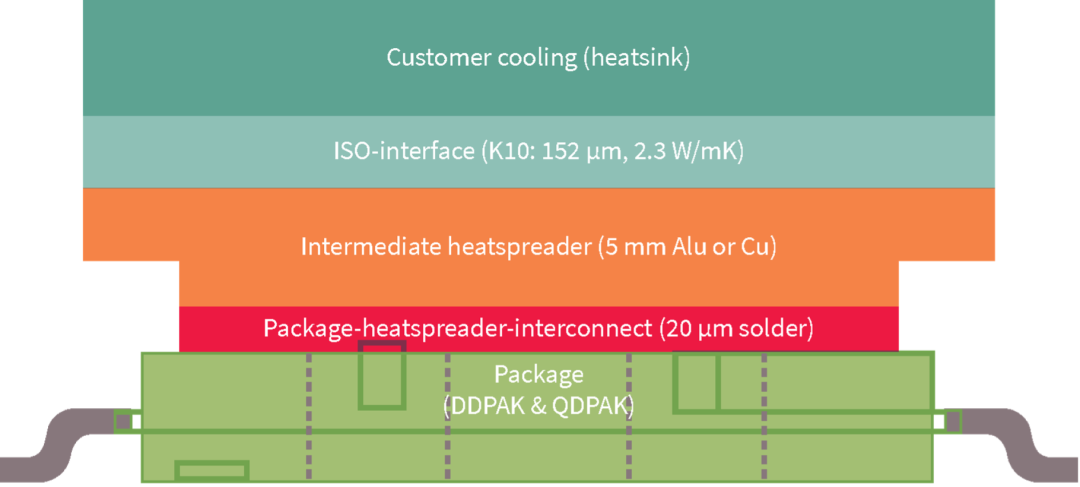

为进一步降低 TSC 的 Zthja 和动态功耗,可选择部署中间散热片,如图 7 所示。该附加散热器的热容量可在一定时间(几秒钟)内储存额外热量,然后再传导至公共散热器和环境中。根据系统设计的不同,为改进系统 Zthja,也可取消公共散热器和 TIM,其中,中间散热片为主要散热器,由风扇气流直接冷却。

图7.单器件散热片安装 [6]

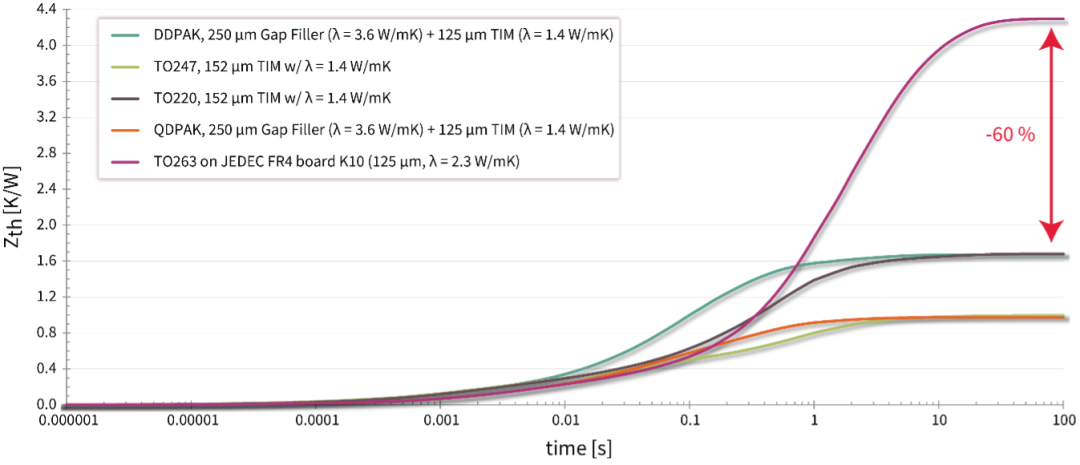

热性能

图 8 显示了所选 THD、BSC SMD 和 TSC SMD 封装的 Zthja 时间相关图表,考虑了基于 FR4 的 PCB 设计和强制风冷。假设不同封装内的相同一芯片器件具有的功耗相同。在基于 FR4 的 PCB 上比较 DDPAK(TSC 封装)与 TO263(BSC 封装),DDPAK 的 Zhtja 降低了 60%,尽管这两种封装的有效散热面积非常接近。DDPAK 避开了上节所述“散热过孔”限制。该图还表明,顶部散热封装能够实现与通孔器件 (THD) 相当的 Zthja 值。

图例表明,使用具有相当高热导纳 (λ) 的薄层隔离材料是实现良好 Zthja 结果的关键。除此之外,使用具有更高 λ 的间隙填充物和隔离箔,将使所示 TSC 封装的 Zthja 比 THD 更低。

图8.强制对流下多封装的典型瞬态抗结-环境热阻 (Zthja)

高频操作中的低寄生电感优势。

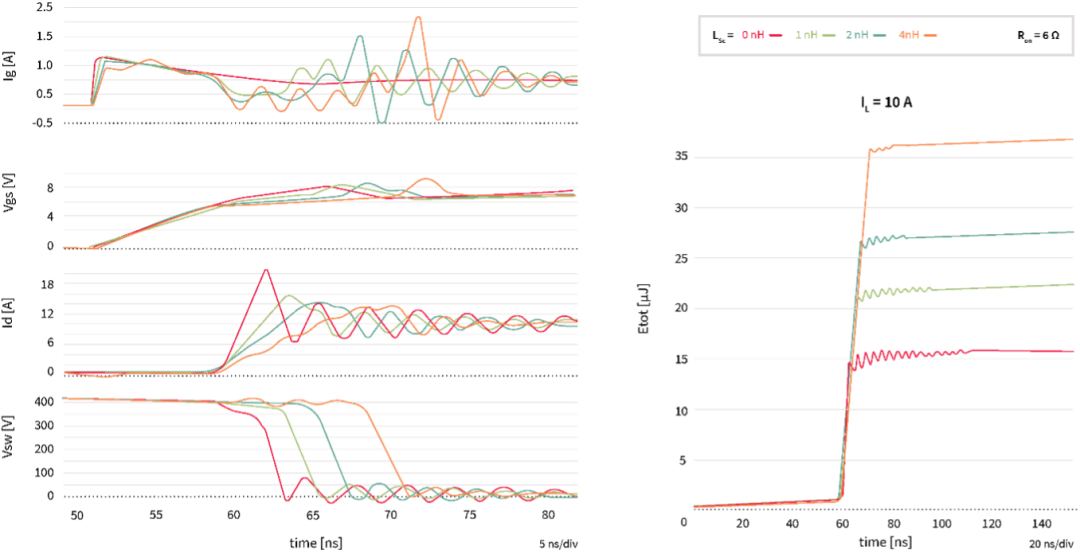

图 9 所示为封装源极电感 (LSc) 对“导通”瞬态的影响。LSc 从 0 增加至 4 nH。漏极电流 (di/dt) 升高导致 LscSc 上的感生压降,栅极驱动电压会减去该电压值,从而降低栅极电流。因此,电压瞬变时间延长,损耗增加。“关断”瞬态的机制相同,但方式相反。

图9.封装源极电感对开关“导通”的影响示例:波形细节(左)和损耗(右)

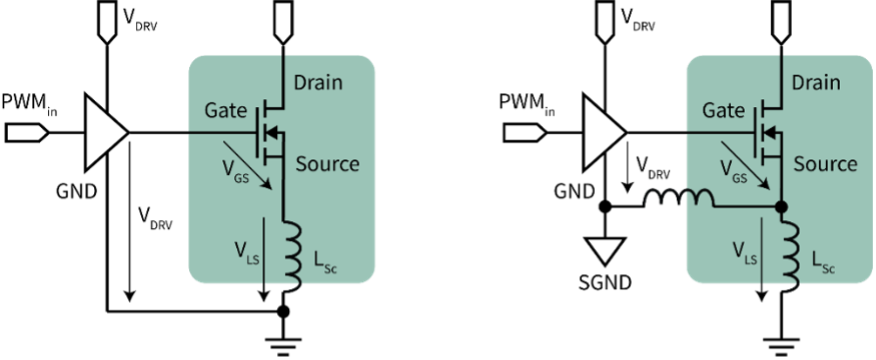

通过使用单独的源极检测引脚(开尔文源极)来控制栅极(图 10,右),可消除上述 LSc 的负面影响,从而有效降低开关损耗。通过使用源极检测连接来驱动栅极,LSc 位于栅极驱动环路之外。因此,其感应电压峰值不会反馈到驱动电路,这与仅有一个源极连接的标准配置(图 10,左)不同。

需特别关注的是,开尔文源极引脚封装解决了 LSc 对栅极驱动和开关速度的负面影响。但是,LSc 仍会增加环路总电感,这是一个关键参数,会导致快速开关应用(例如带有WBG 开关的服务器 SMPS)产生振荡。因此,即使采用开尔文源极引脚封装,封装 LSc 也是越低越好。更多细节见参考应用说明 [7]。

图10.标准 3 端封装(左)和采用开尔文源极的 4 端封装(右)的栅极驱动环路比较

总结

本文讨论了功率半导体封装在满足服务器电源的功率和密度要求方面的重要性,特别是对于硅和宽禁带 (WBG) 开关器件。

首先,简要介绍了服务器 SMPS 的应用和发展趋势,然后讨论了 SMD 封装的装配实现、热性能以及高频操作中的低寄生电感优势。

下表 1 总结了用于服务器 SMPS 中的英飞凌 SMD 封装产品组合,并比较其主要参数。

Table1 服务器应用的 SMD BSC 和 TSC 封装概览。

为评估封装电感,假设封装内器件具有相近 RDS(ON)。

英飞凌开关电源 (SMPS) 设计解决方案可满足日益严苛的服务器和数据中心需求,如需了解更多信息,请单击此处。此外,还可了解我们的全系列创新电源技术(Si、SiC 和 GaN)。

参考资料

1. S. Preimel,“600 V CoolMOS™ G7 和 650 V CoolSiC™ G6 采用新型顶部散热封装 – DDPAK”,应用说明,AN_1802_PL52_1803,2018 年

2. 英飞凌科技,“英飞凌双排欧翼式引脚封装的电路板组装建议”,Rev. 5.0,2020 年

3. 英飞凌科技,“顶部散热型带引脚 TO (TOLT) 封装汽车功率 MOSFET”,应用说明 v1.1,Z8F80044621,2021 年

4. 英飞凌科技,“TOLL 与 TOLT”,应用说明,Z8F80127016,2022 年

5. 英飞凌科技,“适用于高压应用的创新顶部散热封装解决方案”,应用说明 v1.0,AN_2101_PL52_2103_112902,2021 年

6. S. Preimel,“600 V CoolMOS CFD7 采用新型顶部散热封装 – QDPAK”。应用说明,AN_1802_PL52_1803_120439,2018 年

7. B. Zojer,“CoolMOS™ 栅极驱动器和开关动态”,应用说明 v1.0,AN_1909_PL52_1911_173913,2020 年

作者:

Daniel Hölzl,英飞凌科技封装概念工程师

Sam Abdel-Rahman,英飞凌科技系统架构服务器/数据中心 SMPS

评论