毫米波5G接收机多速率数据设计与研究

作者简介:张黎明(1980—),男,移动通信测试事业部高级工程师。目前主要研究方向为移动通信、数字信号处理、电子测量仪器等。E-mail:zlm86400@qq.com。

本文引用地址:https://www.eepw.com.cn/article/202108/427421.htm目前,在毫米波5G 分析仪方面,主要以罗德与施瓦茨(R&S)、是德科技等为代表,其频率范围可达到43.5 GHz 以上,带宽2 GHz,以超外差变频方式产生模拟中频信号输出,EVM 指标优于3.0%,其基带数字信号处理方式以高性能嵌入式硬件加速器为主。国内毫米波5G 测试仪以中电科思仪为代表,频率范围、分析带宽、EVM 解调指标与国外水平相当,但其基带数字信号处理方式以FPGA 处理平台为主。以国家“5G 新基建”政策为引领,为推动国产关键核心器件、基站、终端等设备功能、性能、可靠性等指标进一步提高,依据行业标准和厂家测试需求,研究毫米波5G 信号测试方法,在毫米波5G 技术验证、通信器/ 部件研发、5G 基站外场测试等领域填补了国内空白,实现了国产化毫米波5G 测试仪开拓性创新。[1-2]

1 方案设计

本设计的“并行多相技术和任意深度FFT 处理技术”方案[3-4] 主要完成目标是:

1) 实现5G NR 大带宽信号数据速率高效转换;

2) 采用“任意处理深度”FFT 频域信号分析。

1.1 多速率采样原理方案[5-6]

信号处理领域的采样定理通常可分为低通采样定理和带通采样定理。其中,带通采样定理主要用于将位于一定频带的模拟中频信号下变频到模拟零中频(基带)。而经典奈奎斯特低通采样定理定义为,1 个带宽受限信号可以唯一地由1 组时间间隔不等的均匀釆样值来决定,也就是说当A/D 采样率以不低于信号最高频率两倍采样时,其采样的离散信号样值可以准确恢复原始信号。但是,假如信号最高频率很高且带宽比较窄,此时对信号进行中频低通采样,根据定理则需要高于2 倍最高速率,这将导致A/D 采样速率急剧增高,增大后级数字信号处理(同步解调等)工作量,无法满足实时性要求。综上所述,对于低通采样数据率较高且信号带宽远小于最高频率50% 时,宜采用带通采样定理进行无失真采样。奈奎斯特带通采样定律是,对于一个通带信号x(t) 而言,其信号频带位于[fL,fH] 之间,信号带宽BW=Fh-Fl,则A/D 采样率fS 必须满足下式:

其中,N 为正整数且满足fS ≥ 2B,此时采样率Fs 可以恢复原始模拟信号x(t)。假如,N 为0 且fL 也为0 时,奈奎斯特带通采样定律就变成特殊的低通采样了。同时,用f0=(fL+fH)/2 进行等效代换得到采样率fS 与f0 间关系如下:

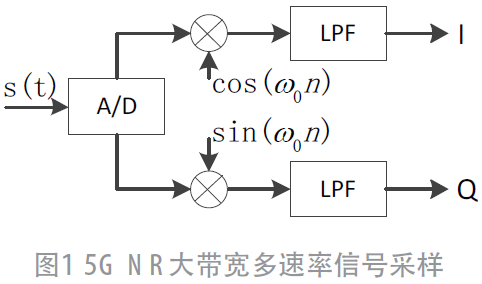

同理,式(2)中N 为正整数且满足fS ≥ 2B。综上所述,5G NR 大带宽多速率信号采样方案如图1 所示。

1.2 多速率重采样原理方案[7-8]

数字信号的重采样即多速率信号处理,其定义为把1 个数字信号采样率从某个固定采样率变换成另一种不同采样率的过程。在5G NR 大带宽接收机设计过程中,由于物理层时频资源配置不同会导致信号BWP 带宽不同,必然会采用重采样技术进行数字信号处理。其中,信号抽取定义为降低信号采样率;信号插值定义为提高信号采样率。

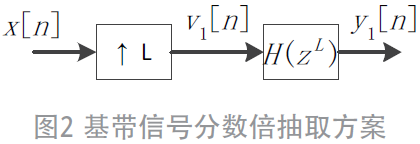

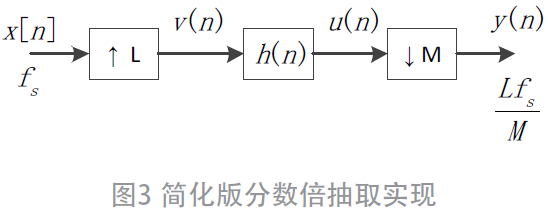

一般来说,5G NR 大带宽信号A/D 采样带宽远远超过实际OFDM 信号处理带宽,此时基带信号严重处于过采样状态,为满足后级解调处理,通常采用抽取来降低数据采样率,进而降低信号信息的冗余度以便后级处理。当釆样率刚好是信号传输速率的整数倍时,通过整数倍抽取就可以降低数据率,这种结构的实现相对容易。但当采样率不是信号传输速率的整数倍时,就涉及到一个分数倍重采样的问题了。此时,需要构建分数倍重采样滤波器组,即先插值后抽取。由插值和抽取级联构成的分数倍抽取方案,如图2 所示。

综上所述,在数字信号处理中改变数字采样率,采用先进行插值后进行抽取,可以避免造成频率混叠。抽取时原始信号的频谱被周期拓展,如果原始信号最高频率大于抽取之后采样率的50% 就会发生混叠。插值也会让频谱周期拓展,但由于输出信号点数增多,所以频率分量只是周期存在,不会发生混叠。为此,无论是抽取还是插值,后面都需要进行1 次数字滤波。根据插值、抽取等效变换,可以节省1 个重采样滤波器。

其插值原理如下:

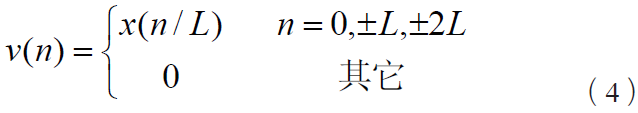

即,插值后的序列v(n) 时域表达式为:

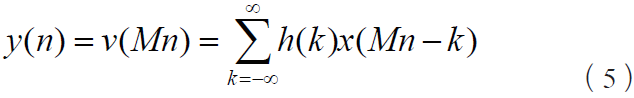

其抽取原理如下:

此时,滤波器h(n) 既充当了前一级插值后的镜像频率抑制,又充当后一级抽取滤波器的抗混叠频率分量,两者合二为一,节省FPGA 资源。同时,由于插值因子L和抽取因子M 可以为任意整数,因此,该原理已经可以实现任意分数倍抽取滤波,而且其Fir 滤波器的归一化截止频率为:

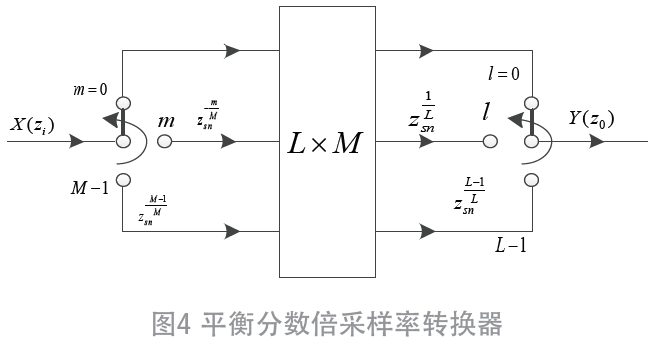

1.3 基于FPGA分数倍抽取实现方案

根据以往所掌握的知识和技术,基于直接型数字滤波器的采样率转换器尽管可显著降低运算复杂度,但由于其具有以较高的采样率对延时状态变量寄存器进行控制,导致插值运算器中必须用较高的运算频率,增加FPGA 的功耗同时也带来电路的不稳定。为解决这一难题,我们采用改进的S/P 和P/S 转换器构建FPGA 的多项数字滤波架构。具体架构图如图4 所示。

该转换器(数字滤波器)具有如下特点:

● 全部与零的加法、乘法全部省略;

● 系统运算都是以低于输入或输出采样率进行计算;

● 全部信号处理采用块运算架构;

● 数据计算潜伏时间最小。

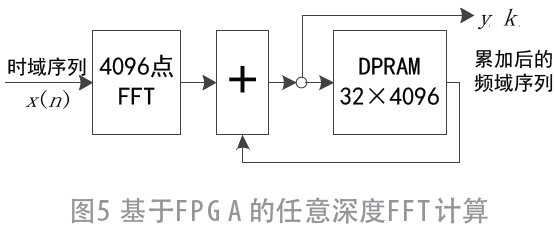

1.4 任意深度FFT实现方案

在接收5G 毫米波大带宽信号时,假如需要分析100 MHz 带宽信号,输入序列长度为10 ms,那么其IQ数据样点数为:

122.88 MHz × 10 000μs = 1 228 800 (7)

即5G NR 的100 MHz 带宽信号在标称采样率122.88 MHz 下,序列长度1 228 800 远大于FPGA 内部Xilinx 等可编程逻辑厂商典型FFT IP 核的65 536 限值。

而在新型频域信号分析时,接收机有必要处理任意长度FFT(一般指2μ),假如不采用现成的FFT IP 核,就需要自己编写FFT,不但耗时且稳定性和资源消耗比会很差,因此就需要运用Weltch 算法思想,把需要分析的长序列进行分解,一般根据测试指标要求,先计算出频谱分辨率,例如100 MHz 的NR 信号的ACLR 中经常需要频率分辨率达到30 kHz,则其需要最小FFT 处理深度为:

122.88×1 000 ÷ 30 = 4 096 (8)

也就是说,4 096 点深度的FFT 在122.88 MHz 采样率下的频率分辨率已经可以达到30 kHz。此时,传统FFT深度已经固定在4 096 点了,可以连续处理4 096 个时域样点。

4096 ÷122.88 = 33.33 (9)

式(9)表示,时域一次性处理4 096 点IQ 数据需要消耗33.33 μs,即300 次循环4 096 次FFT 处理数据长度才能达到一个5G 无线帧长度(10 ms)。具体FPGA 实现方案如图5 所示。

2 测试结果

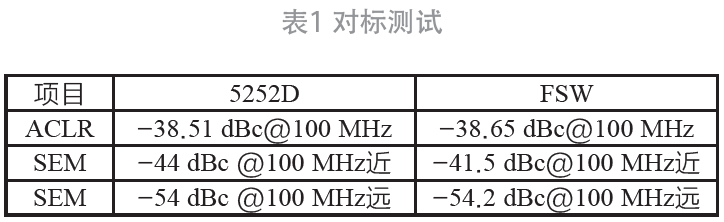

基于5252D 基站测试仪硬件平台进行数据采集处理,对比测试仪器R&S FSW 宽带矢量信号分析仪。

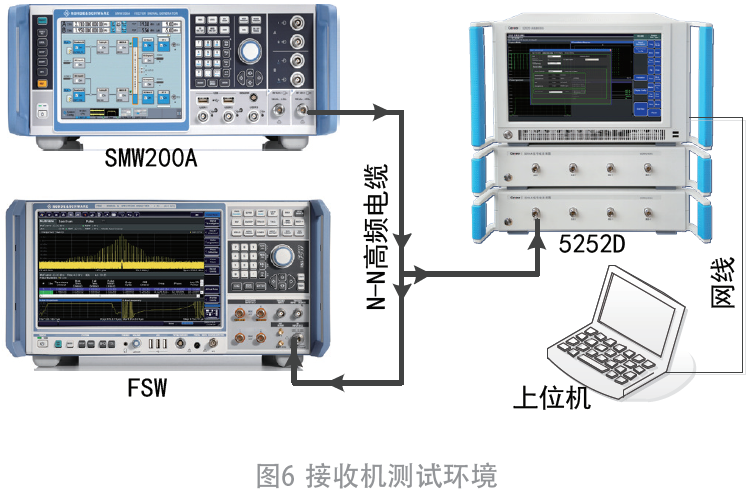

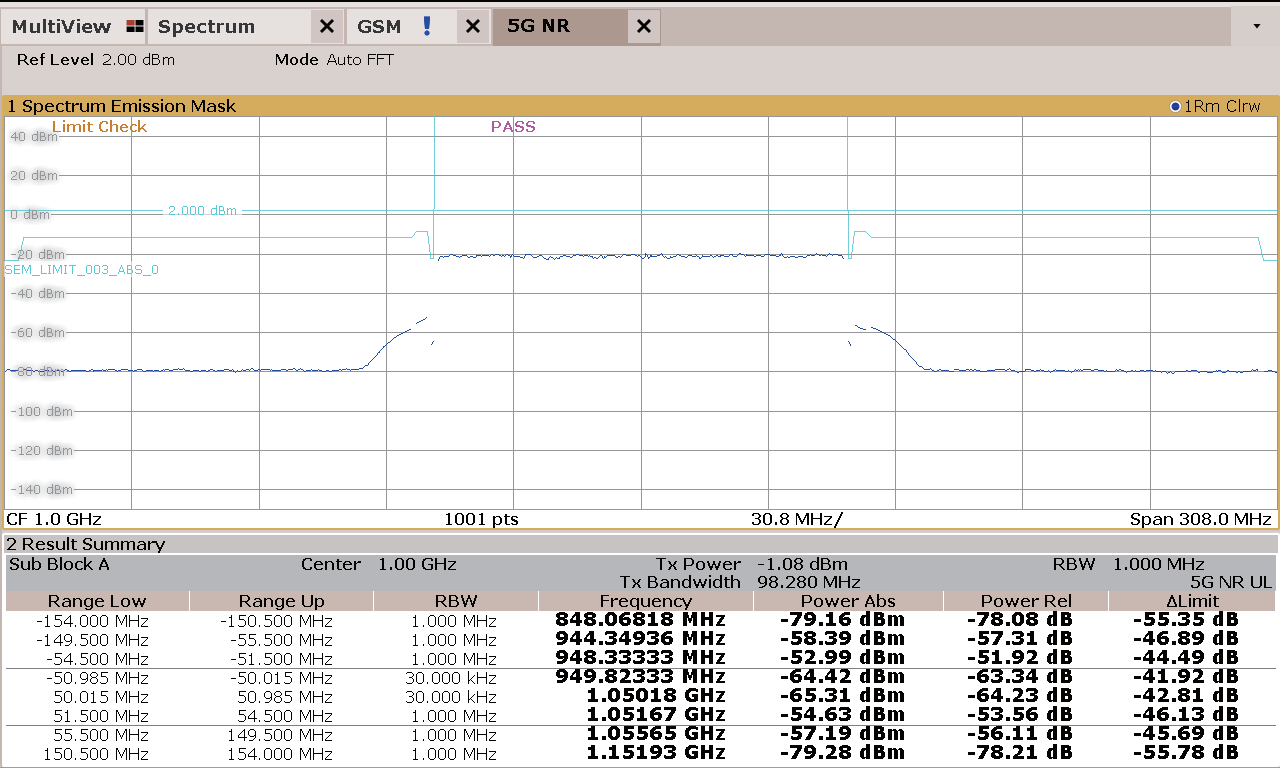

FSW 为对标仪器,验证本文的方案可行性,图6为测试验证环境,对ACLR、SEM 等核心5G 接收指标进行测试。

表1 表示5252D 基站测试仪硬件平台和FSW 宽带矢量信号分析仪在ACLR 和SEM 等技术指标的对比测试。

图9 为构建的毫米波接收机测试验证环境,激励信号源为R&S SMW200A 矢量信号发生器,该仪表最高支持频率44 GHz 毫米波频段,带宽2 GHz。测试时SMW200A 发送5G NR PDSCH 信号,5252D 和FSW 同时进行ACLR 和SEM 指标测试。

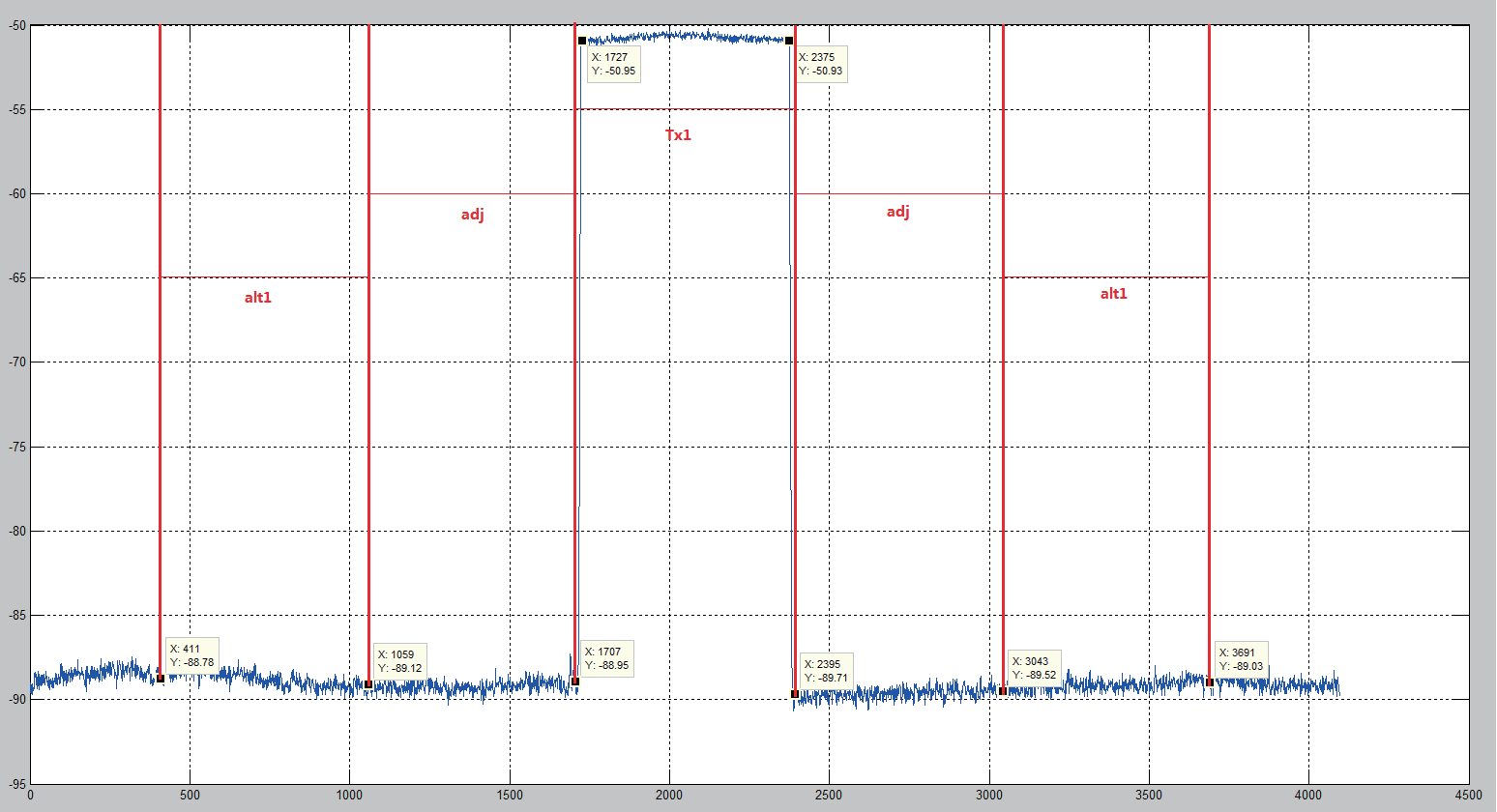

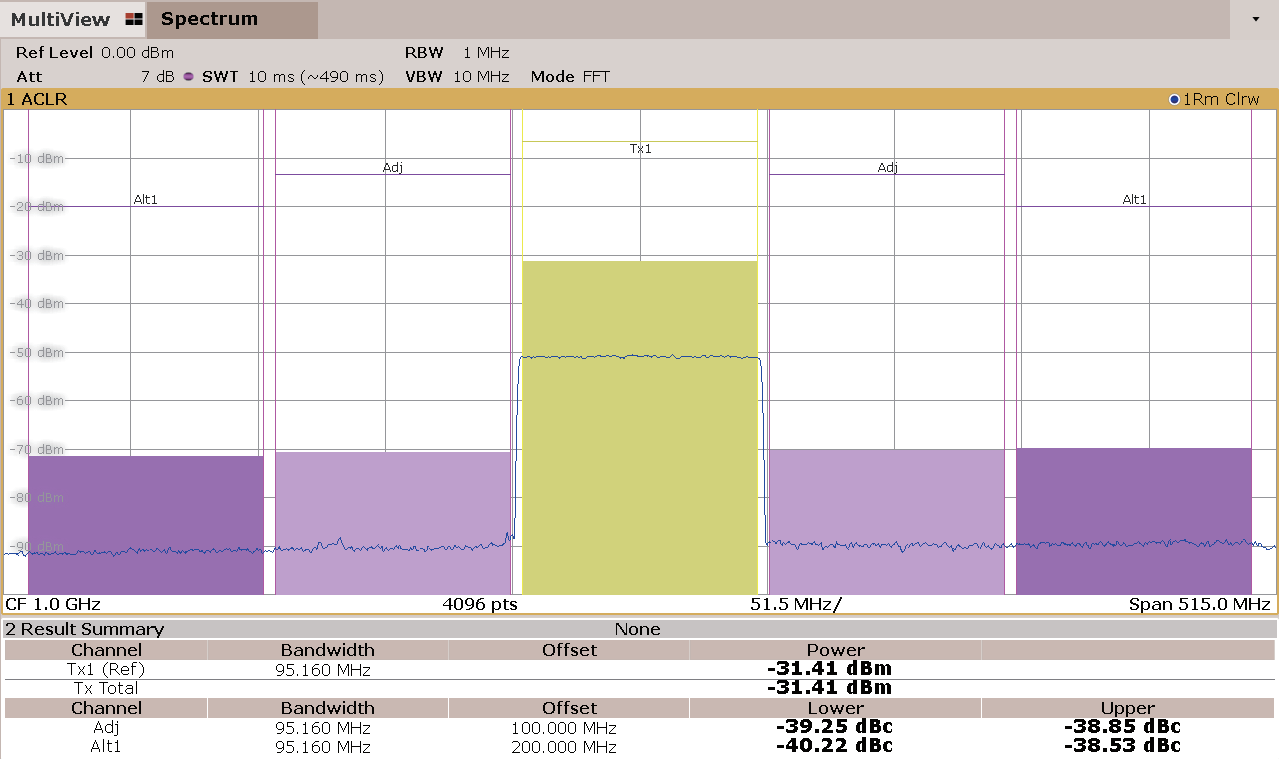

图7、图8 分别为5252D 和FSW 在5G NR PDSCH100 MHz 信号信道带宽ACLR 测试准确度的对比。

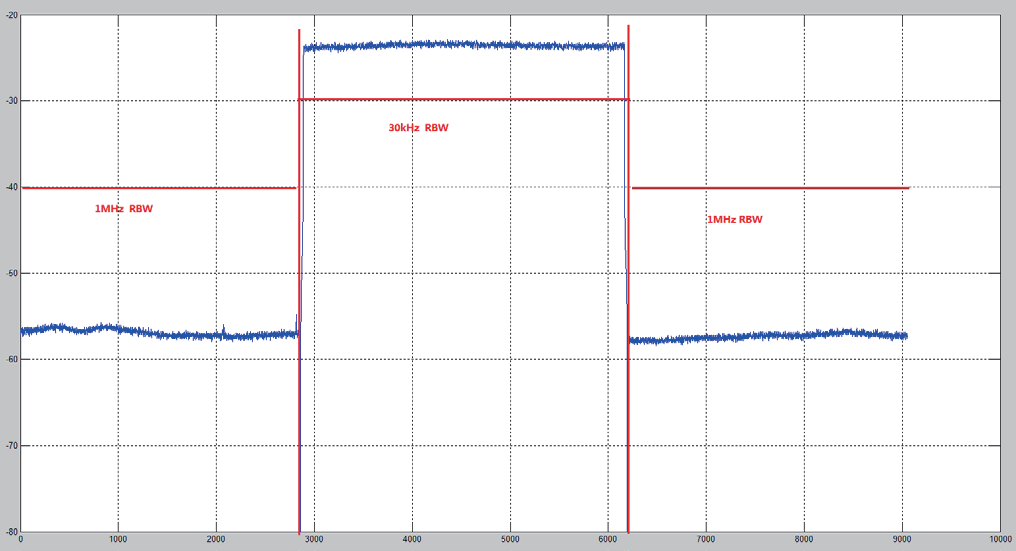

图9 为5252D 的频域SEM 计算数据实测结果(含全扫宽)与图10 FSW 实测结果在5G NR PUSCH100 MHz 信号信道带宽SEM 测试准确度的对比。

图7 5252D接收机ACLR实测结果

图8 FSW接收机ACLR实测结果

图9 5252D接收机SEM实测结果(全扫宽)

图10 FSW接收机SEM实测结果

3 结束语

电路方案设计基于多速率采样原理、多速率信号重采样原理、FPGA 平台分数倍抽取方案和任意深度FFT处理方案,采用多相并行FPGA 滤波数字信号处理技术和改进的基带FPGA 逻辑电路,基于大带宽、高采样率A/D 和高性能FPGA 芯片,设计一款满足毫米波5G 接收机的功能信号分析装置,为研制提供了一种崭新的可

实施方案。

参考文献:

[1] 白宝明,马啸,陈文,等.面向B5G/6G的信息传输与接入技术专题序言[J].西安电子科技大学学报,2020,47(6):1-4.

[2] 张黎明.毫米波5G NR信号OFDM技术研究与实现[J].电子测量技术,2020,43(22):146-149.

[3] 李恩琦,龚小竞, 朱卫华,等.基于FPGA的分数倍抽取滤波器的改进设计与应用[J].南华大学学报(自然科学版),2020,34(1):52-59.

[4] 都赟赟,程敏敏,卢圣龙等.基于FPGA的毫米波数据传输系统的实现[J].通信技术,2020,53(7):1645-1651.

[5] 黄世锋,陈章友,张兰等.多通道雷达数字接收机数字下变频设计[J].电子技术应用,2016,42(6):46-48;55.

[6] 刘晟.数字变频链路中多采样率滤波器研究[J].通信技术,2019,52(9) :2081-2086.

[7] 李飞,冯晓东,李华会,等.可变带宽数字下变频的设计与FPGA实现[J].电子技术应用,2016,42(4):35-38.

[8] 谢海霞,孙志雄.多速率信号处理系统设计与实现[J].电子设计工程,2018,26(18):132-135.

(本文来源于《电子产品世界》杂志2021年5月期)

评论