一种非对称双向可控硅静电防护器件的设计*

*基金项目: 国家自然科学基金青年基金项目(61704145),湖南省自科青年基金项目(2019JJ50609)

本文引用地址:https://www.eepw.com.cn/article/202107/427152.htm作者简介:通信作者:汪洋,wangyang@xtu.edu.cn。

李炜峰 (1999—),男(汉族),湖南娄底人,在读本科生,研究方向集成电路ESD防护。

0 引言

随着集成电路工艺的不断发展和复杂程度的提高,静电防护的要求和需求越来越大。在许多静电保护(ESD)器件结构中,可控硅结构(silicon controlled rectifier,SCR)由于拥有较强的鲁棒性,较小的寄生电容和深回滞曲线被广泛应用于集成电路的静电防护[1],但SCR 的深回滞特性也带来了维持电压低的缺点。一般提高维持电压的方法是通过加入浮空P+ 增长泄放路径的长度[2]、通过内镶二极管,或者增加N+ 与P+ 对形成寄生分流二极管来实现[3]。

双向可控硅(dual directional silicon-controlled rectifier,DDSCR)是为满足器件不论是从阳极到阴极的正向路径,还是阴极到阳极的反向路径都能工作而设计的[4-5]。而一般的器件都会带有保护环结构以避免与其他器件产生寄生结构,但这就会使原有的DDSCR 与保护环形成寄生结构,使正反向I-V 曲线不对称。为了消除寄生结构的影响,传统ADDSCR(Asymmetrical dual directional silicon-controlled rectifier)的结构被提出[6]。但传统ADDSCR 的维持电压较低,需要优化器件来提高其维持电压。

本文提出的非对称双向可控硅静电保护器件基于0.18 μm BCD 工艺,利用电极短接相连的两对注入区,在正向和反向电流路径上都形成分流寄生晶体管,减小相应阱电阻电流,减弱器件的正反馈效应,提高器件的维持电压;同时浮空P+ 的加入,提高了基区浓度,使SCR 路径的晶体管放大倍数降低,从而使走埋层的路径为主要路径,进一步提高了维持电压。最后采用TCAD器件仿真工具,对新器件工作原理和预期参数指标进行验证。

1 传统ADDSCR结构与工作原理

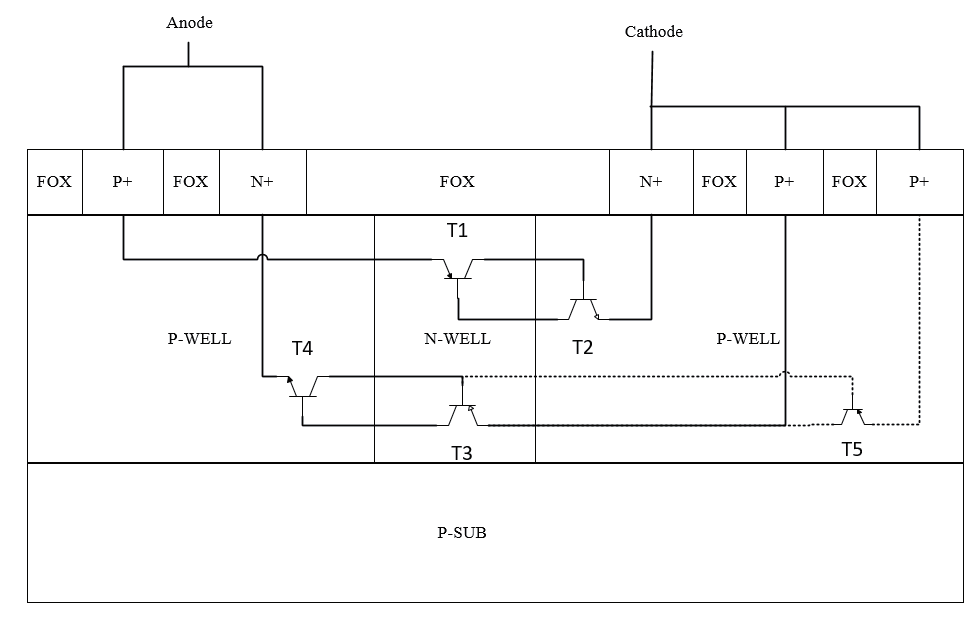

当考虑保护环时,若普通对称型DDSCR 阴极承受ESD 应力,由于保护环也与阴极相连,故产生的ESD电流路径与正向路径不同,ESD 电流会经由保护环的P+ 掺杂区流向阳极,如图1 所示,虚线部分连接的寄生三极管T5 就产生了分流的作用,最终导致该器件正反向路径不同,故正反向I-V 曲线亦不对称。

传统ADDSCR 在普通对称型DDSCR 的基础上加入了N+ 浮空掺杂区[7],且改变了原有PNNP 的注入区形式,改为PNPN 注入区形式,其作用是使在考虑了保护环寄生结构后,直接利用保护环形成反向路径,避免反向ESD 电流被保护环分流,使正反向I-V 曲线对称[4]。

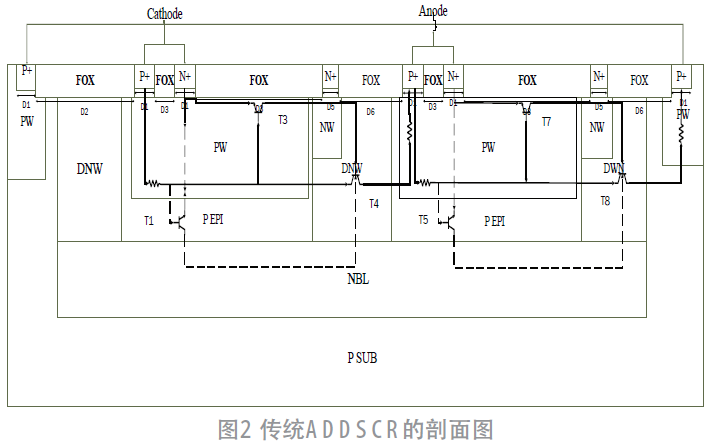

普通DDSCR 的剖面如图1 所示,传统ADDSCR的剖面图及其等效电路如图2 所示。

图1 普通DDSCR的剖面图

如图2 所示,正反向路径的结构相同,其中正向路径由寄生晶体管T1、T3 和T4 组成,反向路径由寄生晶体管T5、T7 和T8 组成。当ESD 为正向脉冲时,正向路径导通;当ESD 为反向脉冲时,反向路径导通。PW 和P 外延层共同组成了SCR 路径中寄生晶体管T3与T7 的基极。当阳极受到正的ESD应力时,随着电压不断增大,P 外延层与NW 间形成的反偏PN 结发生雪崩击穿,由此产生大量的电子空穴对,当RPW 与RNW 上的压降达到0.7 V左右时,SCR 导通,此为SCR 路径,且N+ 浮空掺杂区可影响NW 区的浓度,减小开启电压。

正反向路径中走埋层路径的结构也相同,分别由一个纵向的寄生晶体管T1 与T5 构成。

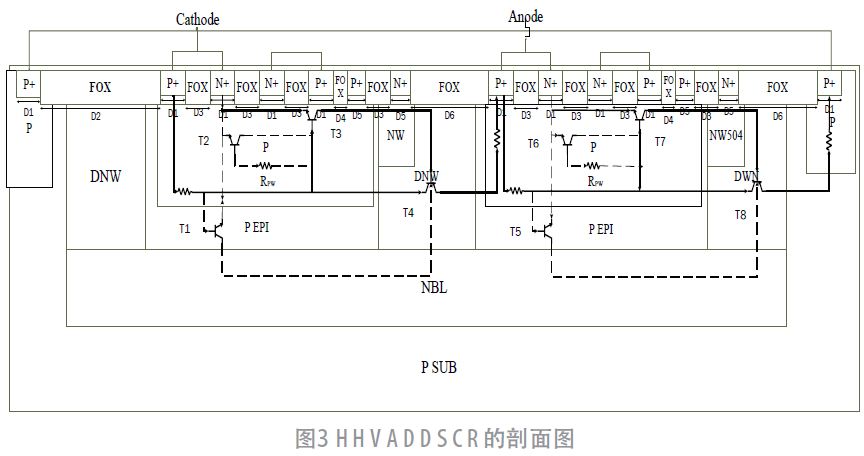

2 HHVADDSCR结构和工作原理

图3 所示为HHVADDSCR( high holding voltage ADDSCR )的结构剖面图。与传统ADDSCR 不同的是,在原有结构的两个PW 中分别加入一对短接的P+和N+ 注入区以及一个P+ 注入区。正反向路径都由1 条SCR 路径和1 条走埋层的路径构成。对于正向路径,SCR 路径的支路由1 个横向PNP 型三极管T4、1 个横向NPN 型三极管T3 和1 个横向寄生分流NPN 型三极管T2 构成;埋层的支路由1个纵向NPN 型三极管T1 构成。对于反向路径,SCR 路径的支路由1 个横向PNP 型三极管T8、1 个横向NPN型三极管T7 和1 个横向寄生分流NPN 型三极管T6 构成;埋层的支路由1 个纵向NPN 型三极管T5 构成。浮空P+ 的加入提高了基区即P 阱的浓度,同时拓展了基区的宽度,这样,SCR 路径的晶体管放大倍数降低,从而使走埋层的路径为主要路径,而走埋层的路径比SCR 路径更长,路径上的电阻更大,使得器件具有更高的维持电压。

增加的两对N+ 与P+ 的电极短接注入区会在正向和反向电流路径上都形成分流寄生晶体管,分别为T2和T6,减小对应阱电阻RPW 电流,减弱SCR 的正反馈效应,提高器件的维持电压,同时由于寄生晶体管T2的分流作用,进一步减小了SCR 路径的电流,更加确保埋层路径成为主要的泄放路径,而且拓展了基区宽度,进一步提高了维持电压。

从上述原理分析来看,HHVADDSCR 克服了传统ADDSCR 维持电压较低的缺点,避免了闩锁。

3 TCAD仿真与分析

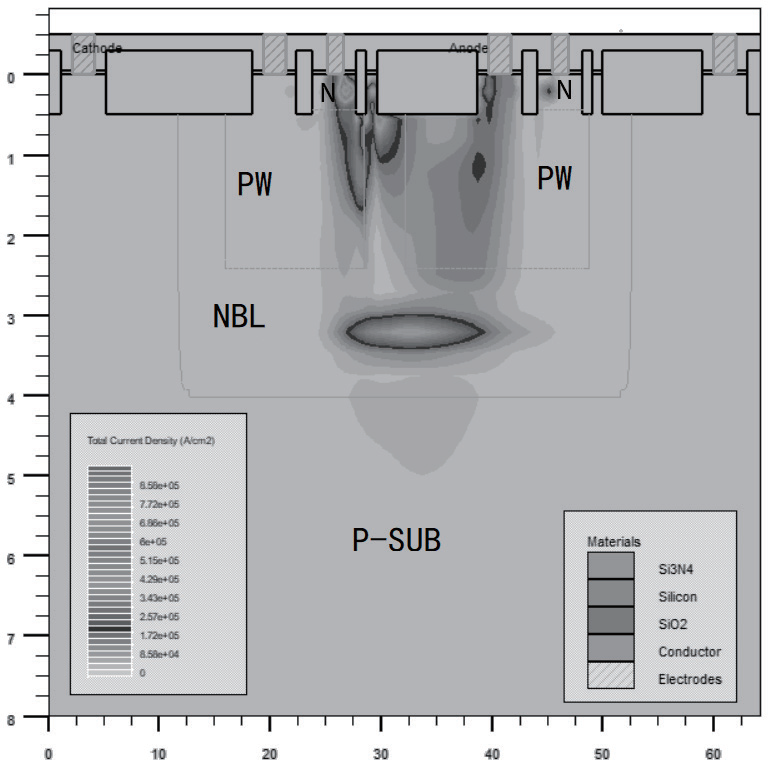

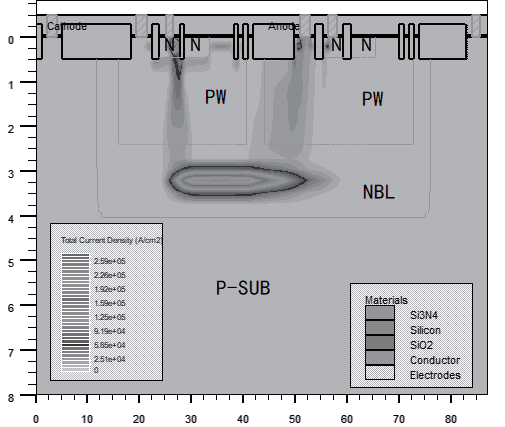

本文采用Silvaco TCAD 进行器件仿真分析,估计器件维持电压和触发电压,仿真时加在器件两端的电流采用从(0~1)mA 等时间间隔取样,得到I-V 特性曲线。TCAD 模拟当ESD 脉冲到达时,传统ADDSCR 的电荷密度图如图4 所示,HHVADDSCR 的电荷密度图如图5所示。

图4 传统ADDSCR的电荷密度图

图5 HHVADDSCR的电荷密度图

仿真结果表明,HHVADDSCR 的电流泄放的主要路径为走埋层路径,且用于分流的寄生晶体管起到了分流作用,与前面的理论分析相符,走埋层的路径成为了主要的电流泄放路径。

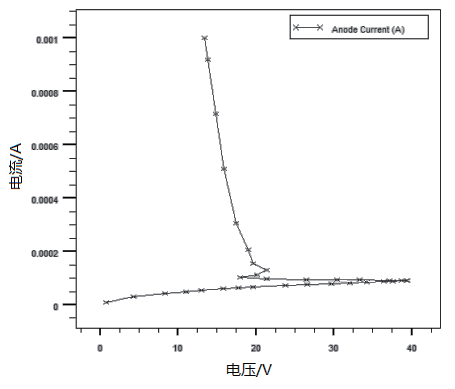

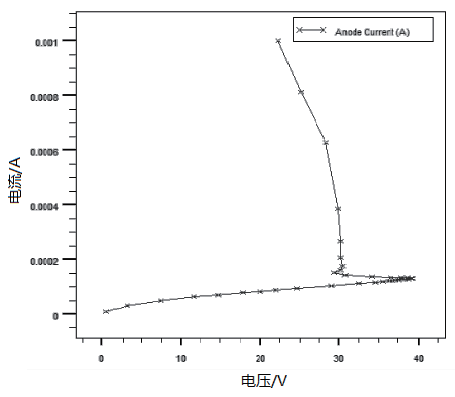

经TCAD 仿真,在相同的电流边界条件下,传统ADDSCR 的I-V 特性曲线如图6 所示,HHVADDSCR的I-V 特性曲线如图7 所示。

图6 传统ADDSCR的I-V特性曲线图

图7 HHVADDSCR的I-V特性曲线图

仿真结果表明,当电流增加到100 mA 时,I-V 曲线已出现2 个拐点,第1 个拐点为第1 次击穿电压点,第2 个拐点为箝位电压点,用这2 个点来分别估计触发电压和维持电压,则传统ADDSCR 的触发电压大约为39.5 V,维持电压大约为18 V;HHVADDSCR 的触发电压大约为39.2 V, 维持电压大约为29.4 V。则HHVADDSCR 的触发电压与传统ADDSCR 基本相同,维持电压得到了提升。

4 结束语

本文提出了一种高维持电压的HHVADDSCR,通过浮空P+ 的加入,提高了基区即P 阱浓度,使SCR 路径的晶体管放大倍数降低,从而使走埋层的路径为主要路径,而走埋层的路径比SCR 路径更长,路径上的电阻更大,使得器件具有更高的维持电压;通过加入电极短接相连的两对注入区,在正向和反向电流路径上都形成了分流寄生晶体管,减小相应阱电阻的电流,减弱SCR 的正反馈效应,提高器件的维持电压,同时由于寄生晶体管分流,进一步减小了SCR 路径的电流,使走埋层的路径变为主要路径,进一步提高了维持电压。通过提高维持电压,使得本器件能够应运于ESD保护设计,使其维持电压高于内部芯片的工作电压,有效地保护了内部芯片,远离闩锁的风险。

参考文献:

[1] 韩燕,董树荣.集成电路ESD防护设计理论、方法与实践 [M].北京:科学出版社,2014:51-54.

[2] CHEN X,WANG Y,JIN X,et al.An ESD robust high holding voltage dual-direction SCR with symmetrical I-V curve by inserting a floating P+ in PWell [J].Solid State Electronics,2019,160:107-627.

[3] HUANG X,LIU Z,FAN L,et al.High holding voltage SCR with Shunt-transistors to avoid the latch-up effect[C].2016 IEEE International Nanoelectronics Conference,2016.

[4] KER M,HSU K.Overview of on-chip electrostatic discharge protection design with SCR-based devices in CMOS integrated circuits[J].IEEE Trans Device Mater Reliab June 2005,5(2):235-49.

[5] ZHAN C R,BESSE P,LAINE J,et al.High-Performance bi-directional SCR developed on a 0.13um SOI-based smart power technology for automotive applications[C].39th Electrical Overstress/Electrostatic Discharge Symposium (EOS/ESD).Tucson,AZ 2017;2017:1–7.

[ 6 ] ZHAN C R , G I L L C, H ONG C, e t a l . H i g h - v o l t a g e asymmetrical bi-directional device for system-level ESD protection of automotive applications on a BiCMOS technology[C].2013 35th Electrical Overstress/Electrostatic Discharge Symposium.Las Vegas,NV,2013:1-8.

[7] KO J,KIM H,JEON J.Gate bounded diode triggered high holding voltage SCR clamp for on-chip ESD protection in HV ICs [C].Electrical Overstress/Electrostatic Discharge Symposium.Las Vegas,NV 2013;2013:1–8.

(本文来源于《电子产品世界》杂志2021年7月期)

评论