嵌入式时钟管理器的设计与实现

目前,在嵌入式产品的研发中,低档微处理器软件多采用裸机开发模式实现。在这种开发模式中,常有如下需求:

本文引用地址:https://www.eepw.com.cn/article/201809/388832.htm(1) 在经历特定的时间段后,执行特定操作;

(2) 根据给定周期执行特定操作。

传统的作法是利用前后台方式:设定硬件定时器,使其在后台以特定周期对各相关操作的标志变量作计数操作;前台则不断对各标志变量巡回查询,若发现标志变量达到预定值,则执行特定操作。可见,上述需求需直接操作硬件定时器实现,其过程繁琐,且需要用户对相关硬件有深入了解。因此,本文设计、实现了一种使用方便的低端系统时钟管理器。

本时钟管理器适用于可提供至少一个硬件定时器的处理器。其为用户提供了有益、友好的裁剪途径,以满足不同目标系统的实际需要。通过裁剪,该时钟管理器的目标代码最小可至100B以下,最大也不超过1KB。

时钟管理器在实现中,将与硬件密切相关的部分组成一独立模块(文件)。针对不同的目标系统处理器,更换该模块即可。为使表述不过抽象,本文以8051系列单片机为目标系统处理器、C51为工具语言阐述该嵌入式时钟管理器的设计与实现。

1 设计

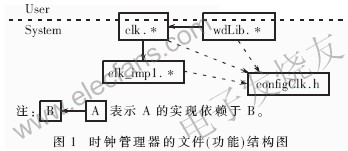

该时钟管理器模块(文件)结构如图1所示。

(1) configClk.h定义了有关系统裁剪、配置的可调参数,通过对configClk.h中相关宏参数的配置,即可实现对该时钟管理器系统的配置和裁剪。

(2) clk_impl.*功能模块用来封装目标系统的一个硬件定时器,以屏蔽不同处理器间的硬件差异,起到HAL(HardwareAbstractLayer)作用。系统时钟在此构建。

(3) clk.*模块在clk_impl.*提供的HAL基础上进一步封装,通过一个钩子(Hook)函数,为系统提供时钟脉冲,且脉冲宽度可调(配置configClk.h中的相关宏参即可)。

(4) WdLib.*模块为用户应用提供多个软件定时器。

2 实现

2.1硬件定时器的底层封装

硬件定时器底层封装在图1所示的clk_impl.*中实现。其中定义了一个初始化接口函数和一个定时器中断的ISR(InterruptServiceRoutine)。令选用的硬件时钟为定时器0(可在configClk.h中配置)。

(1) 初始化接口函数void_clkInit(void){}

用户通过调用该接口函数,可周期性地执行相应的ISR—clkTick_ISR,从而形成逻辑上的系统时钟。另外,本接口函数不为用户直接访问,而在上层模块clk.*中被调用。

(2) 定时器0的ISR—clkTick_ISR

voidclkTick_ISR(void)interrupt1usingREG_GRP_FOR_

SYS_CLK{}

其中:REG_GRP_FOR_SYS_CLK为定义于configClk.h中的可调参数,用来设定本ISR的工作寄存器组。

评论